当前位置:网站首页>FPGA开发第二弹:流水灯实验

FPGA开发第二弹:流水灯实验

2022-08-07 06:57:00 【WeeHours.】

FPGA开发第二弹:流水灯实验

流水灯的原理是开发板上的四盏灯交替亮起,按顺序循环往复产生流水的现象。

LED灯硬件原理图如下所示:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存失败,源站可能有防盗链机制,建议将图片保存下来直接上传下上传(i94S7GpVYvqZ-1659582399078)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803144605337.png)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803144605337.png)]](/img/27/9e30a5fb1fe610e77f0f15b546313d.png)

实验中的系统时钟、按键复位以及LED端口的管脚分配如下表所示。

对应的XDC约束语句如下所示:

create_clock -name clk -period 20 [get_ports clk]

set_property -dict {PACKAGE_PIN R4 IOSTANDARD LVCMOS33} [get_ports clk]

set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports rst]

set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports led[0]]

set_property -dict {PACKAGE_PIN R3 IOSTANDARD LVCMOS33} [get_ports led[1]]

set_property -dict {PACKAGE_PIN V2 IOSTANDARD LVCMOS33} [get_ports led[2]]

set_property -dict {PACKAGE_PIN Y2 IOSTANDARD LVCMOS33} [get_ports led[3]]

流水灯模块原理图如下图所示:

由于人眼的视觉暂留,流水灯状态变化间隔时间不能低于0.1s,否则的话实验效果就不明显。本实验我们设置流水灯间隔为0.2s一次,我们使用计数器累加计数来计时,计时达0.2s后计数器清零并重新开始计数,每0.2s就能让led的状态改变一次。

流水灯模块代码如下:

module flow_led(

input clk,

input rst,

output reg [3:0] led

);//定义输入端口时钟和清零,输出端口即LED

reg[23:0] counter;//定义一个计数器

always @(posedge clk or negedge rst)

begin

if(rst==0)

count<=24'd0;//根据计数的值进行规定位数

else if(counter<24'd1000_0000)//最多记到0.2s,这个是次数一个时钟周期设置为20ns

counter<=counter+1'b1;

else

counter<=24'd0;

end

[email protected](posedge clk or negedge rst)

begin

if(rst==0)//清零信号

led<=4'b0001;

else if(counter==24'd1000_0000)

led[3:0]<={led[2:0],led[3]};//0.2s变一次

else

led<=led;//其他时间保持不变

end

endmodule

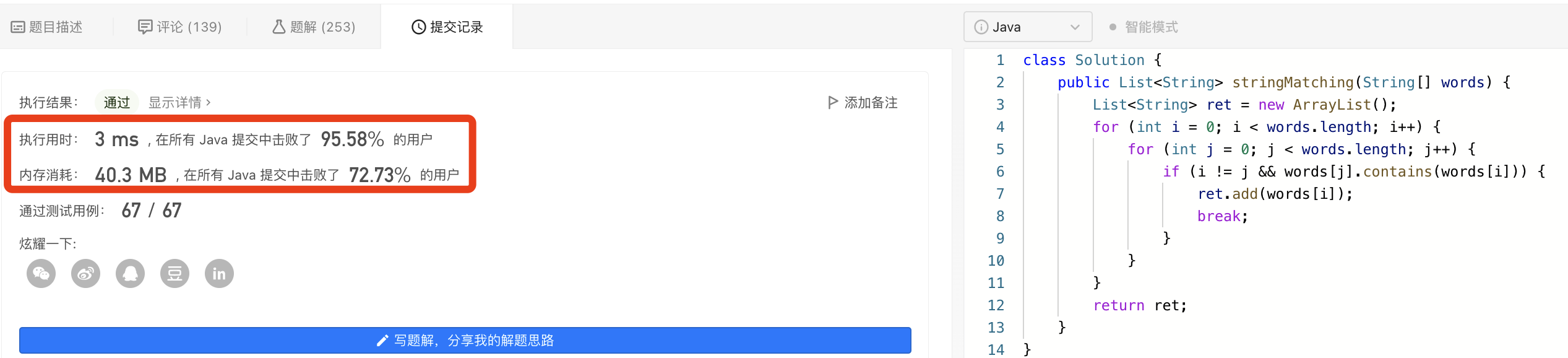

测试代码testbench如下:

`timescale 1ns/1ns

module test();

parameter T=20;//一个时间周期

reg clk;

reg rst;

wire [3:0] led;

initial

begin

clk=1'b0;

rst=1'b0;

#(T+1) rst=1'b1;

end

always #(T/2) clk=~clk;//半个时间周期翻转

flow_led lh(

.clk(clk),

.rst(rst),

.led(led)

);

endmodule

仿真结果如下图所示:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-8ZdfpUAw-1659582399083)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803145937047.png)]](/img/98/be5c5ccc22672dd6606fc228b66ebb.png)

最后下载验证,生成比特流,在FPGA开发板上进行开发。

具体操作可以参考FPGA开发第一弹:FPGA开发第一弹:Vivado软件安装、开发使用与工程建立_WeeHours.的博客-CSDN博客_vivado 设置顶层

以上就是我进行的流水灯实验,继续熟悉整个FPGA开发的流程,如果自己做的项目的话其实每一步基本都不能缺失,每一步都需要我们认真总结掌握,多练几次也就熟练了!欢迎大家私信我一同交流学习,也欢迎大家批评指正!

边栏推荐

- LeetCode刷题笔记:899.有序队列

- 传输层(UDP协议,TCP协议三次握手、四次挥手)

- 一些零碎知识点的索引

- 10 years of experience summary: 7 tools for data analysts, focus on causal analysis!

- inux安装软件命令yum,apt-get

- Actionformer: Localizing moments of actions with transformers 论文阅读笔记

- 【问题记录】一次由filter引发的血案,如何定位上游链路的问题,问题排查与定位思路分享

- LeetCode 1408. String matching in arrays

- LeetCode 628. Maximum Product of Three Numbers

- 神经网络ppt不足之处怎么写,神经网络ppt免费下载

猜你喜欢

VoLTE Basic Self-Learning Series | What are transparent data and non-transparent data in VoLTE?

神经元细胞属于什么细胞,人体有多少神经元细胞

cron expression

LeetCode 628. Maximum Product of Three Numbers

spyder/conda安装包报错:conda info could not be constructed. KeyError: ‘pkgs_dirs‘

This beta version of Typora is expired

LeetCode 剑指 Offer 06. 从尾到头打印链表

图解LeetCode——1408. 数组中的字符串匹配(难度:简单)

CTO强烈禁止使用Calendar,那用啥?

Vitalik详解5种类型的ZK-EVM

随机推荐

MySQL - 索引优化

LeetCode 剑指 Offer 30. 包含min函数的栈

好消息|Erda 加入中国开源社区 landscape

ROS接收颜色点云并转换为图像和颜色点云

VoLTE Basic Self-Learning Series | What are transparent data and non-transparent data in VoLTE?

VoLTE Basic Self-study Series | Summary

HyperBDR云容灾深度解析二:自研Boot in Cloud技术,实现高度自动化云容灾

用户登录模块---Druid+JDBC+Servlet

cron 表达式

VoLTE Basic Self-Learning Series | The relationship between IMS, VOIP, VoLTE, and RCS?

VoLTE Basic Self-Learning Series | Enterprise Voice Network Brief

微信小程序--》小程序全局配置和详解下拉刷新和上拉触底页面事件

VoLTE基础自学系列 | VoLTE终端哪些场景会触发CSFB?

服务端获取用户ip

【Promise】Promise 使用 / 回调地狱问题 async-await /宏队列与微队列

leetcode 110. Balanced Binary Trees

VoLTE基础自学系列 | 什么是VoLTE中的Silent Redial?它和CSFB什么关系?

grid grid layout

OS模块中获取当前文件的绝对路径的相关方法

LeetCode 1163. The last substring lexicographically