当前位置:网站首页>Why should Latches be avoided in digital IC design?

Why should Latches be avoided in digital IC design?

2022-08-08 06:12:00 【Pippi width】

Why Latches should be avoided in digital IC design

When I was in school, the teacher said that the judgment statement should write all the conditions, otherwise a latch would be generated. When working on the project, he said that the assignment of multi-bit register signals must add an if condition to prevent the assignment of else.It is very contradictory. This article mainly talks about what a latch is, under what circumstances a latch occurs, and the harm of a latch

Article table of contents

I. What is a latch?

Latch is a memory cell circuit that is sensitive to pulse level, and they can change state under the action of a specific input pulse level [1].In other words, if a module's input information will be updated to its output pins only under the action of a specific level, otherwise the output of the module will remain unchanged, then this module can be regarded as aLatches.

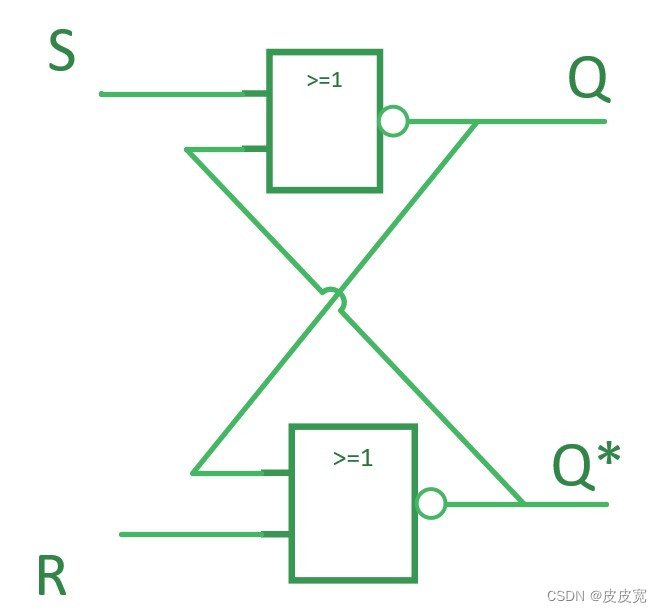

The structure of a common S-R register is as follows:

The truth table is

| S | R | Q |

|---|---|---|

| 0 | 0 | Keep |

| 1 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 1 | Flip |

When S and R are 00, the output Q can be kept unchanged, so as to achieve the purpose of using combinational logic to achieve storage;

Second, under what circumstances does a latch appear?

Sequential logic does not require latches to store data due to the existence of registers; while the conditions of combinational logic are not given full time, a latch will appear;

For example

[email protected](*)if(vld)a = b;At this time, since there is no case where vld is 0, it will not be instantiated as a selector of two alternatives, but a latch will be instantiated to achieve the storage function of keeping data unchanged when vld is 0;

Third, why should latches be avoided?

Latches have the following disadvantages:

- Cannot be reset asynchronously and is in an indeterminate state after power up.

- Latches can complicate static timing analysis;

- If the circuit is built on an FPGA, since the basic unit in the FPGA is composed of a look-up table and flip-flops, more resources are needed to generate latches;

- Latches are sensitive to glitches and will cause circuit instability (I don't understand this, can instantiating a selector solve this problem??)

References

【1】 Latch_360 Encyclopedia (so.com)

【2] CSDN: Causes, Harm and Avoidance of Latch in FPGA Learninghref="https://blog.csdn.net/kuan__/article/details/124392567?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522165959877816782248522021%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=165959877816782248522021&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~first_rank_ecpm_v1~pc_rank_34-9-124392567-null-null.142%5Ev39%5Epc_rank_34_queryrelevant0&utm_term=%E9%94%81%E5%AD%98%E5%99%A8%E5%AF%84%E5%AD%98%E5%99%A8&spm=1018.2226.3001.4187">CSDN: The relationship and difference between latches, D flip-flops and registers

边栏推荐

- 轮播文字! QPainter

- Web Application Vulnerability Assessment with Zap and W3af

- 仿QQ好友列表,QListWidget!

- 121 distributed interview questions and answers

- "Public Administration" exam key points and answers

- The CAP theorem instance analysis

- 什么是 DevOps?看这一篇就够了!

- CAP定理实例分析

- Several postman features worth collecting will help you do more with less!

- Typescript namespace

猜你喜欢

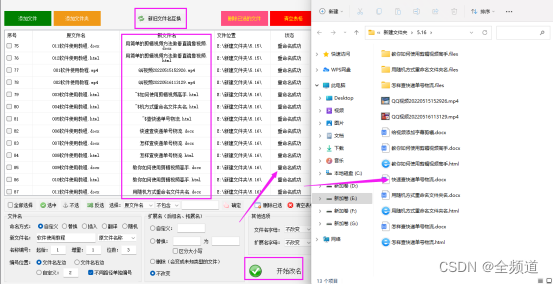

How to batch import files and rename them all to the same file name

Leetcode sword 】 refers to the Offer (special commando) summary

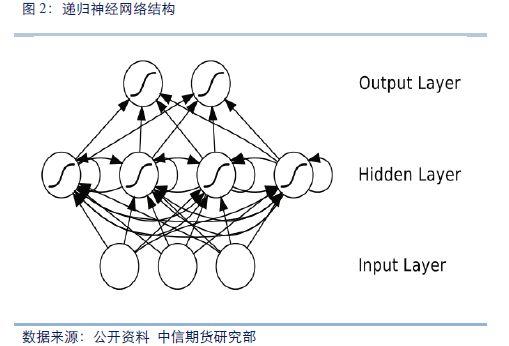

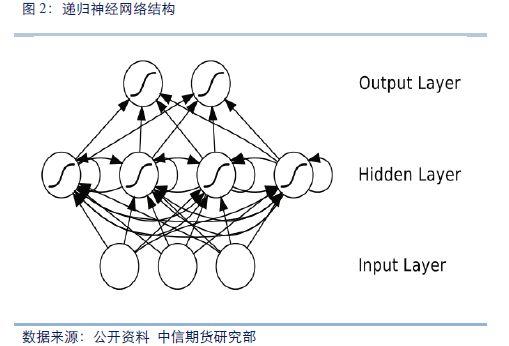

神经网络一般训练多少次,神经网络训练时间过长

The pta patching simple graph theory

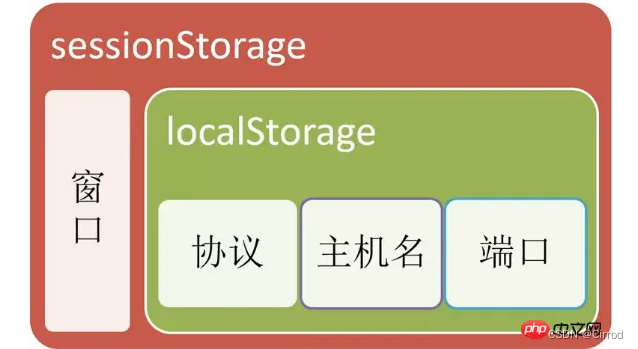

webstorage

Redis set to start automatically at boot

Web 攻击的日志分析:初学者指南

tkinter-TinUI-xml combat (7) PDF paging and merging

How many times the neural network is generally trained, the neural network training time is too long

Summary of digital IC design written test questions (4): some basic knowledge points

随机推荐

Postman显示验证码图片(base64字符串)

Redis set to start automatically at boot

Completed - desktop interactive wizard design based on facial expressions (share the results, attach the data set of facial expressions and the yolov5 model trained by yourself and the interactive int

stack-queue

Runtime——KVC,KVO原理

Web Application Vulnerability Assessment with Zap and W3af

验证的计划

基于FTP协议的文件上传与下载

分页组件的使用

postgres 安装 14 版本出现错误提示解决办法

0 dictionary tree/string medium LeetCode676. Implement a magic dictionary

神经网络参数量和计算量,神经网络是参数模型吗

Educational Codeforces Round 133 (Rated for Div. 2) C Supplement

The CAP theorem instance analysis

The pta patching simple graph theory

【u-boot】u-boot的驱动模型分析

人体神经元细胞分布图片,神经元人体分布大图

Style of DataGrid in wpf

Promise的使用与async/await的使用

文件操作 - IO