当前位置:网站首页>Program download and data extraction using JLINK command line

Program download and data extraction using JLINK command line

2022-04-21 07:12:00 【A code farmer who likes to take notes】

Summary of the future

There is a need to quickly download firmware to the board , Then read the firmware stored in the firmware CRC32 Check the version of the check value , use JFlash It's too slow

Realization way

If the board is H743, stay JLink The installation directory opens the command line 【 In the later stage, it can be realized by writing an upper computer with one key , Very convenient 】

// To configure SWD Interface ,CPU by STM32H743VI, Normal should return JLink Information about successful connection

.\JLink.exe -device STM32H743VI -Speed 4000 -IF SWD

// Connect , If normal, the kernel information should be displayed

connect

// Read back to the specified address 1 individual 32 A value ,8012345 by 16 Bit address ,1 by 1 individual

mem32 8012345 1

// If you need to download firmware to the specified address 0x80012345

loadbin "xxxx.bin" 0x80012345

// hit ? You can see that JLink With the help of the

版权声明

本文为[A code farmer who likes to take notes]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204210613411620.html

边栏推荐

- CISSP认证每日知识点(2022年4月19日)

- C语言模拟进栈出栈,先进先出先进后出共用内存

- 每日网安认证测试题(2022年4月15日)

- stm32mp157 wm8960音频驱动调试笔记

- idea如何打包成war包

- 每日CISSP认证常错题(2022年4月14日)

- GD单片机Keil环境搭建

- How to quickly "liver" high-quality slides? Recommend a latex typesetting artifact

- SQL数据库语法学习笔记

- The random gradient descent method is used to learn the depth network

猜你喜欢

【ThreadX】ThreadX源码阅读计划(一)

Learn SCI paper drawing skills (c)

【SSM整合】1. 基本环境搭建

![[ThreadX] ThreadX source code reading plan (II)](/img/a8/591d22c403563ab47f99d2c009c3e2.png)

[ThreadX] ThreadX source code reading plan (II)

![[threadx] threadx source Reading plan (II)](/img/a8/591d22c403563ab47f99d2c009c3e2.png)

[threadx] threadx source Reading plan (II)

Tensorflow实例3: 验证码图片的识别训练,每张图片有4个字母

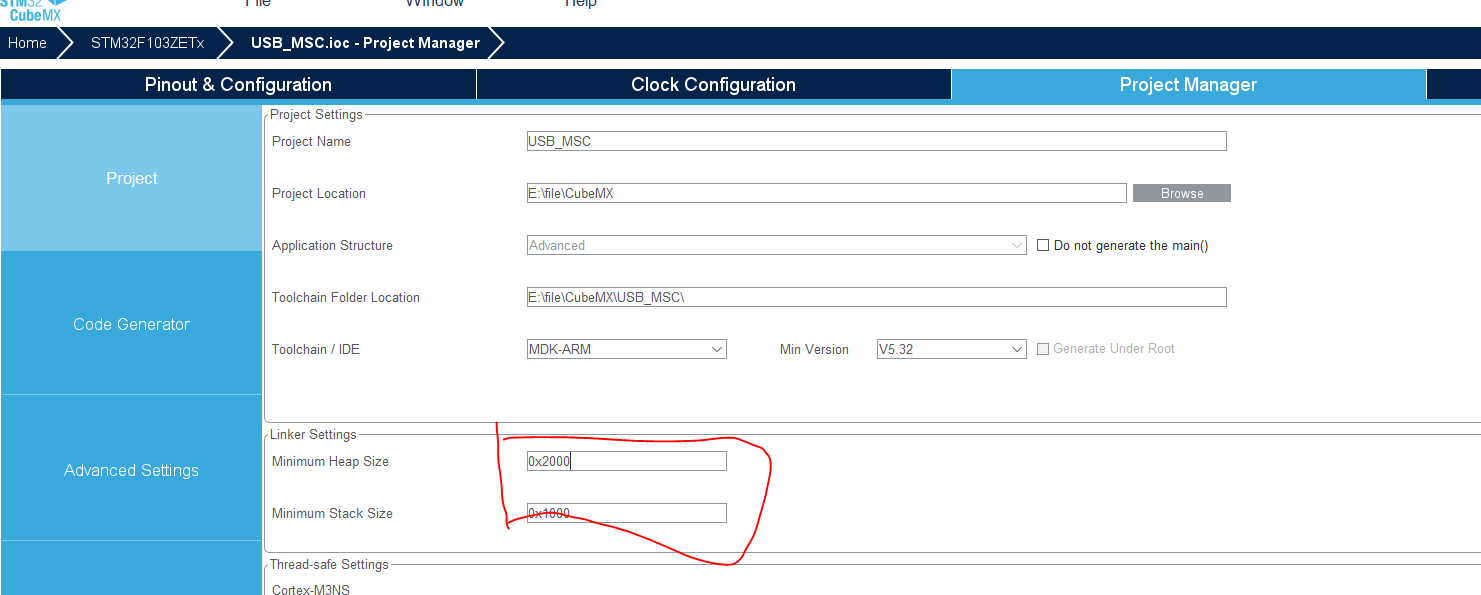

使用STM32cubeMX/STM32cube ide 生成FatFS代码,操作SPI FLASH

![2、 2 [FPGA] development environment construction](/img/7a/e6904f1685d92e4fd716487fb63456.png)

2、 2 [FPGA] development environment construction

【Thread X】NetX Duo PTP校时客户端

![3、 0 [Verilog HDL] first acquaintance with Verilog programming language](/img/bd/6352e3b12f4f4997d5342bbaec2b9a.jpg)

3、 0 [Verilog HDL] first acquaintance with Verilog programming language

随机推荐

Remember some commonly used r packages

Tensorflow基础0:文件的读取与存储

reg文件导入注册表后出现中文乱码的解决方法

canvas 绘制路飞

搭建自己的blog

imx6网口上电后连接不稳定link up,link down

applicationContext.xml变成灰色的文档咋解决

jvm 的 解释执行与 编译执行

每日网安认证测试题(2022年4月13日)

Spark性能优化指南

【SSM整合】4. 逻辑代码编写以及测试

Draw biaxial separation diagram with ggplot2

idea如何打包成war包

Flat (flat lattice transformer) code implementation

每日CISSP认证常错题(2022年4月14日)

Sublime Text3 安装简体中文

Linux启动MySQL报错

CISSP认证每日知识点(2022年4月15日)

QT error: no matching member function for call to ‘connect‘

CANopen使用方法与对象字典主要参数