当前位置:网站首页>FPGA (V) one of RTL codes (cross clock domain design)

FPGA (V) one of RTL codes (cross clock domain design)

2022-04-22 23:45:00 【Jian Chen~】

List of articles

Preface

It's going to be an interview soon , A little flustered !HDLbits The title of has been finished , But I know I'm not enough , Just start with one B standing UP The Lord intercepted a question bank for brushing questions , Only Title , Write your own code , So there may be a problem with the code written , I'm going to divide it into several sections and release the title code . Only for self-study . If you need it, you can also have a look , If there is an error , I would also like to point out that ! thank you !

One 、 asynchronous FIFO

About this part , In my last blog FPGA( Four ) Numbers IC The four basic questions of the interview The second part of the fourth chapter of , There are also codes , The gray code method used .

Two 、 Asynchronous reset, synchronous release

For detailed explanation, please refer to Principle of asynchronous reset and synchronous release

The simple explanation is :

Asynchronous reset , Synchronous release means that when the reset signal arrives, it is not synchronized by the clock signal , It is synchronized by the clock signal when the reset signal is released .

RTL Code as follows :

module Sys_Rst(

input clk ,

input rst_n ,

output sys_rst

);

reg rst_r0;

reg rst_r1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rst_r0 <= 1'b0;

rst_r1 <= 1'b0;

end

else begin

rst_r0 <= 1'b1;

rst_r1 <= rst_r0;

end

end

assign sys_rst = rst_r1;

endmodule

3、 ... and 、 Two level trigger synchronization

The two-stage trigger is generally what we often call two shots , It can effectively reduce the risk of metastable state , As shown below :

RTL Code :

module abit_Pulse(

input clk , // Input clock

input rst_n , // Reset signal

input asynch_in , // Input signal

output synch_out

);

reg [1:0] signal_r;

// In the fast clock domain , Beat the signal twice

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

signal_r <= 2'b00;

else

signal_r <= {

signal_r[0],asynch_in};

end

assign synch_out = signal_r[1];

endmodule

Four 、 handshake CDC Design

FPGA Logic design review (7) Multi bit signal CDC Handshake synchronization of processing mode

A cross clock domain method based on mobile phone holding system and its application Verilog Realization

Handshake refers to a way of communication between two devices , The signal used for communication is the handshake signal . The simplest handshake signal is valid and ready, It can also be called request and grant. Suppose the device 1 To the device 2 send data , equipment 1 I don't know the equipment 2 When can I receive data , equipment 2 I don't know the equipment 1 When will the data be sent , Then if they use handshake to communicate, it may be in this order :

- equipment 1 take valid Signal setting 1, Tell the device 2, The data is ready , Enclosed please find

- equipment 2 I'm busy at the moment and can't receive data , equipment 2 take ready The signal remains 0

- equipment 2 Free , take ready Signal setting 1 Receiving equipment 1 The data of

- equipment 1 See device 2 Of ready by 1, It knows the equipment 2 The data has been received , take valid Set up 0 At the same time, undo the data , Prepare for the next send

- You can see that because there is handshake control , It can ensure the correct transmission of data , Will not be lost . The design of cross clock domain handshake is to take advantage of handshake control , So as to avoid data transmission errors caused by cross clock domain

RTL Code :

/************************************************************************************* Input : ·clk_a, clk_b Source clock and destination clock ·rst Reset signal ·a_en,data_a It can be used as an agreement , detected a_en It works ( Falling edge ) When , Input data and update , Update the data until a_en The next falling edge of Output : ·b_en Yes a_en Synchronization of ·data_b_out Yes b Synchronization of ·ack_a yes b The response signal in the clock domain ack, Synchronize to a The signal behind the clock field , notice a Time domain ( Falling edge notification ) You can send the next data . in fact ,a_en It's the falling edge of the signal *************************************************************************************/

module syn_handshake(

input wire clk_a , // Source clock

input wire clk_b , // Destination clock

input wire rst ,

input wire a_en , // An enabling signal from the outside , The pulse lasts for one clock cycle

input wire [3:0] data_a_in , // External input signal

output reg [3:0] data_b_out ,

output wire b_en ,

output wire ack_a

);

// Generate a_en The falling edge of Just delay one cycle

reg a_en_d1 ;

//reg a_en_d2 ;

reg a_en_neg ;

always@(posedge clk_a or posedge rst) begin

if(rst) begin

a_en_d1 <= 1'd0;

// a_en_d2 <= 1'd0;

a_en_neg <= 1'd0;

end

else begin

a_en_d1 <= a_en;

// a_en_d2 <= a_en_d1;

// a_en_neg <= ~a_en_d1 && a_en_d2;

a_en_neg <= ~a_en && a_en_d1;

end

end

// Generate request signals

reg a_req ;

wire a2_q_pos;

always@(posedge clk_a or posedge rst) begin

if(rst)

a_req <= 1'd0;

else if(a_en_neg)

a_req <= 1'd1;

else if(a2_q_pos) //a_req Lower conditions

a_req <= 1'd0;

else

a_req <= a_req;

end

// Request signal a_req Cross clock domain processing

reg b1_q, b2_q;

always@(posedge clk_b or posedge rst) begin

if(rst) begin

b1_q <= 1'd0;

b2_q <= 1'd0;

end

else begin

b1_q <= a_req;

b2_q <= b1_q;

end

end

// Generate clock field b Data enable signal in

//b2_q The rising edge of the signal

//b Clock domain pair a The response signal in the clock domain

reg b2_q_d1;

reg b2_q_d2;

reg b2_q_d3;

reg ack_b;

always@(posedge clk_b or posedge rst) begin

if(rst) begin

b2_q_d1 <= 1'd0;

b2_q_d2 <= 1'd0;

b2_q_d3 <= 1'd0;

ack_b <= 1'd0;

end

else begin

b2_q_d1 <= b2_q;

b2_q_d2 <= b2_q_d1;

b2_q_d3 <= b2_q_d2;

ack_b <= b2_q_d2;

end

end

assign b_en = ~b2_q_d3 && b2_q_d2;

//b_en It works , The data is valid , You can sample a The data in the clock field is lost

always@(posedge clk_b or posedge rst) begin

if(rst)

data_b_out <= 4'd0;

else if(b_en)

data_b_out <= data_a_in;

end

// The response signal is synchronized to a Time domain

//a2_q The rising edge serves as a_req Lower conditions

reg a1_q, a2_q;

reg a3_q ;

always@(posedge clk_a or posedge rst) begin

if(rst) begin

a1_q <= 1'd0;

a2_q <= 1'd0;

a3_q <= 1'd0;

end

else begin

a1_q <= ack_b;

a2_q <= a1_q;

a3_q <= a2_q;

end

end

assign a2_q_pos = ~a3_q && a2_q;

assign ack_a = a2_q; // This signal acts as a_en The feedback signal of ,a_en Take the falling edge of this signal

endmodule

Simulation file

`timescale 1ns / 1ps

module tb_syn_handshake;

reg clk_a ;

reg clk_b ;

reg rst ;

reg a_en ; // An enabling signal from the outside , The pulse lasts for one clock cycle

reg [3:0] data_a_in ; // External input signal

wire [3:0] data_b_out ;

wire b_en ;

wire ack_a ;

initial begin

clk_a = 1'd0;

forever begin

#2 clk_a = ~clk_a;

end

end

initial begin

clk_b = 1'd0;

forever begin

#3 clk_b = ~clk_b;

end

end

initial begin

rst = 1'd1;

#15

@(negedge clk_a);

rst = 1'd0;

end

reg ack_a_d1;

always@(posedge clk_a or posedge rst) begin

if(rst) begin

a_en <= 1'd1;

ack_a_d1 <= 1'd0;

end

else begin

ack_a_d1 <= ack_a;

a_en <= ~ack_a && ack_a_d1;

end

end

always@(posedge clk_a or posedge rst) begin

if(rst) begin

data_a_in <= 4'd0;

end

else if(a_en) begin

data_a_in <= $random;

end

end

syn_handshake u_syn_handshake(

.clk_a ( clk_a ),

.clk_b ( clk_b ),

.rst ( rst ),

.a_en ( a_en ),

.data_a_in ( data_a_in ),

.data_b_out ( data_b_out ),

.b_en ( b_en ),

.ack_a ( ack_a )

);

endmodule

Simulation results

5、 ... and 、 Asynchronous dual port RAM

Numbers IC The basis of the written test : Synchronous and asynchronous dual port RAM Realization

stay FPGA In design , Often used RAM, there RAM Generally refers to static RAM(SRAM). commonly FPGA There is the so-called block RAM, It's ready-made RAM resources . Usually , We use IP nucleus , Design , Let's design our own IP nucleus .

RAM Divided into single ended 、 Pseudo double terminal 、 True two terminal three modes .

- Single ended RAM Read and write share an address

- Pseudo double terminal RAM A write port , A read port , Respective addresses and enabling signals , The write port is only responsible for writing , The read port is only responsible for reading , So it's called pseudo double ended

- What a double mouth RAM You can access any address at any time , The addresses of the two ports are the same , Shared memory and address . This brings about a problem : There will be conflicts when reading and writing an address at the same time . Based on this contradiction, it is necessary to set restrictions

Next , use Verilog Implement an asynchronous dual port RAM, depth 128, A wide 16bit.A Write in ,B The mouth reads . Support film selection , Read write request , Requirement code can be integrated .

RTL Code

/************************************************************************* Implement an asynchronous dual port RAM, depth 128, A wide 16bit.A Write in ,B The mouth reads . Support film selection , Read write request , Requirement code can be integrated *************************************************************************/

module Dual_Port_Sram #(

parameter ADDR_WIDTH = 7, // Address bit width

parameter DATA_WIDTH = 16, // Data bit width

parameter DATA_DEPTH = 1 << ADDR_WIDTH // The depth of the data = 2^ADDR_WIDTH

) (

input clka ,

input clkb ,

input rst_n ,

input csen_n , // Piece of optional signal , Low efficiency

/*************Port A Signal Write********************************/

input [ADDR_WIDTH-1:0] addra ,

input [DATA_WIDTH-1:0] data_a ,

input wrena_n ,

/*************Port B Signal Read********************************/

input [ADDR_WIDTH-1:0] addrb ,

input rdenb_n ,

output [DATA_WIDTH-1:0] data_b

);

/************* A Port write logic *********************************/

integer i;

reg [DATA_WIDTH-1:0] register[DATA_DEPTH-1:0]; // Memory definition

always @(posedge clka or negedge rst_n) begin

if(!rst_n) begin

for(i = 0; i < DATA_DEPTH; i = i + 1)

register[i] <= 0;

end

else if(!wrena_n && !csen_n)

register[addra] <= data_a;

end

/************* B Port read logic *********************************/

reg [DATA_WIDTH-1:0] rddata_b;

always @(posedge clkb or negedge rst_n) begin

if(!rst_n)

rddata_b <= 1'b0;

else if(!rdenb_n && !csen_n)

rddata_b <= register[addrb];

else

rddata_b <= rddata_b;

end

assign data_b = rddata_b;

endmodule

Simulation file

`timescale 1ns/1ps

module tb_Dual_Port_Sram;

parameter ADDR_WIDTH = 7; // Address bit width

parameter DATA_WIDTH = 16; // Data bit width

parameter DATA_DEPTH = 1 << ADDR_WIDTH; // The depth of the data = 2^ADDR_WIDTH

reg clka ;

reg clkb ;

reg rst_n ;

reg csen_n ;

reg [ADDR_WIDTH-1:0] addra ;

reg [DATA_WIDTH-1:0] data_a ;

reg wrena_n ;

reg [ADDR_WIDTH-1:0] addrb ;

reg rdenb_n ;

wire [DATA_WIDTH-1:0] data_b ;

Dual_Port_Sram #(

.ADDR_WIDTH (ADDR_WIDTH),

.DATA_WIDTH (DATA_WIDTH),

.DATA_DEPTH (DATA_DEPTH)

)u_Dual_Port_Sram(

.clka (clka ),

.clkb (clkb ),

.rst_n (rst_n ),

.csen_n (csen_n ),

.addra (addra ),

.data_a (data_a ),

.wrena_n (wrena_n),

.addrb (addrb ),

.rdenb_n (rdenb_n),

.data_b (data_b )

);

initial begin

clka = 1'd0;

forever begin

#2 clka = ~clka;

end

end

initial begin

clkb = 1'd0;

forever begin

#3 clkb = ~clkb;

end

end

initial begin

rst_n = 1'b0;

csen_n = 1'b1;

wrena_n = 1'b1;

addra = 1'b0;

data_a = 1'b0;

rdenb_n = 1'b1;

addrb = 1'b0;

#50

rst_n = 1'b1;

csen_n = 1'b0;

#10

wrena_n = 1'b0;

repeat (DATA_DEPTH-1) begin

@(posedge clka) begin

addra = addra + 1;

data_a = data_a + 1;

end

end

#35

wrena_n = 1'b1;

rdenb_n = 1'b0;

repeat (DATA_DEPTH-1) begin

@(posedge clkb) begin

addrb = addrb + 1;

end

end

#50

rdenb_n = 1'b1;

csen_n = 1'b1;

#100 $stop;

end

endmodule

Simulation results

summary

This is the first part , It may also be a difficult part of the interview , But it should also be part of the regular exam . Study the code carefully , The circuit diagram and sequence diagram should be able to be confident .

Because there are some things that refer to the Internet , If there is infringement , Please inform , Then I delete or mark it out .

版权声明

本文为[Jian Chen~]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204222341591854.html

边栏推荐

- 分享两道最近做的比较经典的OJ题(排列子序列+字符串中找出连续最长的数字串)

- 共轭梯度法(Conjugate Gradients)(4)

- 金融信息安全实训——22/4/19(下)

- On Spartacus product details page, use outlet to display user-defined data

- FileNotFoundError: [Errno 2] No such file or directory: 'image/1. Jpg 'problem solving

- LeetCode 1446 - 1449

- 北京航空航天大学开通CnOpenData试用

- 51 单片机学习_4-2 数码管动态显示

- 居家第二十二天的绿豆芽

- (MM-2018)用于行人重识别的局部卷积神经网络

猜你喜欢

Method of shrinking master-slave nodes in redis cluster cluster

Visual studio always conflicts with Sogou input method

visual studio 总是和搜狗输入法冲突

【leetcode】二叉树,226翻转二叉树,116填充二叉树节点的右侧指针,114将二叉树展开为链表

Install mujoco and mujoco on win10_ py,gym

![[leetcode] binary tree, maximum depth of 104 binary tree, diameter of 543 binary tree, maximum path and sum of 124 binary tree](/img/f8/5de0ecee78a6f9c9bd8562629355be.png)

[leetcode] binary tree, maximum depth of 104 binary tree, diameter of 543 binary tree, maximum path and sum of 124 binary tree

Conjugate gradients (4)

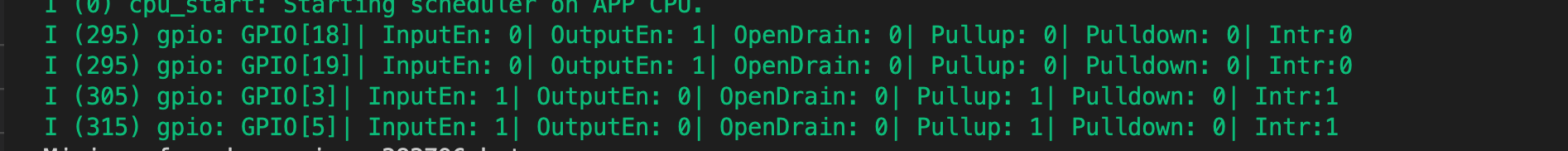

Esp32 (GPIO) - GPIO learning (5)

![[leetcode] binary tree, 654 largest binary tree, 105 constructs binary tree according to preorder and inorder traversal, 106 constructs binary tree according to inorder and postorder traversal, and 88](/img/7c/435c5f6ed591b81084020bc73c7db7.jpg)

[leetcode] binary tree, 654 largest binary tree, 105 constructs binary tree according to preorder and inorder traversal, 106 constructs binary tree according to inorder and postorder traversal, and 88

Invite you to participate in the ume plug-in development competition

随机推荐

[leetcode] binary tree, in-depth understanding of the first, middle and last order

【年度总结】继往开来:回首不靠谱的2021,希冀靠谱的2022

LeetCode 1446 - 1449

51 单片机学习_4-2 数码管动态显示

JS to traverse the array

邀请你参与字节跳动 UME 插件开发竞赛

Want others to watch your video? Comment on your video? It's enough to learn these two moves

[PCIe 6.0] new features of PCIe 6.0 - detailed explanation of dmwr (deferred memory write)

VsCode使用EmmyLua插件调试Unity工程ToLua代码

Introduction to opencv (II) -- affine transformation and perspective transformation

Typora样式调优

[pyGame] can the little dinosaur on chrome be played with code? It looks like fun~

Ajustement de style typora

LeetCode 1446 - 1449

共轭梯度法(Conjugate Gradients)(3)

【DVCon2020】基于Signoff Abstract Model的低功耗设计层级验证加速

Huawei machine test question - hj73 calculation date to day conversion

visual studio 2019恢复默认设置

【DVCon2020】软件兄弟呐喊:硬件兄弟,请你做个人

[perseverance challenge] PCIe ask and answer every day (filed on February 2022)