当前位置:网站首页>[dvcon2020] automatic generation method of UVM sequence based on ral

[dvcon2020] automatic generation method of UVM sequence based on ral

2022-04-22 23:28:00 【MangoPapa】

Click to enter 【 Chip design verification 】 Community , See more

Statement :

- 🥭 Author URI :【MangoPapa Of CSDN Home page 】.

- ️ This article was first published in CSDN, Please indicate the source of reprint or quotation 【 Click to view the original 】.

- ️ The purpose of this column is Academic paper sharing , This paper is non-profit , Only used for Personal learning record And Knowledge sharing .

- ️ If the pictures or relevant references used in this article infringe upon your legitimate rights and interests , Please contact me to delete .

- Welcome to point out the mistakes in the article , Welcome colleagues to communicate with me ~

- mailbox :[email protected]

List of articles

Overview of the paper

The title of this paper is Automated Generation of RAL-based UVM Sequences, The author is Intel Canadian Engineers .

This paper puts forward a kind of be based on RAL( Register abstraction layer ) Of UVM Sequence Automatic generation Method , And discussed it. By dividing TB Constrain the range to speed up the simulation The problem of .

research objective

generally , We control by configuring a set of registers DUT The hardware behavior of , In order to make DUT Work in a certain feature Next . For different feature, The configured registers and the order of the configured registers may be different . at present , The common method of configuring registers is to use UVM RAL Model To configure the DUT register . That means : We need to target every feature Draw up a programming sequence, and coding become uvm sequence.

I think everyone DV Students have encountered these situations in the verification process :feature That's too much ,feature It has changed again ,programming sequence It has changed again , The register has changed again …… Write manually 、 Manual modification , My hands are numb , It makes people swear .

What do I do ? automation ! Automate with scripts !

The new method

This paper puts forward a kind of Automatic generation from design documents based on RAL Of UVM Sequence Methods , And discussed it. By dividing TB Constrain the range to speed up the simulation The problem of . chart 1 It's script generation UVM sequence Of UVM The test framework .

The main idea of this method is summarized as follows :

- Standard design documents . Write a design in a specific format spec, Machine readable is required . This document needs to contain two important sub documents spec, One is the register spec, The second is each feature Of programming sequence spec.

- Parsing script . Automatically parse the document with a script , Automatic generation uvm sequence and ral sequence.

- Every time the design document is updated , Re parse and regenerate the related data sequence that will do .

In the above methods , There are a few places I would like to focus on :

- In design documents programming sequence It is designed as a state machine form of directed acyclic graph , It is convenient for the script to correctly generate the corresponding uvm sequence.

- In order to improve the coverage, It needs to be right RAL Model The register values of are random in a large range . In larger designs , But considering that there may be dependencies between registers , Only by ral At random or manually ral It is unrealistic to add random constraints in ,ral model Random constraints on all registers are complex , It takes a long time to break the contract . And it's different feature Next ral model The random scheme is also different . In this automatic generation environment , How to achieve it ?—— For use config_db, every last feature Of test Of uvm sequence All correspond to a specific config_db, stay test in set to ral sequence, And only randomly what we're verifying block Related registers , So as to reduce the time of solving the random constraint ( It's the accelerated simulation mentioned earlier ), It can also prevent random unexpected wrong results .

Discuss

This method is good ,DV No longer afraid of changes in design documents !

The method is a good one , But to tell you the truth, , The automatic generation used in this paper test sequence The concept of is not very new , Mature companies have similar scripts .

Really use this method , need DE Students are writing design spec Be more standard when you . In especial programming sequence, How to configure each register 、 How much , Write clearly . So much feature …… This method The liberation of the DV, bitter DE ah , It is estimated that DE I'm going to curse my mother .DE Don't write DV You can write if you like , If no one writes , This method doesn't work .

End

Click to enter 【 Chip design verification 】 Community , See more

版权声明

本文为[MangoPapa]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204222322441015.html

边栏推荐

- 古典问题:有一对兔子,从出生后第3个月起每个月都生一对兔子,小兔子长到第三个月后每个月又生一对兔子,假如兔子都不死,每个月的兔子总数为多少?

- 【Objective-C 高级编程】—— GCD

- 程序设计语言基础(1)

- Pytorch convolution kernel filling and stride, multiple input and multiple output channels, pool layer

- UVM源码解读,UVM-1.2 code review notes

- 在Spartacus产品明细页面用outlet显示自定义数据

- JS has several red, white and black balls, including 25 red and white balls, 31 white and black balls and 28 red and black balls. Find the number of each of the three balls.

- Numeric type and sequence type

- 【PCIe 实战】SNPS PCIe 开启 SRIS mode

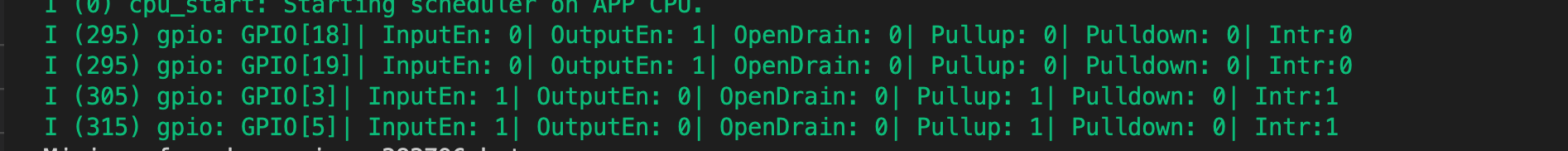

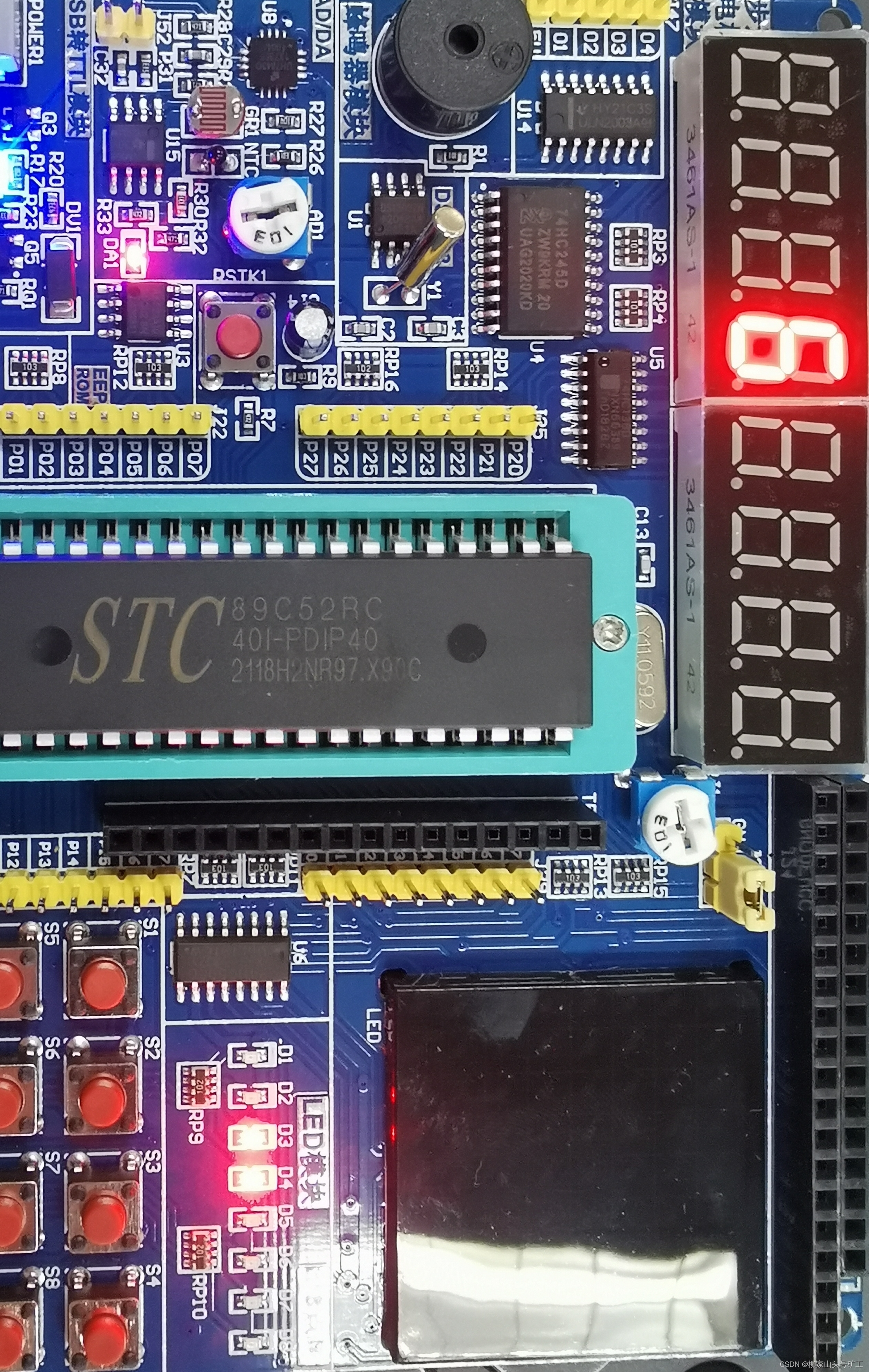

- Esp32 (GPIO) - GPIO learning (5)

猜你喜欢

JS计算圆的周长和面积

JSON. In golang Marshall pit

ESP32 (GPIO)-GPIO学习(5)

codeforce round#784(div4) A-H

编写程序,实现电子时钟自动走动的效果并提供一个按钮控制电子时钟是否停止走动。

Write a program to realize the effect of automatic movement of the electronic clock, and provide a button to control whether the electronic clock stops moving.

51 单片机学习_4-1 数码管显示

辰视工业级机器视觉 | 焊缝检测解决方案

Detailed explanation of SQL language

visio文本框输入公式

随机推荐

L1-049 ladder race seat allocation (20 points) (in-depth understanding of for loop + three-dimensional array + error analysis)

[*CTF2022]web题目复现及wp

[leetcode refers to offer 54. The k-th node of the binary search tree (simple)]

[hctf 2018] admin flash session forgery

80386汇编_全局描述表GDT介绍

Golang中json.Marshal避坑

PCIe 参考时钟架构 (Refclk Architecture)

华为机试题——HJ76 尼科彻斯定理

django连接数据库获取数据

读《Software Engineering at Google》(13)

Shell script command results are saved to variables with line breaks

邀请你参与字节跳动 UME 插件开发竞赛

Django指定数据库的时候报No module named ‘django_test.settings‘

Go timer time Ticker

【经验分享】分享 MangoPapa 的论文学习经验

Le Code [SWIFT] déclenche l'événement de clic d'uibutton

[dvcon2020] simulation acceleration method based on multithreaded UVM test platform

Pytorch convolution kernel filling and stride, multiple input and multiple output channels, pool layer

【毅力挑战】PCIe 每日一问一答(2022.02 归档)

JS to traverse the array