当前位置:网站首页>Some work experience after joining the digital ic design

Some work experience after joining the digital ic design

2022-08-11 02:24:00 【the rice is delicious】

First, the circuit framework and timing analysis of the code

The way of writing code in previous courses is relatively direct and casual. After generally understanding the design requirements, I start writing code without paying attention to the requirements of clock and reset. The sensitive variables of the always block are alsoAll kinds of latches are generated, and the generated latches are even more numerous. After writing, the code can run through the behavioral simulation and can be used on the development board, and the learning task of one semester is completed.

The disadvantages of this method are also significant: although the results of some codes in behavioral simulation are correct, their actual performance on the development board is not satisfactory.Various bugs appear.In the final analysis, the understanding of the code was not deep enough at that time, and there was no need to realize what kind of circuit these codes generated, and what kind of results such a circuit would cause.There will be no bugs of all kinds.Such techniques are also very practical in work. There are a lot of codes to be built in the future, the framework is very complex, and the sub-modules and top modules are stacked one by one.Timing analysis, it is very difficult to modify the code framework after encountering a bug in the later stage, and it is not conducive to us to understand the logic function of the entire circuit.Therefore, drawing circuit diagrams and waveform diagrams frequently is the first step to do a good job in front-end design.

The first counter circuit diagram drawn by the landlord after joining the job

Second, consider the practicality of the code from different angles

Digital chip design is a very time- and money-consuming industry. After the formed circuit is made into a mask and photoetched on the silicon wafer, it cannot be changed.Therefore, there are many factors and influences that need to be considered when designing the code.At the design point, the algorithm and function of the circuit implementation and the required resources must be planned first.After the design is completed, it must pass the verification and testing of the back-end.Therefore, when writing code, you should also consider the back-end timing analysis and STA.

For example, for a multi-bit counter, if the synchronous clock is used, the gate circuit device will be much more expensive than the asynchronous clock, but the asynchronous design is not used in the verilog HDL design.Because asynchronous sequential logic is difficult to control the competition and risk caused by combinational logic and delay, the more complex the circuit, the more difficult it is to debug the asynchronous design, and the trigger conditions of the asynchronous design are complex, and asynchronous changes may be triggered at any time, causingMetastability, etc.The most important thing is that asynchronous design will make back-end verification and STA (static timing analysis) extremely complicated. The back-end requires clock and reset (jump control signal) to be relatively pure, and too many sensitive variables.It will make it difficult for STA to proceed, so asynchronous design is generally not used.Similarly, the clock and reset signals and other variables are not allowed to do some logic operations, which will cause the clock or reset to be less pure.

Three, the means of debugging

After the code is written, behavior-level simulation must be performed. When viewing the waveform, it is inevitable that some parts do not meet the design requirements and need to be modified.But must not modify the standard framework of the circuit just to figure out the correct timing, for example: adding signals other than reset and clock difference to the sensitive list of the always block will also makeBackend validation work gets complicated.Or put the same signal in multiple always blocks to assign values.If this is the only way to meet the design requirements, then the initial design is definitely unreasonable, and we must try to find the problem from the design method itself.

边栏推荐

- WeChat public account background management

- 软件测试面试题:缺陷等级应如何划分?

- Experiment record of Shengxin (part3)--scipy.spatial.distance_matrix

- mysql 死锁 Deadlock found when trying to get lock; try restarting transaction

- 报错处理:org.xml.sax.SAXParseException: 不允许有匹配 “[xX][mM][lL]“ 的处理指令目标

- Ora - 00001 in violation of the only constraint

- 软件测试面试题:I P协议、RARP协议、ICMP协议与ARP协议的功能是什么?

- 如何开展性能测试,你知道吗?

- 掌握这几招,轻松K.O面试官,Offer拿到吐

- 对加密世界的经济误解:现金是储蓄?稀缺性创造价值?

猜你喜欢

TRCX:掺杂过程分析

qtcreator调试webkit

SyntaxError: invalid syntax

![[The method of calling the child page from the parent page of the iframe] Stepping on the pit: It is the key to use `[x]` when getting elements. You cannot use `.eq(x)`, otherwise it will not be obtai](/img/ec/0cca8c7011770429c34a6aa1f36460.png)

[The method of calling the child page from the parent page of the iframe] Stepping on the pit: It is the key to use `[x]` when getting elements. You cannot use `.eq(x)`, otherwise it will not be obtai

①CAS SSO单点登录框架源码深度分析

![报错处理:org.xml.sax.SAXParseException: 不允许有匹配 “[xX][mM][lL]“ 的处理指令目标](/img/35/650c92ac4c5fc2d5826f3216a09e65.png)

报错处理:org.xml.sax.SAXParseException: 不允许有匹配 “[xX][mM][lL]“ 的处理指令目标

WeChat public account background management

微信公众号后台管理

多线程之ThreadPoolExecutor

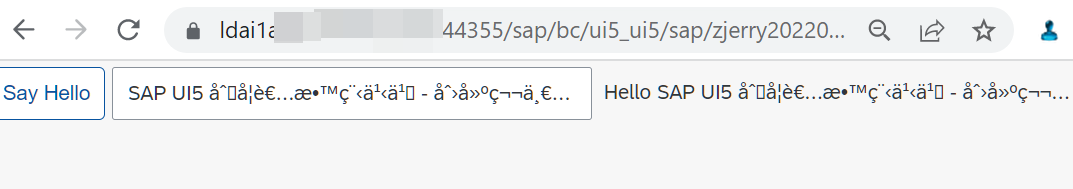

117. 本地开发好的 SAP UI5 应用部署到 ABAP 服务器时,中文字符变成乱码的原因分析和解决方案

随机推荐

学军中学推理社2017届招新试题

软件测试面试题:性能测试工作?

Js prototype and prototype chain and prototype inheritance

How to solve the problem of Tomcat booting and crashing

关于地图GIS开发事项的一次实践整理(上)

测试3年,开口就要25k?面试完最多给15k...

第二课第一周第4-6节 医学预后案例欣赏+作业解析

leetcode 739. Daily Temperatures 每日温度(中等)

[4G/5G/6G专题基础-154]: 5G无线准入控制RAC(Radio Admission Control)

通过热透镜聚焦的高斯光束

软件测试面试题:Web服务器指标指标?

shell [stdin/stdout/stderr][重定向]

Mysql_Note6

PIFuHD配置记录

【备战“金九银十”】2022年软件测试面试题最新汇总

【oops-framework】模板项目【oops-game-kit】使用简介

软件测试面试题:在频繁的版本发布中,如何回归测试?

2022制冷与空调设备运行操作考试试题模拟考试平台操作

软件测试面试题:软件测试的过程的V模型,说出它的缺点?

生信实验记录(part2)--tf.reduce_sum()用法介绍