当前位置:网站首页>The fifth bullet of FPGA development: hand rubbing breathing light code

The fifth bullet of FPGA development: hand rubbing breathing light code

2022-08-07 07:02:00 【WeeHours.】

The fifth bullet of FPGA development: hand rubbing breathing light code

The PWM method adopted by the breathing light controls the brightness of the LED light by adjusting the duty cycle at a fixed frequency.PWM stands for Pulse Width Limitation.

Under the fixed-period PWM signal generated by the counter, the duty cycle is 0, and the LED is not bright; the duty cycle is 100%, and the LED is the brightest.Changing the duty cycle from 0 to 100, the breathing light effect can be achieved.

The schematic diagram of PWM duty cycle adjustment is as follows:

![[External link image transfer failed, the origin site may have an anti-leech mechanism, it is recommended to save the imageDirect upload(img-YTjRhxW2-1659583228704)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803103824553.png)]](/img/83/f2b49e496721f240a57df46165a88e.png)

The longer the LED is high, the brighter the LED, and the shorter the high time, the darker the LED.

The module port and structural block diagram of this experiment are shown in the following figure:

![[External link image transfer failed, the source site may have an anti-leech mechanism, it is recommended to save the imageDirect upload (img-ucpJAS1B-1659583228707)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803110624728.png)]](/img/03/6cf43182b3b8fd0679b49cc398924e.png)

The pin assignments of the system clock, key reset and LED port in the experiment are shown in the table below.

![[External link image transfer failed, the origin site may have an anti-leech mechanism, it is recommended to save the imageDirect upload (img-yy7CrpmM-1659583228708)(C:\Users\user\AppData\Roaming\Typora\typora-user-images\image-20220803144717771.png)]](/img/5e/9a4988144aa9af113f9eb9f145468d.png)

The corresponding XDC constraint statement is as follows:

create_clock -name clk -period 20 [get_ports clk]set_property -dict {PACKAGE_PIN R4 IOSTANDARD LVCMOS33} [get_ports clk]set_property -dict {PACKAGE_PIN U2 IOSTANDARD LVCMOS33} [get_ports rst]set_property -dict {PACKAGE_PIN R2 IOSTANDARD LVCMOS33} [get_ports led] The breathing light code is as follows:

module breath_led(input clk,input rst,output led);reg[15:0] period;reg[15:0] pwm;reg state;//led changes according to the state of period and pwmassign led=(period>=pwm)?1'b1:1'b0;//Counter, record 50000, 20nsalways @(posedge clk or negedge rst)beginif(rst==0)period<=16'd0;else if(period==16'd50000)period<=16'd0;elseperiod<=period+1'b1;endalways @(posedge clk or negedge rst)//duty cycle setting modulebeginif(rst==0)beginpwm<=16'd0;//Initialize pwm to 0, state to 0state<=1'b0;endelsebeginif(period==16'd50000)//If the counter is fullbeginif(state==1'b0)//If the state is 0beginif(pwm==16'd50000)//If pwm=50000state<=1'b1;//The state is changed to 1else//pwm!=50000pwm<=pwm+16'd25;//pwm changes with 25endelse//If the state is 1beginif(pwm==16'd0)//If pwm=0state<=1'b0;//The state is changed to 0else//pwm!=0pwm<=pwm-16'd25;//pwm gradually decreases by 25endendendendendmodule The core is the comparison between the current cycle count value and the duty cycle. If the current cycle count value is less than or equal to the duty cycle count value, the LED outputs a high level, that is, lights up;If the value is greater than the duty cycle value, the LED output is low, that is, it goes out.

Finally, a bitstream is generated for download verification.

For specific operation steps, please refer to the first bullet of FPGA development: The first bullet of FPGA development: Vivado software installation, development and useBuilding with the project The above is the breathing light experiment I conducted, and I continue to be familiar with the entire FPGA development process. If you are doing your own project, you can’t miss every step. Every step needs to be summed up and mastered carefully.proficient!Welcome everyone to private message me to exchange and learn together, and welcome everyone to criticize and correct!

边栏推荐

- VoLTE Basic Self-Learning Series | VoLTE Network Architecture

- Powerful number

- LeetCode 628. Maximum Product of Three Numbers

- 用户登录模块---Druid+JDBC+Servlet

- VoLTE Basic Self-Learning Series | The relationship between IMS, VOIP, VoLTE, and RCS?

- VoLTE基础自学系列 | RTP及RTCP协议原理

- 网络安全笔记4——消息认证与杂凑函数

- pytest框架之fixture测试夹具详解

- VoLTE Basic Self-Learning Series | What is Silent Redial in VoLTE?How does it relate to CSFB?

- How to use the @Async annotation

猜你喜欢

神经网络权值是什么意思,神经网络权重取值范围

FPGA开发第二弹:流水灯实验

The spyder/conda installation package reports an error: conda info could not be constructed. KeyError: 'pkgs_dirs'

VoLTE Basic Self-Learning Series | What are transparent data and non-transparent data in VoLTE?

Gaussian Temporal Awareness Networks GTAN论文阅读笔记

Top 20 most popular plugins for QGIS

LeetCode 剑指 Offer 24. 反转链表

LeetCode 1408. String matching in arrays

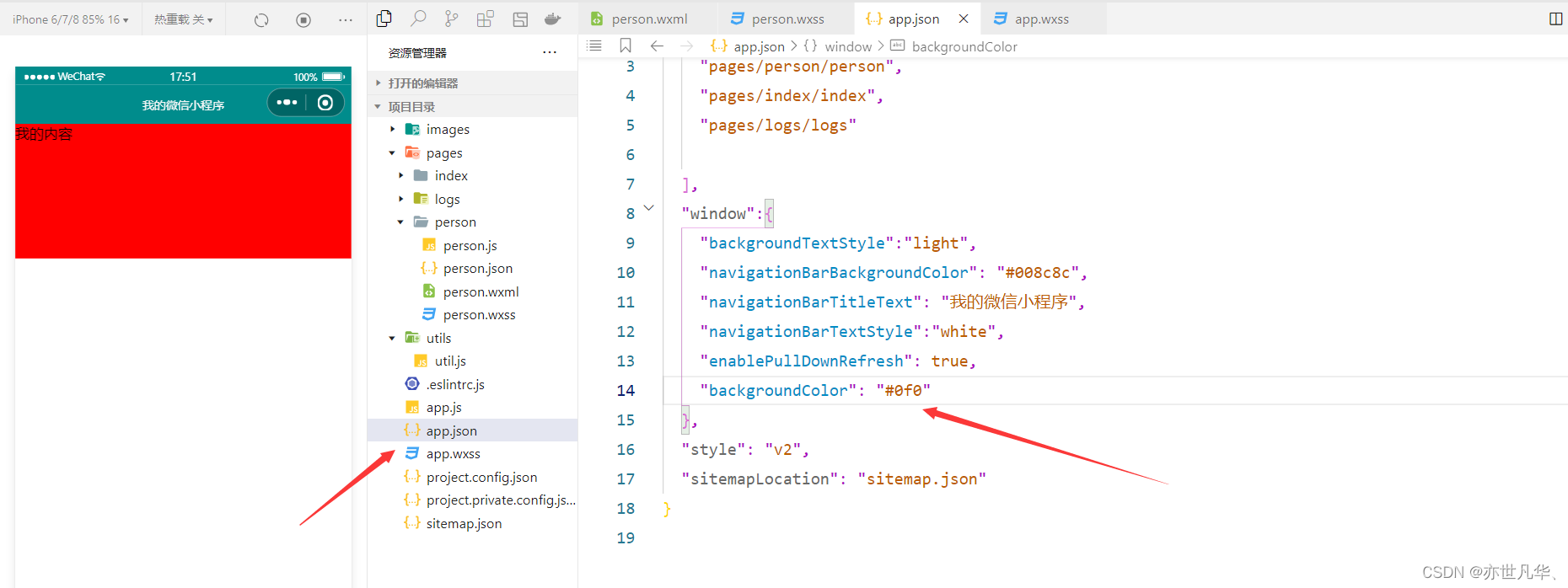

微信小程序--》小程序全局配置和详解下拉刷新和上拉触底页面事件

神经元细胞属于什么细胞,人体有多少神经元细胞

随机推荐

OC-run loop

MySQL - index optimization

[Array Questions] LeetCode 969. Pancake Sorting

WEB安全基础 - - -弱口令和暴力破解

网络安全笔记3——双钥密码体制

Codeforces Summer Training Weekly Report (7.28~8.3)

VoLTE basic self-study series | IP layer routing and addressing process in IMS network (implementation in registration process)

Qt 使用SQLite的性能优化的亿点点记录

VoLTE Basic Self-Learning Series | What is Forking in SIP and IMS

机器学习中的线性回归——基于R

排序--希尔排序

This beta version of Typora is expired

LeetCode points to Offer 24. Reverse linked list

VoLTE basic self-study series | RTP and RTCP protocol principles

LNK2001 unresolved external symbol cuGetErrorName resolved

servlet 教程 2:返回 jsp 页面

Learning salient boundary feature for anchor-free temporal action localization AFSD阅读笔记

servlet tutorial 1: environment setup and new servlet project

VoLTE基础自学系列 | IMS网络概述

网络安全笔记2——单钥密码体制