当前位置:网站首页>牛客网 Verilog 在线编程题库解答(VL1~VL10)

牛客网 Verilog 在线编程题库解答(VL1~VL10)

2022-08-09 17:28:00 【洋洋2020】

目录

VL1 四选一多路器

`timescale 1ns/1ns

module mux4_1(

input [1:0] d1,d2,d3,d0,

input [1:0] sel,

output[1:0] mux_out

);

reg [1:0] mux_out;

[email protected](*) begin

case(sel)

2'b00: mux_out <= d3;

2'b01: mux_out <= d2;

2'b10: mux_out <= d1;

2'b11: mux_out <= d0;

default: mux_out <= d0;

endcase;

end

endmodule

VL2 异步复位的串联 T 触发器

`timescale 1ns/1ns

module Tff_2 (

input wire data, clk, rst,

output reg q

);

reg q0;

[email protected](negedge rst or posedge clk) begin

if(~rst) begin

q0 <= 1'b0;

q <= 1'b0;

end

else begin

q0 <= data ^ q0;

q <= q0 ^ q;

end

end

endmodule

VL3 奇偶校验

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

reg check_odd;

reg check_even;

[email protected](*) begin

check_odd <= ^bus;

check_even <= ~(^bus);

end

assign check = (sel)? check_odd: check_even;

endmodule

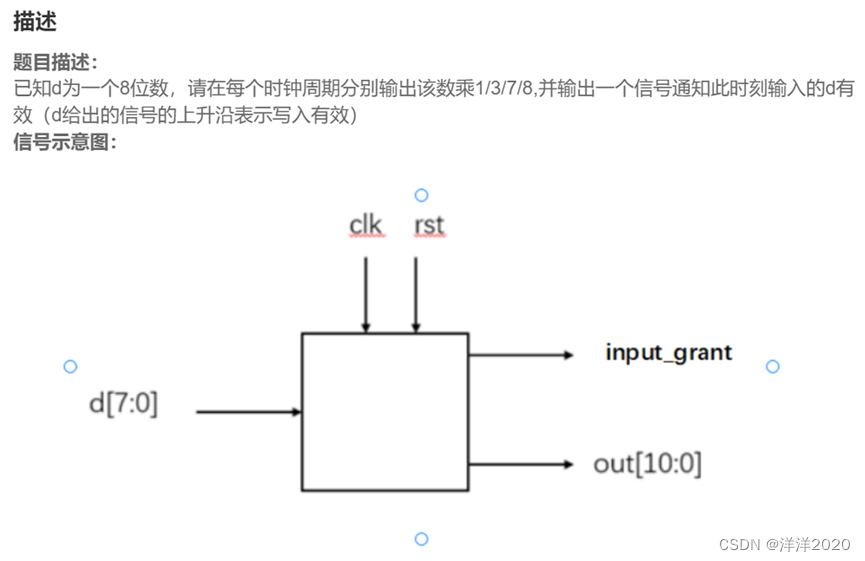

VL4 移位运算与乘法

`timescale 1ns/1ns

module multi_sel(

input [7:0]d,

input clk,

input rst,

output reg input_grant,

output reg [10:0]out

);

reg [10:0] d_m1, d_m2, d_m4, d_m8;

reg [1:0] pulse_cnt;

[email protected](negedge rst or posedge clk) begin

if(!rst)

pulse_cnt <= 2'd0;

else begin

pulse_cnt <= pulse_cnt + 1;

end

end

[email protected](negedge rst or posedge clk) begin

if(!rst) begin

d_m1 <= 11'd0;

d_m2 <= 11'd0;

d_m4 <= 11'd0;

d_m8 <= 11'd0;

end

else begin

if(pulse_cnt == 0) begin

d_m1 <= {3'd0,d};

d_m2 <= {2'd0,d,1'd0};

d_m4 <= {1'd0,d,2'd0};

d_m8 <= {d,3'd0};

end

end

end

[email protected](negedge rst or posedge clk) begin

if (!rst) begin

out <= 11'd0;

input_grant <= 1'b0;

end

else begin

case(pulse_cnt)

2'b00: begin

out <= {3'd0,d};

input_grant <= 1'b1;

end

2'b01: begin

out <= d_m2 + d_m1;

input_grant <= 1'b0;

end

2'b10: begin

out <= d_m4 + d_m2 + d_m1;

input_grant <= 1'b0;

end

2'b11: begin

out <= d_m8;

input_grant <= 1'b0;

end

endcase;

end

end

endmodule

VL5 位拆分与运算

`timescale 1ns/1ns

module data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,

output [4:0]out,

output validout

);

reg [15:0] d_buf;

reg [4:0] out;

[email protected](negedge rst or posedge clk) begin

if (!rst)

d_buf <= 16'd0;

else

if(sel == 2'b00)

d_buf <= d;

end

[email protected](*) begin

case(sel)

2'b01: out <= d_buf[3:0] + d_buf[7:4];

2'b10: out <= d_buf[3:0] + d_buf[11:8];

2'b11: out <= d_buf[3:0] + d_buf[15:12];

default: out <= 16'd0;

endcase;

end

assign validout = (sel == 2'b00)? 1'b0:1'b1;

endmodule

VL6 多功能数据处理器

`timescale 1ns/1ns

module data_select(

input clk,

input rst_n,

input signed[7:0]a,

input signed[7:0]b,

input [1:0]select,

output reg signed [8:0]c

);

[email protected](negedge rst_n or posedge clk) begin

if(~rst_n)

c <= 0;

else

case(select)

2'b00: c <= a;

2'b01: c <= b;

2'b10: c <= a+b;

2'b11: c <= a-b;

default: c <= 0;

endcase;

end

endmodule

VL7 求两个数的差值

`timescale 1ns/1ns

module data_minus(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

output reg [8:0]c

);

[email protected](negedge rst_n or posedge clk) begin

if(~rst_n)

c <= 0;

else

c <= (a > b)? a-b: b-a;

end

endmodule

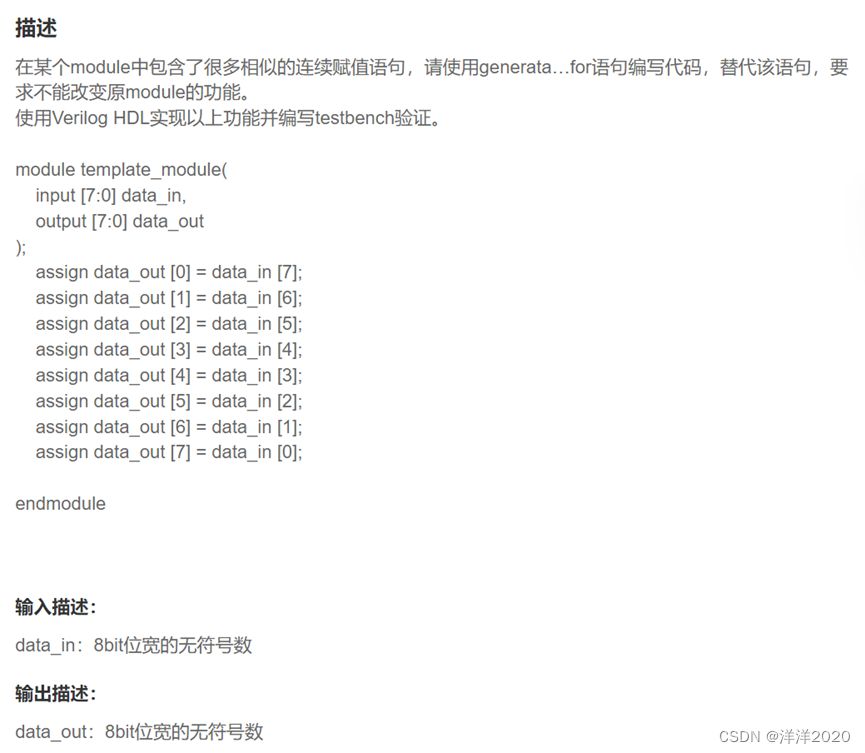

VL8 使用 generate...for 语句简化代码

`timescale 1ns/1ns

module gen_for_module(

input [7:0] data_in,

output [7:0] data_out

);

reg [7:0] data_out;

genvar i;

generate

for(i=0; i<8; i=i+1) begin: data_out_assign

[email protected](data_in[7-i]) begin

data_out[i] <= data_in[7-i];

end

end

endgenerate

endmodule

VL9 使用子模块实现三输入数的大小比较

`timescale 1ns/1ns

module main_mod(

input clk,

input rst_n,

input [7:0]a,

input [7:0]b,

input [7:0]c,

output [7:0]d

);

wire [7:0] tmp1,tmp2;

sub_mod sub_mod_inst0 (

.clk (clk ),

.rst_n(rst_n),

.inx (a ),

.iny (b ),

.zout (tmp1 )

);

sub_mod sub_mod_inst1 (

.clk (clk ),

.rst_n(rst_n),

.inx (a ),

.iny (c ),

.zout (tmp2 )

);

sub_mod sub_mod_inst2 (

.clk (clk ),

.rst_n(rst_n),

.inx (tmp1 ),

.iny (tmp2 ),

.zout (d )

);

endmodule

module sub_mod(

input clk,

input rst_n,

input [7:0] inx,

input [7:0] iny,

output [7:0] zout

);

reg [7:0] zout;

[email protected](negedge rst_n or posedge clk) begin

if(~rst_n)

zout <= 0;

else

zout <= (inx < iny)? inx: iny;

end

endmodule

VL10 使用函数实现数据大小端转换

`timescale 1ns/1ns

module function_mod(

input clk,

input rst_n,

input [3:0]a,

input [3:0]b,

output [3:0]c,

output [3:0]d

);

reg [3:0] c;

reg [3:0] d;

function [3:0] reverse;

input [3:0] din;

integer i;

begin

for(i = 0;i < 4;i=i+1)

reverse[i] = din[3-i];

end

endfunction

[email protected](*) begin

if(~rst_n) begin

c <= 0;

d <= 0;

end

else begin

c <= reverse(a);

d <= reverse(b);

end

end

endmodule

边栏推荐

- 艺术与科技的狂欢,云端XR支撑阿那亚2022砂之盒沉浸艺术季

- 50道Redis面试题,来看看你会多少?

- The difference between approach and method

- 安装搭建私有仓库 Harbor

- The principle implementation of handwritten flexible.js, I finally understand the multi-terminal adaptation of the mobile terminal

- d中简单禁止垃集

- win10 uwp 获得Slider拖动结束的值

- Flink运行架构

- One-key login principle of local number

- LeetCode笔记:Biweekly Contest 84

猜你喜欢

混动产品助力,自主SUV市场格局迎来新篇章

uniapp中使用网页录音并上传声音文件(发语音)——js-audio-recorder的使用【伸手党福利】

Self-taught software testing, how far can I go out to find a job?

loadrunner脚本--参数化

释放数据价值的真正法宝,数据要素市场化开发迫在眉睫

Can't install the Vmware virtual machine on the Ark Kai server?

The senior told me that the MySQL of the big factory is connected through SSH

50道Redis面试题,来看看你会多少?

太厉害了!华为大牛终于把 MySQL 讲的明明白白(基础 + 优化 + 架构)

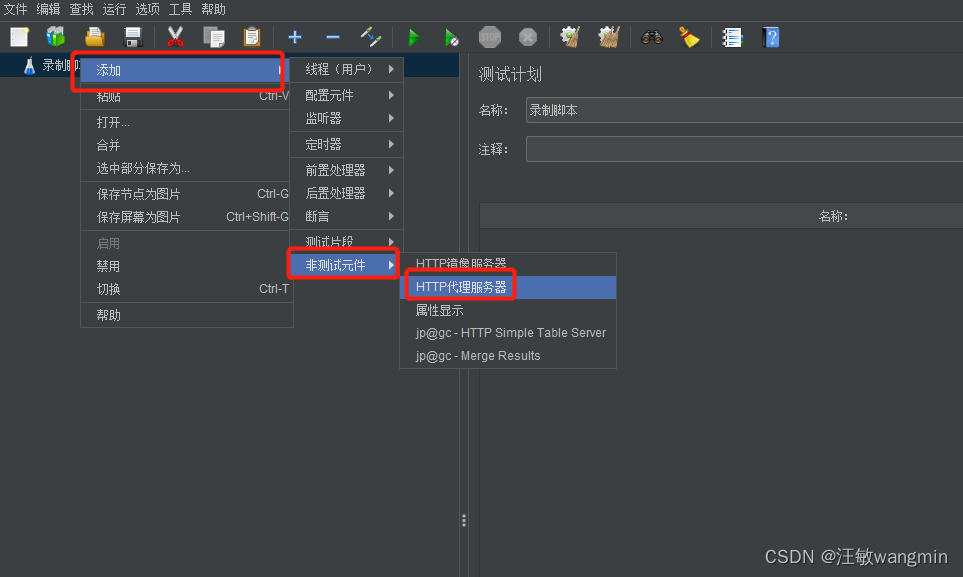

jmeter - record script

随机推荐

anno arm移植Qt环境后,编译正常,程序无法正常启动问题的记录

毕昇编译器优化:Lazy Code Motion

Self-taught software testing, how far can I go out to find a job?

leetcode300.最长递增子序列(动态规划)

C语言知识补充

动态RDLC报表(三)

神秘的程序员(20-30)

论文解读:Deep-4MCW2V:基于序列的预测指标,以鉴定大肠杆菌中的N4-甲基环胞嘧啶位点

About the common Hook encapsulation of DOM (2)

Engaged in software testing for a year, only basic functional testing, how to further study?

Unity Webgl与JS相互交互 Unity 2021.2之后的版本

怎样选择一个好的SaaS知识库工具?

Logic unauthorized and horizontal and vertical unauthorized payment tampering, verification code bypass, interface

LeetCode笔记:Weekly Contest 305

win10 uwp 模拟网页输入

Flink on Yarn

Flink运行架构

动手学深度学习_风格迁移

动手学深度学习_全卷积网络 FCN

uniapp 实现底部导航栏tabbar