当前位置:网站首页>UART串口协议

UART串口协议

2022-08-07 05:13:00 【FPGA小白758】

1.串口简介

通用异步收发传输器(Universal Asynchronous Receiver/Transmitter),通常称作UART。UART 是一种通用的数据通信协议,也是异步串行通信口(串口)的总称,它在发送数据时将并行数据转换成串行数据来传输,在接收数据时将接收到的串行数据转换成并行数据。它包括了 RS232、RS499、RS423、RS422 和 RS485 等接口标准规范和总线标准规范。

特点:异步、全双工,串行口.先传低位再传高位

2.RS232 通信协议简介

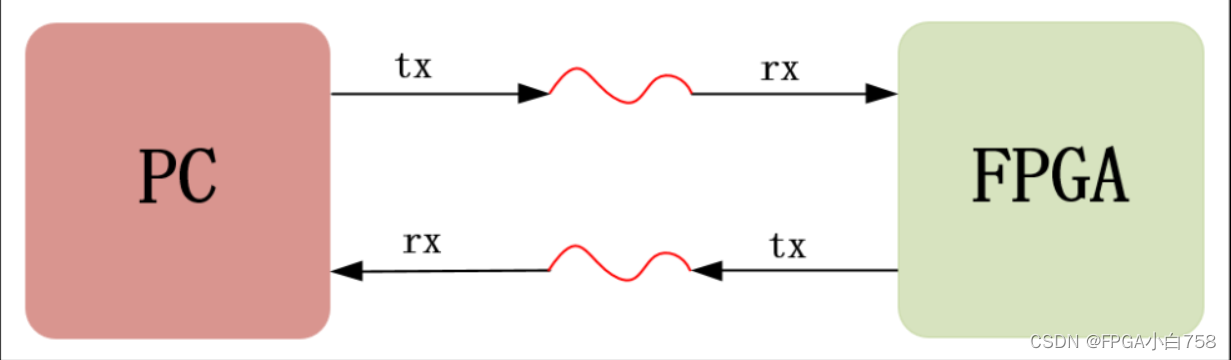

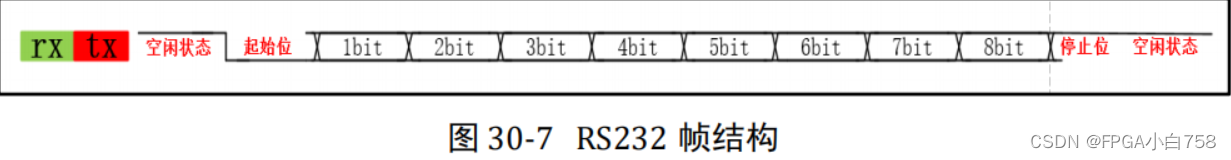

1、RS232 是 UART 的一种,没有时钟线,只有两根数据线,分别是 rx 和 tx,这两根线都是 1bit 位宽的。其中 rx 是接收数据的线,tx 是发送数据的线。

波特率:在信息传输通道中,携带数据信息的信号单元叫码元(因为串口是 1bit 进行传输的,所以其码元就是代表一个二进制数),每秒钟通过信号传输的码元数称为码元的传输速率,简称波特率,常用符号“Baud”表示,其单位为“波特每秒(Bps)”。串口常见的波特率有 4800、9600、115200 等,我们选用 9600 的波特率进行串口章节的讲解。

比特率:每秒钟通信信道传输的信息量称为位传输速率,简称比特率,其单位为“每秒比特数(bps)”。比特率可由波特率计算得出,公式为:比特率=波特率 * 单个调制状态对应的二进制位数。如果使用的是 9600 的波特率,其串口的比特率为:9600Bps * 1bit= 9600bps。

// FPGA : 小梅哥AC620

// EDA : Quartus II 13.0sp1 (64-bit) and ModelSim SE-64 10.5

// Author : FPGA小白758 https://blog.csdn.net/q1594?spm=1010.2135.3001.5343

// File : uart_rx.v

// Create : 2022-05-04 22:30:02

// Revise : 2022-05-04 22:30:03

// Editor : sublime text3, tab size (4)

// -----------------------------------------------------------------------------

module uart_rx(

input wire sclk,

input wire rst_n,

input wire rx,

output reg [7:0] po_data,

output reg po_flag

);

parameter CNT_BAUD_MAX = 1_000_000_000 / 1562500 / 20 - 1;

parameter CNT_HALF_BAUD_MAX = CNT_BAUD_MAX / 2;

reg rx1,rx2,rx2_reg;

reg rx_flag;

reg [12:0] cnt_baud;

reg bit_flag;

reg [3:0] bit_cnt;

//打拍

always @(posedge sclk) begin

{

rx2_reg,rx2,rx1}<={

rx2,rx1,rx};

end

//数据传输标志

always @(posedge sclk or negedge rst_n) begin

if (rst_n == 1'b0) begin

rx_flag <= 1'b0;

end

else if (bit_cnt == 4'd8 && bit_flag == 1'b1) begin

rx_flag <= 1'b0;

end

else if (rx2_reg == 1'b1 && rx2 == 1'b0) begin

rx_flag <= 1'b1;

end

end

//波特率计数器

always @(posedge sclk or negedge rst_n) begin

if (rst_n == 1'b0) begin

cnt_baud <= 'd0;

end

else if (rx_flag == 1'b0) begin

cnt_baud <= 'd0;

end

else if (rx_flag == 1'b1 && cnt_baud == CNT_BAUD_MAX) begin

cnt_baud <= 'd0;

end

else if (rx_flag == 1'b1) begin

cnt_baud <= cnt_baud + 1'b1;

end

end

//采样标志位

always @(posedge sclk or negedge rst_n) begin

if (rst_n == 1'b0) begin

bit_flag <= 1'b0;

end

else if (rx_flag == 1'b1 && cnt_baud == CNT_HALF_BAUD_MAX) begin

bit_flag <= 1'b1;

end

else begin

bit_flag <= 1'b0;

end

end

//采样数量计数

always @(posedge sclk or negedge rst_n) begin

if (rst_n == 1'b0) begin

bit_cnt <= 'd0;

end

else if (bit_flag == 1'b1 && bit_cnt == 'd8) begin

bit_cnt <= 'd0;

end

else if (bit_flag == 1'b1) begin

bit_cnt <= bit_cnt + 1'b1;

end

end

//移位寄存

always @(posedge sclk or negedge rst_n) begin

if (rst_n == 1'b0) begin

po_data <='d0;

end

else if (bit_cnt >= 4'd1 && bit_flag == 1'b1) begin

po_data <= {

rx2_reg,po_data[7:1]};

end

end

//结束标志

always @(posedge sclk or negedge rst_n) begin

if (rst_n == 1'b0) begin

po_flag <= 1'b0;

end

else if (bit_cnt == 4'd8 && bit_flag == 1'b1) begin

po_flag <= 1'b1;

end

else begin

po_flag <= 1'b0;

end

end

endmodule

边栏推荐

- 2021-01-29

- 自定义分页

- 「SwiftUI」TabView中添加NavigationBarItems

- dgiot-dtu realizes PLC data acquisition and real-time viewing on the cloud

- 多个Excel打包成zip导出

- DCDC low pressure booster regulated dc high voltage 12 v24v turn - 50 v100v110v150v200v250v300v350v400v500v negative voltage output

- 软删除源码分析

- 谭浩强第五版第三章课后习题

- 防抖和节流

- pta 天梯赛 L1-020 帅到没朋友

猜你喜欢

随机推荐

SSM整合------全过程

SSM的简单整合

打印sql各种方法汇总

腾讯云部署

Paper Time 回顾|MB2:为自治数据库建立行为模型

全网最全超详细.htaccess语法讲解

uniapp的map地图组件介绍

2022/7/2 Jenkins详细教程

正则表达式笔记

DGIoT任务调度

2021-01-29

pymysql格式化输入的一些问题

转速信号变送模块 频率转电压电流信号变换器

DGIOT's first lightweight IoT open source platform in China - one-click deployment of TLS certificates

SQL 改写系列六:谓词推导

实现串口通信数据帧打包与解析,串口通信可靠传输,屡试不爽的数据封包与状态机数据解析程序

3*3卷积核生成

DIN 11 HVI标准信号0-20mA/ 4-20mA等转高电压高电流0-165mA /0-200mA/0-15V/0-20V等输出放大转换器

5路热电阻温度信号转RS-485/232,温度采集转换模块 YL25

多个Excel打包成zip导出