当前位置:网站首页>Fundamentals of digital electronic technology 5.1 overview of trigger and 5.2 SR latch

Fundamentals of digital electronic technology 5.1 overview of trigger and 5.2 SR latch

2022-04-21 19:08:00 【FPGA Bridge】

Preface

《 Fundamentals of digital electronic technology 》 The first 5.1 and 5.2 Section learning notes

《 Digital logic circuit design 》 The first 4.1 Section learning notes

5.1 Trigger Overview

Digital circuits are divided into combinational logic circuits and sequential logic circuits .

Combinational logic circuit consists of gate circuit , The output state at a certain time is only related to the input state at that time , It has nothing to do with the original state of the circuit , No memory function .

The sequential logic circuit consists of a latch 、 Flip flops and registers and other units , The output state at a certain time is not only related to the input state at that time , And it is related to the original state of the circuit , With memory function .

Trigger is the basic unit of sequential logic circuit , Be able to store 1 The basic unit circuits of bit binary signals are collectively referred to as flip flops (Flip-Flop). To realize memory 1 Bit binary signal function , The trigger has the following two basic characteristics :

It has two stable states that it can maintain itself , Used to represent the logical state 0 and 1.

Under the operation of trigger signal , According to the input signal, the trigger can be set to 0 or 1.

Classification of triggers :

According to the trigger mode : Level trigger 、 Pulse triggered 、 edge-triggered

According to the principle of storing data : Static trigger 、 Dynamic trigger

According to the stable working state : Two state trigger 、 Monostable trigger 、 No steady state trigger ( Multi resonant oscillator )

According to the structure of the circuit : Basic trigger 、 Synchronous trigger 、 Master slave trigger 、 Edge trigger, etc

According to the logical function :SR trigger 、JK trigger 、T trigger 、D trigger 、 Schmidt trigger 、 Multivibrator

Static trigger : It stores data by self-locking of circuit state ( Main learning );

Dynamic trigger :MOS A device for storing data by storing charge on the output capacitor of the tube grid , The charge of a capacitor has 0 state , nothing 1 state .

5.2 SR Latch

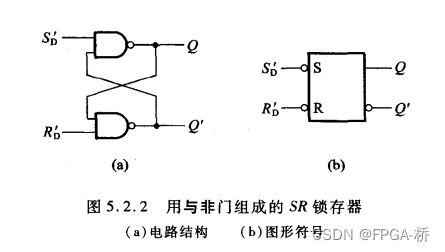

SR Latch (set-Reset Latch) It is the basic structure of various trigger circuits . It can maintain a stable state by itself , And the setting can be completed according to the output signal 0 or 1 state , No trigger signal is required to trigger . There is no self holding function in the gate circuit .

The picture below shows SR Circuit structure of latch :

notes : because Q And Q' It's the opposite , Therefore, only Q The state of indicates the state of the latch , In the following table Q by 0 Indicates that the latch status is 0, here Q=0,Q'=1; In the following table Q by 1 Indicates that the latch status is 1, here Q=1,Q'=0;

In the following table Q Indicates the current state of the latch ,Q* Indicates the next state of the latch

版权声明

本文为[FPGA Bridge]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204211907020974.html

边栏推荐

猜你喜欢

随机推荐

Database advanced learning: introduction to index and BTREE, B + tree, hash

Analysis of service registration source code of Nacos

MySQL数据库索引面试题(最新版)

el-tabs中套用el-tooltip(气泡文字提示框)

Context in programming

In the El input search in ement, the matching input suggestions after input must have the value attribute

The difference between null and undefined

Which futures trading platform is the safest? How do I choose?

How to call the login, playback address and video playback interface of easycvr platform?

Distributed transaction Foundation

Seata(一) 服务配置以及启动

医疗机器人在AI领域的广泛应用

Big guys, why is it 10 times slower to call functions in this way?

XD signal and system

2022.04.21 (lc_56_consolidation interval)

WebRTC视频无法播放,如何在EasyCVR添加UDP打洞程序?

MySQL (III) index optimization and case analysis

How to classify cosmetics in the management system?

How to set the TS slice file size for the new kernel version of easycvr?

Svg series - 1, entry level operation

![[ES6] let, const, deconstruction assignment, template string](/img/42/1e57b501799cc019cf652b8aaf5999.gif)