当前位置:网站首页>Verilog语法基础HDL Bits训练 09

Verilog语法基础HDL Bits训练 09

2022-08-08 13:06:00 【南邮学渣】

文章目录

Circuits:Karnaugh Map to Circuit

一、3-variable

本小节讲通过卡诺图化简得出表达式

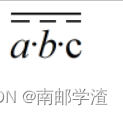

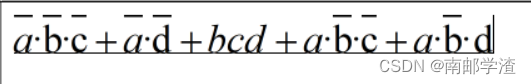

本题化简完毕是

- RTL代码

module top_module(

input a,

input b,

input c,

output out );

assign out = ~(~a & ~b & ~c);

endmodule

- 仿真波形图

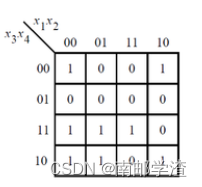

二、4-variable

卡诺图化简结果为

- RTL代码

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = ( ~a & ~b & ~c) | (a & ~b & ~c) | (~a & ~d) | (b & c & d) | (a & ~b & d);

endmodule

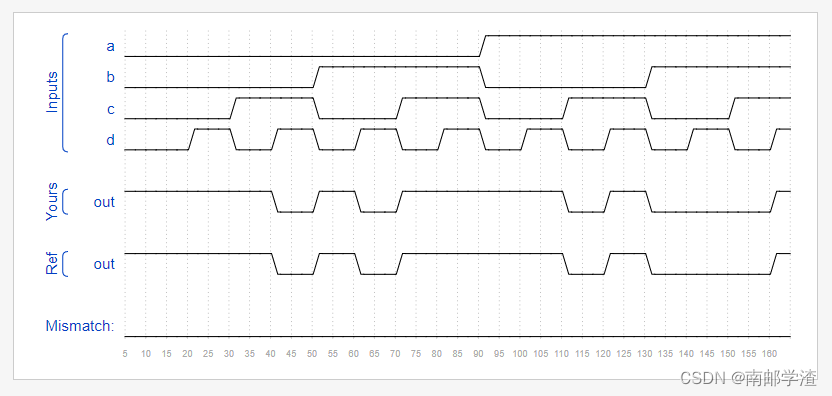

- 仿真波形图

三、4-variable

卡诺图化简为(要注意看外一行的数字,有陷阱)

- RTL代码

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = a | (~b & c);

endmodule

- 仿真波形图

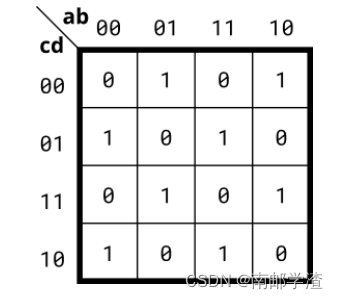

四、4-variable

- RTL代码

module top_module(

input a,

input b,

input c,

input d,

output out );

assign out = (~a&~b&~c&d)|(~a&b&~c&~d)|(a&b&~c&d)|(a&~b&~c&~d)|(~a&b&c&d)|(a&~b&c&d)|(~a&~b&c&~d)|(a&b&c&~d);

endmodule

- 仿真波形图

五、Minimum SOP and POS

SOP是以1为中心圈卡诺圈,POS是以0为中心圈卡诺圈,二者用的是同一张卡诺图。

- RTL代码

module top_module (

input a,

input b,

input c,

input d,

output out_sop,

output out_pos

);

assign out_sop = (c & d) | (~a & ~b &c);

assign out_pos = c & (~b | d) & (~a | d);

endmodule

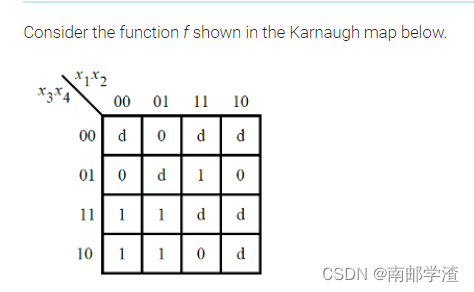

六、Karnaugh map

- RTL代码

module top_module (

input [4:1] x,

output f );

assign f = (x[2] & x[4]) | (x[3] & x[4]) | (~x[1] & x[3]);

endmodule

七、Karnaugh map

- RTL代码

module top_module (

input [4:1] x,

output f

);

assign f = (~x[2] & ~x[4]) | (~x[1] & x[3]) | (x[2] & x[3] & x[4]);

endmodule

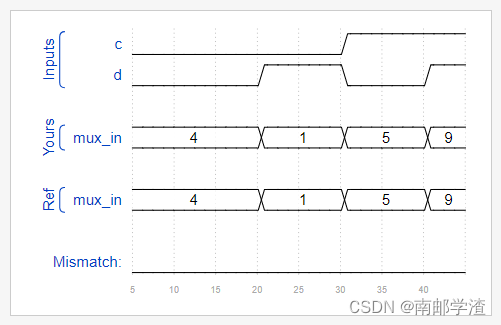

八、K-map implemented with a multiplexer

- RTL代码

module top_module (

input c,

input d,

output [3:0] mux_in

);

assign mux_in[0] = c | d;

assign mux_in[1] = 1'b0;

assign mux_in[2] = ~d;

assign mux_in[3] = c & d;

endmodule

- 仿真波形图

边栏推荐

- “自降估值”3个亿的咖啡独角兽要IPO了

- Jenkins - Introduction to Continuous Integration (1)

- 【第2天】SQL快速入门-条件查询(SQL 小虚竹)

- sample函数—R语言

- 南非 KMP 媒体集团实施了 DMS(文档管理系统)使流程数字化,员工可以再次专注于他们的实际任务,提供了效率

- R语言patchwork包将多个ggplot2可视化结果组合起来、使用plot_annotation函数以及tag_level参数为组合图添加自定义编码序列(字符向量列表)

- 2022-08-03

- node中package解析、npm 命令行npm详解,node中的common模块化,npm、nrm两种方式查看源和切换镜像

- 【SSR服务端渲染+CSR客户端渲染+post请求+get请求+总结】三种开启服务器的方法总结

- 史上最全JVM性能调优:线程+子系统+类加载+内存分配+垃圾回收

猜你喜欢

随机推荐

直接选择排序

xxd命令(反编译、二进制文件转十六进制文件)

将小部分源码设计精髓带入到开发中来(工厂模式、适配器模式、抽象类、监听器)

SQL INSERT INTO and INSERT INTO the SELECT statement

(7) FlinkSQL kafka data written to the mysql way 2

【软考 系统架构设计师】软件架构设计⑥ 软件产品线

医药行业转型发展,探索数字化供应链升级之道

面试官问你什么是长轮询?

八月粉丝福利来了!大疆手机云台你爱了吗?

逐步手撕轮播图3(分步教程)

sample函数—R语言

[C language] Dynamic memory management

C语言小项目 -- 通讯录(静态版+动态版+文件版)

【重构map】【重构filter】【重构Some】【重构reduce方法】【重构flat函数】

【软考 系统架构设计师】软件架构设计⑦ 构件与中间件技术

UnsatisfiedDependencyException: Error creating bean with name ‘

移位运算、位运算、逻辑运算相关知识点及笔试题

Using Flask and Celery to push real-time/timed messages asynchronously in Win10 environment (Socket.io)/The latest strategy in 2020

金融行业数智化供应链管理系统:多维度评估分析供应商,赋能智能金融变革

MeterSphere--开源持续测试平台