当前位置:网站首页>[FPGA] Design Ideas - I2C Protocol

[FPGA] Design Ideas - I2C Protocol

2022-08-11 03:42:00 【Spring Breeze Preface】

一、模块框图

二、状态转移图

三、端口列表

1、控制模块:

input clk ,

input rst_n ,

input rd_en ,//读请求,按键控制

input [7:0] din ,//接收串口的数据

input din_vld ,//Serial data completion flag

input [7:0] rd_data ,//Receive data from the interface

input done ,//rd_data数据完成标志

input ready ,//Serial port idle flag

output reg [7:0] dout ,//Read data out to the serial port

output reg dout_vld,//Serial data completion flag

output reg [3:0] cmd ,//Send data to the interface

output reg req ,//Send a request to the interface

output reg [7:0] wr_data ,//Send data to the interface

2、接口模块

input clk ,

input rst_n ,

//控制模块

input req ,//接收请求

input [3:0] cmd ,//接收命令

input [7:0] wr_data ,//Receive data from the control module

output done ,//A byte transfer complete flag

output reg [7:0] rd_data ,//Pass the read data into the control module

//output reg slave_ack ,//写入数据后EEPROM应答信号

//eeprom

input i2c_sda_i ,//EEPROMSerial data passed to the interface module

output reg i2c_scl ,//I2C时钟

output reg i2c_sda_oe ,//输出使能信号

output reg i2c_sda_o //The interface module arrivesEEPROM的串行数据

四、设计思路

1、控制模块

(1)状态机设计

assign idle2rd_req = state_c == IDLE && rd_en;

assign idle2wr_req = state_c == IDLE && (wfifo_usedw > WR_LEN - 2);

assign rd_req2rd_wait = state_c == RD_REQ && (1'b1);

assign rd_wait2rd_req = state_c == RD_WAIT && (done & cnt_byte < RD_LEN - 1);

assign rd_wait2done = state_c == RD_WAIT && end_cnt_byte;

assign wr_req2wr_wait = state_c == WR_REQ && (1'b1);

assign wr_wait2wr_req = state_c == WR_WAIT && (done & cnt_byte < WR_LEN - 1);

assign wr_wait2done = state_c == WR_WAIT && end_cnt_byte;

assign done2idle = state_c == DONE && (1'b1);

(2)Byte counter design

assign add_cnt_byte = (state_c == RD_WAIT | state_c == WR_WAIT) & done ;

assign end_cnt_byte = add_cnt_byte && cnt_byte == ((state_c == WR_WAIT)?(WR_LEN-1):(RD_LEN-1)) ;

(3)设计一个task,用于发送请求,命令,数据

读状态时:

第0字节发送(请求,{开始命令,写命令},{I2C器件地址,写请求});

第1字节发送(请求,写命令,寄存器地址};

The last byte is sent(请求,{写命令,停止命令},wfifo中的输出数据);

写状态时:

第0字节发送(请求,{开始命令,写命令},{I2C器件地址,写请求});

第1字节发送(请求,写命令,寄存器地址};

第2字节发送(请求,{开始命令,写命令},{I2C器件地址,读请求}};

The last byte is sent(请求,{读命令,停止命令},0);

(4)Register address design

读地址:

初始为0,Whenever a complete read operation completes(即rd_wait2done),The number of data read in by the address auto-increment(即rd_addr <= rd_addr + RD_LEN - 3)

写地址:

初始为0,Whenever a complete write operation completes(即wr_wait2done),The number of data written by the address auto-increment(即wr_addr <= wr_addr + WR_LEN - 2)

(5)Output to serial port data design

即dout 与 dout_vld

dout等于rfifo的输出数据

dout_vld等于rfifo的读请求

(6)FIFO设计

数据宽度为8,Depth is default256

wfifo:

The data input is the data input from the serial port

读请求:Write status and begin to have data

wfifo_rdreq = state_c == WR_WAIT & done & cnt_byte > 1;

写请求:非满且输入有效

wfifo_wrreq = ~wfifo_full && din_vld;

rfifo:

The data input is the data input from the interface

读请求:Not empty and the serial port is free

rfifo_rdreq = ready && ~rfifo_empty;

写请求:Read status and begin to have data

rfifo_wrreq = ~rfifo_full && state_c == RD_WAIT && done && cnt_byte >2;

2、接口模块

(1)状态机设计

assign idle2start = state_c == IDLE && (req && (cmd & `CMD_START));

assign idle2write = state_c == IDLE && (req && (cmd & `CMD_WRITE));

assign idle2read = state_c == IDLE && (req && (cmd & `CMD_READ));

assign start2write= state_c == START && (end_cnt_bit && (command & `CMD_WRITE));

assign start2read = state_c == START && (end_cnt_bit && (command & `CMD_READ));

assign write2rack = state_c == WRITE && end_cnt_bit;

assign rack2stop = state_c == RACK && (end_cnt_bit && (command & `CMD_STOP));

assign rack2idle = state_c == RACK && (end_cnt_bit && (command & `CMD_STOP) == 0);

assign read2sack = state_c == READ && end_cnt_bit;

assign sack2stop = state_c == SACK && (end_cnt_bit && (command & `CMD_STOP));

assign sack2idle = state_c == SACK && (end_cnt_bit && (command & `CMD_STOP) == 0);

assign stop2idle = state_c == STOP && end_cnt_bit;

(2)计数器设计

I2C时钟

非IDLE状态开启,

every time250every system clock cycle expires.

bit时钟

每当I2CTurns on once when the clock ends,

结束状态为:读/Write the status down8bit,The rest of the status is recorded1bit.

(3)I2C时钟设计

初始为1,跳出IDLEPulled low after the state,记到I2Chalf the clock(125)时拉高,Finish oneI2Cpulled low after the clock.

(4)I2C输出设计

初始为1

起始状态,I2CPull the signal high in the middle of the clock low level,Make sure the start signal can be detected,I2CPull the signal low in the middle of the clock high

写状态且I2CWhen the clock is low in the middle,Convert the incoming data from the control module to parallel-serial conversion and output

Send a reply signal andI2CWhen the clock is low in the middle,If there is a stop command,Then send a high level,Otherwise send low level.

结束状态,I2CPull the signal low in the middle of the clock low level,Make sure that the stop signal can be detected,I2CPull the signal high in the middle of the clock high level.

(5)I2Coutput enable design

开始状态、结束状态、写状态、Transmit acknowledgment status is high,其余为低电平.

(6)接收EEPROM数据设计

read status andI2CWhen the clock is high in the middle,串并转换

(7)接收EEPROM应答设计

Receive reply andI2CWhen the clock is high in the middle,The reply signal is equal to the input signal.

边栏推荐

- MongoDB 基础了解(二)

- 基于改进YOLOv5轻量化的烟火检测

- I didn't expect MySQL to ask these...

- The development of the massage chair control panel makes the massage chair simple and intelligent

- Is Redis old?Performance comparison between Redis and Dragonfly

- oracle的基数会影响到查询速度吗?

- Leetcode 450. 删除二叉搜索树中的节点

- 互换性测量技术-几何误差

- E-commerce project - mall time-limited seckill function system

- [BX] and loop

猜你喜欢

QueryDet: Cascading Sparse Query Accelerates Small Object Detection at High Resolution

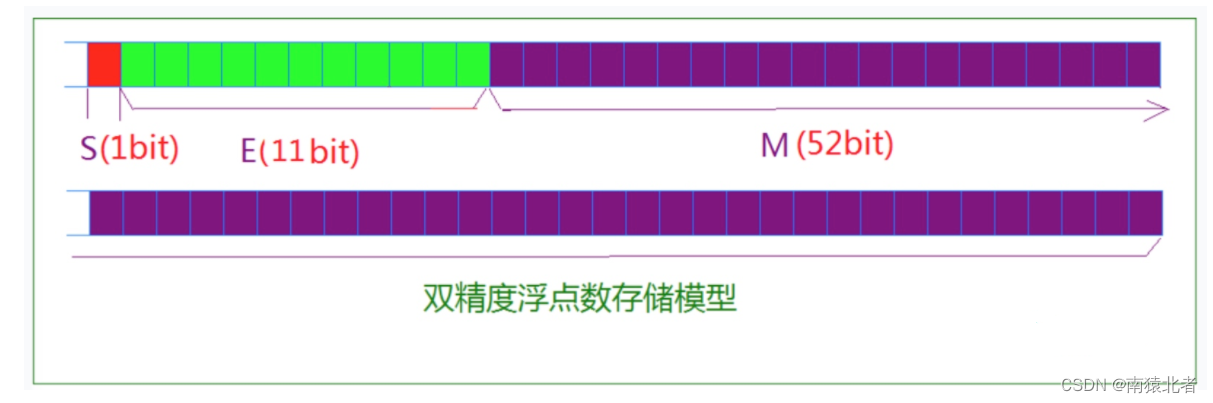

浮点数在内存中的存储方式

![[DB operation management/development solution] Shanghai Daoning provides you with an integrated development tool to improve the convenience of work - Orange](/img/3e/06654c5ad976bad53bf0aa4390e7e9.png)

[DB operation management/development solution] Shanghai Daoning provides you with an integrated development tool to improve the convenience of work - Orange

【FPGA】SDRAM

STC8H development (15): GPIO drive Ci24R1 wireless module

The most unlucky and the luckiest

Multi-serial port RS485 industrial gateway BL110

【FPGA】day22-SPI协议回环

Qnet弱网测试工具操作指南

云平台下ESB产品开发步骤说明

随机推荐

Watch to monitor

Get the length of the linked list

Detailed explanation of VIT source code

The last update time of the tables queried by the two nodes of the rac standby database is inconsistent

大马驮2石粮食,中马驮1石粮食,两头小马驮一石粮食,要用100匹马,驮100石粮食,如何分配?

互换性与测量技术——表面粗糙度选取和标注方法

Uni - app - access to Chinese characters, pinyin initials (according to the Chinese get pinyin initials)

Talk about the understanding of RPC

Element's BFC attribute

Build Zabbix Kubernetes cluster monitoring platform

互换性测量与技术——偏差与公差的计算,公差图的绘制,配合与公差等级的选择方法

你不知道的 console.log 替代品

Ten Advanced Concepts of SQL Development

The impact of programmatic trading and subjective trading on the profit curve!

分布式和集群的区别和联系

【C语言】入门

CSDN 博客更换皮肤

How does MSP430 download programs to the board?(IAR MSPFET CCS)

Multi-merchant mall system function disassembly 26 lectures - platform-side distribution settings

树莓派入门(5)系统备份