当前位置:网站首页>Riscv MMU overview

Riscv MMU overview

2022-04-23 13:15:00 【pwl999】

1. Background

Linux Memory management contains a lot , The main knowledge points can be referred to Linux Mem. This article only describes one of the knowledge points Paging and MMU.

This paper is based on Quan Zhi D1 For example , Contains one from brother Flathead Riscv64 Of CPU IP-Core, Code name C906. For specific manuals, please refer to C906 User's Manual .

2. X86_64

The same is 64bit cpu,x86_64 Support 48bit and 57bit Two linear address modes , They correspond to each other 4level and 5level mmu mapping :

| Linear address | mmu Hierarchy | Linux user address space | Linux kernel address space |

|---|---|---|---|

| Sv48 (48bit) | 4level: pgd→pud→pmd→pte→page(4k) | 0x00000000 00000000 - 0x00007FFF FFFFFFFF | 0xFFFF8000 00000000 - 0xFFFFFFFF FFFFFFFF |

| Sv57 (57bit) | 5level: pgd→p4d→pud→pmd→pte→page(4k) | 0x00000000 00000000 - 0x00FFFFFF FFFFFFFF | 0xFF000000 00000000 - 0xFFFFFFFF FFFFFFFF |

X86_64 Use CR3 Register to save MMU The root address of the mapping table .

For more details, please refer to Paging addressing (Paging) Detailed explanation of mechanism and Detailed layout of kernel address space .

3. C906

Sv39/Sv48/Sv57/Sv64 These models riscv64 All support . because C906 The designed application scenario does not require so much memory resources , at present C906 Only support Sv39 Pattern , Corresponding 3level mmu mapping .

| Linear address | mmu Hierarchy | Linux user address space | Linux kernel address space |

|---|---|---|---|

| Sv39 (39bit) | 3level: pgd→pmd→pte→page(4k) | 0x00000000 00000000 - 0x0000003F FFFFFFFF | 0xFFFFFFC0 00000000 - 0xFFFFFFFF FFFFFFFF |

and x86 CR3 similar ,riscv Use SATP Register to save MMU The root address of the mapping table . The specific mapping relationship is as follows :

3.1 SATP register

SATP The specific format of the register is shown in the figure below :

The analysis of specific fields is as follows :

- Mode - MMU Address translation mode

| Value | Name | Description |

|---|---|---|

| 0 | Bare | No translation or protection |

| 1-7 | - | Reserved |

| 8 | Sv39 | Page-based 39-bit virtual addressing |

| 9 | Sv48 | Page-based 48-bit virtual addressing |

| 10 | Sv57 | Reserved for page-based 57-bit virtual addressing |

| 11 | Sv64 | Reserved for page-based 64-bit virtual addressing |

| 12-15 | - | Reserved |

When Mode by 0 when ,MMU close .C906 Only support MMU Shut down and Sv39 Two modes .

- ASID – At present ASID. Indicates the of the current program ASID Number .

- PPN – Hardware backfill root PPN. The first level hardware backfill is used PPN (Phsical Page Number).

3.2 Page table entry

pgd/p4d/pud/pmd/pte The size of table items contained in the page table of each level is 8 bytes, Every 4k page Memory can only hold 512 Page table items , Therefore, the addressing range of page table at each level is 9bit.

c906 The specific page table item format is as follows :

The analysis of specific fields is as follows :

-

PPN – Page table physical address .PPN[i] Respectively represent the corresponding... When the three-level page table is converted PPN value .

-

RSW – Reserved for Software. Bits reserved for the software to customize the page table function .default by 2’b0.

-

D – Dirty

D Position as 1 when , Indicates whether the page has been rewritten .

1’b0: The current page is not written / Don't write ;

1’b1: The current page has been written / Can write .

This bit is in C906 Hardware implementation and W Properties are similar to . When D Position as 0 when , Writing to this page will trigger Page Fault (store)

abnormal , By configuring... In the exception service program D Bit to maintain whether the page has been rewritten / A writable definition . This bit is reset to 0. -

A – Accessed

A Position as 1 when , Indicates that the page has been visited . by 0 I haven't been visited , Access to the page table triggers Page Fault ( Corresponding visit

type ) Exception and set the field to 1. This bit is reset to 0. -

G – Global

Global page id , The current page can be shared by multiple processes , This bit is reset to 0.

1’b0: Unshared pages , Process number ASID private ;

1’b1: Share page . -

U – User

User mode is accessible , This bit is reset to 0.

1’b0: User mode is not accessible , When user mode accesses , Out page fault abnormal ;

1’b1: User mode is accessible . -

X : Executable ;W : Can write ;R : Can be read .

XRW Permission specification

| X | W | R | Meaning |

|---|---|---|---|

| 0 | 0 | 0 | Pointer to next level of page table |

| 0 | 0 | 1 | Read-only page |

| 0 | 1 | 0 | Reserved for future use |

| 0 | 1 | 1 | Read-write page |

| 1 | 0 | 0 | Execute-only page |

| 1 | 0 | 1 | Read-execute page |

| 1 | 1 | 0 | Reserved for future page |

| 1 | 1 | 1 | Read-write-execute page |

In violation of the XWR Permission will trigger Page Fault abnormal .

- V – Valid

Indicates whether the physical pages are allocated in memory , Visit one V by 0 The page of , Will trigger Page Fault abnormal . This bit is reset to 0.

1’b0: The current page is not assigned ;

1’b1: The current page has been assigned .

C906 The extended page properties are as follows

-

SO– Strong order

Used to indicate memory requirements for access order :

1’b0: no strong order(Normal-memory);

1’b1: strong order(Device).

The default is no strong order. -

C – Cacheable

1’b0: Non-cacheable;

1’b1: Cacheable.

The default is Non-cacheable. -

B – Buff er

1’b0: Non-bufferable ;

1’b1: Bufferable .

The default is Non-bufferable . -

Sec (T – Trustable)

Used to represent whether the page belongs to the trusted world or the untrusted world , This bit is only available when TEE It makes sense to expand ,C906 This bit in is undefined .

1’b0: Non-trustable;

1’b1: Trustable;

The default is Trustable.

3.3 Huge Page

x86 A... Is used in the page table entry of PS Bit to identify whether the current is huge page, If I set this bit, that pud Can directly address 1G Large page of ,pmd Can directly address 2M Large page of .

c906 There are no entries in the table PS This bit, It is to use XRW 3 individual bit To identify whether the current page is the last level of the page table .

- If

XRW=000, Is the middle level page table - If

XRW!=000, Is the last level of page table .pgdby 1G Big page ,pmdby 2M Big page .

3.4 ASID

ASID (Adress Space ID) The main purpose of is to give mmu The cache to tlb For labeling , If... Is set in the page table entry G – Global It is not affected by the overall situation ASID Constraints .

stay Linux Each user has its own address in the process space , Have an independent mmu The mapping relationship . So when the process switches mmu Mapping also requires switching .

ASID There are two main functions :

- Reduce tlb Global refresh of .

- Do permission isolation without refreshing .

ASID The detailed principle can refer to : Kernel page table isolation (KPTI) Detailed explanation .

4. Linux Yes mmu Common operations of

linux In the following scenarios, the mmu To operate , I won't go into details here :

| scene | description |

|---|---|

| fork() | Simple replication mmu The mapping relationship |

| execv() | Recreate the user state vma mapping |

| mmap() | Create a new paragraph vma mapping |

| task_switch | Switch between different address spaces mmu mapping |

| page_fault() | according to vma Mapping creates the actual mmu mapping |

| mprotect() | change vma and mmu Memory properties |

| system call | In the open KPTI Under the circumstances , It's going to happen mmu Switch |

| mem reclaim | After reclaiming file memory , Destroy the corresponding mmu mapping |

Reference documents

1.C906 User's Manual

2. Paging addressing (Paging) Detailed explanation of mechanism

3. Detailed layout of kernel address space

4.commit:RISC-V: Paging and MMU

5. Kernel page table isolation (KPTI) Detailed explanation

版权声明

本文为[pwl999]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204230612157590.html

边栏推荐

- CSDN College Club "famous teacher college trip" -- Hunan Normal University Station

- CMSIS cm3 source code annotation

- Mui close other pages and keep only the first page

- Example interview | sun Guanghao: College Club grows and starts a business with me

- MySQL 8.0.11下载、安装和使用可视化工具连接教程

- Esp32 vhci architecture sets scan mode for traditional Bluetooth, so that the device can be searched

- AUTOSAR from introduction to mastery 100 lectures (51) - AUTOSAR network management

- Translation of multi modal visual tracking: review and empirical comparison

- SQL exercise question 1

- three. JS text ambiguity problem

猜你喜欢

初鉴canvas,展示个小小的小案例

FatFs FAT32 learning notes

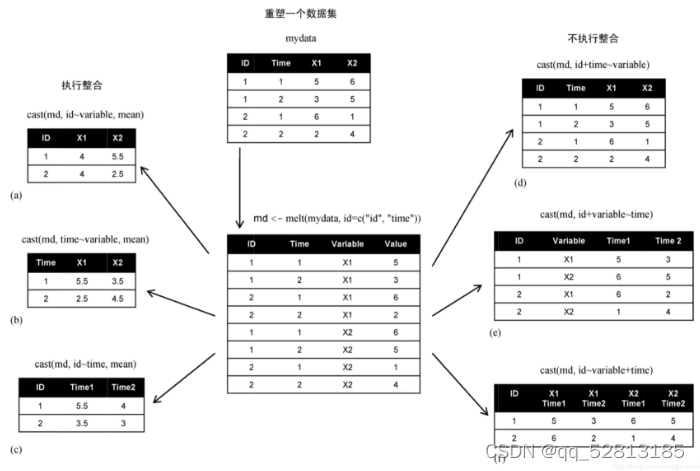

R语言中dcast 和 melt的使用 简单易懂

在 pytorch 中加载和使用图像分类数据集 Fashion-MNIST

叮~ 你的奖学金已到账!C认证企业奖学金名单出炉

mui + hbuilder + h5api模拟弹出支付样式

The difference between string and character array in C language

The first lesson is canvas, showing a small case

Learning notes of AMBA protocol

解决虚拟机中Oracle每次要设置ip的问题

随机推荐

9419 page analysis of the latest first-line Internet Android interview questions

The project file '' has been renamed or is no longer in the solution, and the source control provider associated with the solution could not be found - two engineering problems

解决Oracle中文乱码的问题

数据仓库—什么是OLAP

pyqt5 将opencv图片存入内置SQLlite数据库,并查询

mui picker和下拉刷新冲突问题

FFmpeg常用命令

Melt reshape decast long data short data length conversion data cleaning row column conversion

2020年最新字节跳动Android开发者常见面试题及详细解析

[quick platoon] 215 The kth largest element in the array

Playwright controls local Google browsing to open and download files

“湘见”技术沙龙 | 程序员&CSDN的进阶之路

GIS practical tips (III) - how to add legend in CASS?

Complete project data of UAV apriltag dynamic tracking landing based on openmv (LabVIEW + openmv + apriltag + punctual atom four axes)

uniapp image 引入本地图片不显示

将opencv 图片转换为字节的方式

Example interview | sun Guanghao: College Club grows and starts a business with me

「玩转Lighthouse」轻量应用服务器自建DNS解析服务器

这几种 VSCode 扩展是我最喜欢的

Mui wechat payment pit