当前位置:网站首页>串扰与防护

串扰与防护

2022-08-09 04:00:00 【Risehuxyc】

1、什么是串扰

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

串扰是信号完整性中最基本的现象之一,在板上走线密度很高时串扰的影响尤其严重。我们知道,线性无缘系统满足叠加定理,如果受害线上有信号的传输,串扰引起的噪声会叠加在受害线上的信号,从而使其信号产生畸变。

2、串扰是怎么引起的?

串扰是由电磁耦合引起的,耦合分为容性耦合和感性耦合两种。

串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望

的电压噪声。

容性耦合是由于干扰源(Aggressor)上的电压变化在被干扰对象(Victim)上

引起感应电流从而导致的电磁干扰;

而感性耦合则是由于干扰源上的电流变化产生的磁场在被干扰对象上引起感应电压从而导致的电磁干扰。因此,信号通过一导体时会在相邻的导体上引起两类不同的噪声信号:容性耦合信号和感性耦合信号。

感性耦合:

容性耦合:

3、降低串扰有哪些方法?

当两个网络靠近时,一个网络的电流变化会引起另外一个网络的电流变化,即产生串扰。也就是两个网络之间的电磁场耦合产生。串扰只在上升、下降沿电流变化时产生。

降低串扰的方法有:

1、选择慢变化边沿信号的器件。

2、选择输出摆幅和电流小的器件。

3、为了减少PCB上的线间耦合,可以采取:

(1)加大电源地层与信号层间距;

(2)提高相邻信号层间距;

(3)减少并行走线长度;

(4)增加线间距抑制;

(5)地线隔离

(6)在受害线上采用匹配技术;

(7)关键信号线走STRIPLINE

带状线:走在内层(stripline/double stripline),埋在PCB内部的带状走线,如下图所示

蓝色部分是导体,绿色部分是PCB的绝缘电介质,stripline是嵌在两层导体之间的带状导线。

因为stripline是嵌在两层导体之间,所以它的电场分布都在两个包它的导体(平面)之间,不会辐射出去能量,也不会受到外部的辐射干扰。但是由于它的周围全是电介质(介电常数比1大),所以信号在stripline 中的传输速度比在microstrip line中慢!

边栏推荐

猜你喜欢

A separate machine is connected to the spark cluster of cdh, and the task is submitted remotely (absolutely successful, I have tested it n times)

【Redis底层解析】字典类型

VS2019 compiles boost_1_79, generates 32-bit and 64-bit static libraries

全链路UI设计笔记

Mysql表打不开

HyperLynx(四)差分传输线模型

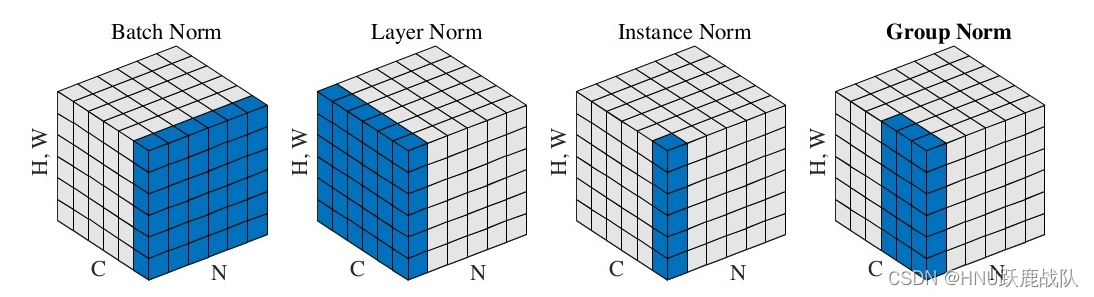

了解CV和RoboMaster视觉组(五)图像处理中使用的滤波器

Polygon zkEVM Prover

了解CV和RoboMaster视觉组(五)local-distribution汇聚方法

One Pass 1258 - Digital Pyramid (Dynamic Programming)

随机推荐

项目管理-挣值分析方法学习总结

卷积神经网络模型训练——入门理解

了解CV和RoboMaster视觉组(五)local-distribution汇聚方法

了解CV和RoboMaster视觉组(五)滤波器、观测器和预测方法

引用类型的浅拷贝与深拷贝小记

SQL JOIN上的and

理性预测,未来音视频开发前景将是这般光景

Kaggle(六)特征衍生技术 特征聚合

31 basic statistical concepts

进程和计划任务管理

《剑指offer》题解——week1(持续更新)

NanoDet代码逐行精读与修改(五.2)计算Loss

VsCode如何使用国内镜像下载

MutationObserver接口(一) 基本用法

Swift3.0 sets the background color and text color of the status bar

【每日一题】761. 特殊的二进制序列

状态机使用小结

uniapp uview uselect 时间选择 日期生成代码

leetcode 1805. 字符串中不同整数的数目

leetcode 5724. 绝对差值和