当前位置:网站首页>Quartus Prime硬件实验开发(DE2-115板)实验二功能可调综合计时器设计

Quartus Prime硬件实验开发(DE2-115板)实验二功能可调综合计时器设计

2022-04-23 13:54:00 【渣渣ye】

实验二功能可调综合计时器设计

- 实验目的

- 掌握QuartusII等实验工具的输入、综合、仿真、下载的使用方法

- 掌握DE2开发版的器件功能特性和使用方法

- 掌握Verilog HDL时序逻辑系统设计的主要方法和技术

- 掌握并应用EDA设计的方法和流程

- 预习要求

- 了解QuartusII等管教分配、下载的方法和流程

- 了解开发板输入、输出显示资源的工作特性

- 了解开发板设计、开发和测试的方法和流程

- 实验要求

设计一个可调的综合计时器。具体功能:

- 显示小时、分、秒,提供置零功能。显示在七段管或LCD屏幕上,可以考虑24/12小时模式切换功能。

- 能够对秒、分、小时进行分别修改,可以两位数整体修改或每位独立修改

- 整点报时功能,整点可以显示一定形式的LED来表示。

- 闹钟功能,设定特定时间,到时间以特定LED显示来显示闹钟。注意闹钟持续时间,也可以参考懒人闹钟模式。

初始操作与实验一几乎类似,详情可参考实验一链接:Quartus Prime硬件实验开发(DE2-115板)实验一CPU指令运算器设计_渣渣ye的博客-CSDN博客

需要注意的是,实验二内,需要替换管脚对应的数值,具体数值表链接如下:

FPGA硬件实验二功能可调综合计时器设计实验设计管脚设置-数据集文档类资源-CSDN下载

主体代码:

module shizhong(clkin,key0,hex0,hex1,hex2,hex3,hex4,hex5,hex6,hex7,KEY0,KEY1,key17,key16,key15,LEDR,LEDG,in,key14,key13,key12);

input clkin;

input key0,key17,key16,key15,key14,key13,key12;

input[6:1] in;

input KEY0,KEY1;

reg clk=0;

output reg[6:0] hex0,hex1,hex2,hex3,hex4,hex5,hex6,hex7;

output reg[7:0] LEDR,LEDG;

reg[7:0] out2,out3,out4,out5,out6,out7;

reg[7:0] second;

reg[7:0] minute;

reg[7:0] hour;

reg[7:0] second1;

reg[7:0] minute1;

reg[7:0] hour1;

integer N=25000000;

integer i=0;

reg[16:0] naozhong=0;

reg[16:0] s=0;

integer a=86400;

always@(posedge clkin) //分频

begin

if(i==N)

begin

i=0;

clk=~clk;

end

else i=i+1;

end

always@(posedge clk)

begin

if(key0) s=0; //置零

else

//计数

begin

//整点报时

if(s%3600==0)

begin

LEDR=8'b11111111;

end

else

begin

LEDR=8'b00000000;

s=(s+1)%a;

end

if(key17&&key16==0&&key15==0) //调整小时

begin

if(KEY0==0)s=(s+3600)%a;

else if(KEY1==0)s=(s-3600)%a;

else s=s%a;

end

else if(key17==0&&key16&&key15==0) //调整分钟

begin

if(KEY0==0)s=(s+60)%a;

else if(KEY1==0)s=(s-60)%a;

else s=s%a;

end

else if(key17==0&&key16==0&&key15) //调整秒

begin

if(KEY0==0)s=(s+1)%a;

else if(KEY1==0)s=(s-1)%a;

else s=s%a;

end

end

end

always@(key17,key16,key15,s)

begin

//闹钟

if(key17==1&&key16==1&&key15==1)

begin

naozhong = 0;

if(key12)naozhong=naozhong+in;

else if(key13)naozhong=naozhong+in*60;

else if(key14)naozhong=naozhong+in*3600;

else naozhong=naozhong;

second1=naozhong%60;

minute1=naozhong/60%60;

hour1=naozhong/3600;

out7=hour1/10;

out6=hour1%10;

out5=minute1/10;

out4=minute1%10;

out3=second1/10;

out2=second1%10;

hex7=seven(out7);

hex6=seven(out6);

hex5=seven(out5);

hex4=seven(out4);

hex3=seven(out3);

hex2=seven(out2);

hex1=7'b1111111;

hex0=7'b1111111;

end

else

begin

second=s%60;minute=s/60%60;hour=s/3600;

out7=hour/10;out6=hour%10;

out5=minute/10;out4=minute%10;

out3=second/10;out2=second%10;

hex7=seven(out7);

hex6=seven(out6);

hex5=seven(out5);

hex4=seven(out4);

hex3=seven(out3);

hex2=seven(out2);

hex1=7'b1111111;

hex0=7'b1111111;

if(s==naozhong)LEDG=8'b11111111;

else LEDG=8'b00000000;

end

end

function[6:0] seven;

input [7:0] din;

case(din)

4'h0:seven=7'b1000000;

4'h1:seven=7'b1111001;

4'h2:seven=7'b0100100;

4'h3:seven=7'b0110000;

4'h4:seven=7'b0011001;

4'h5:seven=7'b0010010;

4'h6:seven=7'b0000010;

4'h7:seven=7'b1111000;

4'h8:seven=7'b0000000;

4'h9:seven=7'b0010000;

default:seven=7'b1111111;

endcase

endfunction

endmodule

硬件测试:

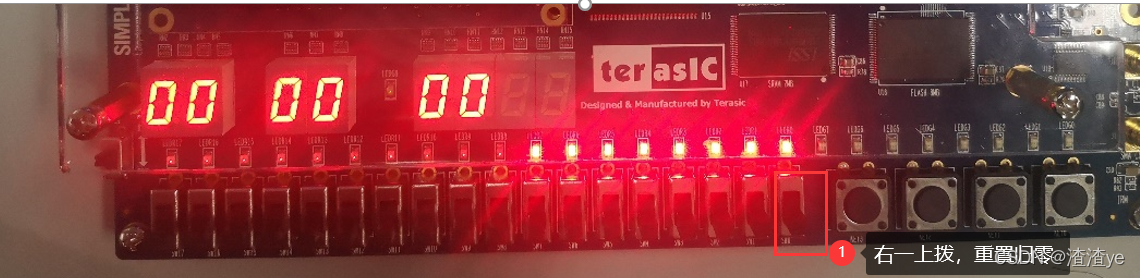

归零

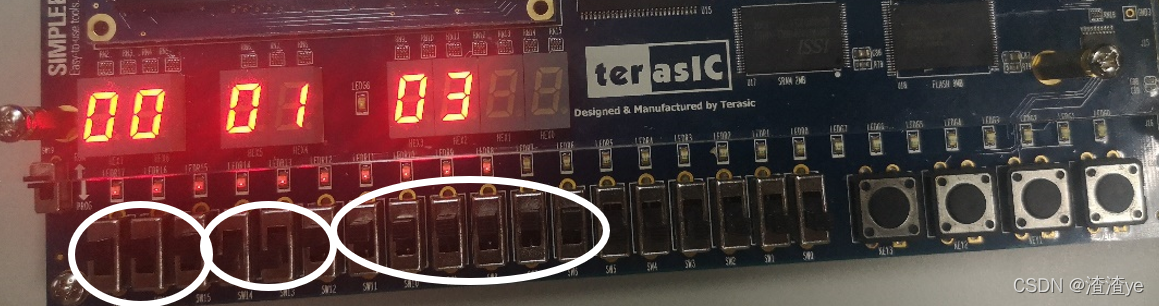

控制时间

设置闹钟,时间到,绿灯亮

版权声明

本文为[渣渣ye]所创,转载请带上原文链接,感谢

https://blog.csdn.net/yyfloveqcw/article/details/124362870

边栏推荐

- Kettle--控件解析

- PG SQL intercepts the string to the specified character position

- Use future and countdownlatch to realize multithreading to execute multiple asynchronous tasks, and return results after all tasks are completed

- About me

- leetcode--380.O(1) 时间插入、删除和获取随机元素

- Express②(路由)

- Dolphin scheduler scheduling spark task stepping record

- Tensorflow Download

- Double pointer instrument panel reading (I)

- Reading notes: Secure federated matrix factorization

猜你喜欢

![[machine learning] Note 4. KNN + cross validation](/img/a1/5afccedf509eda92a0fe5bf9b6cbe9.png)

[machine learning] Note 4. KNN + cross validation

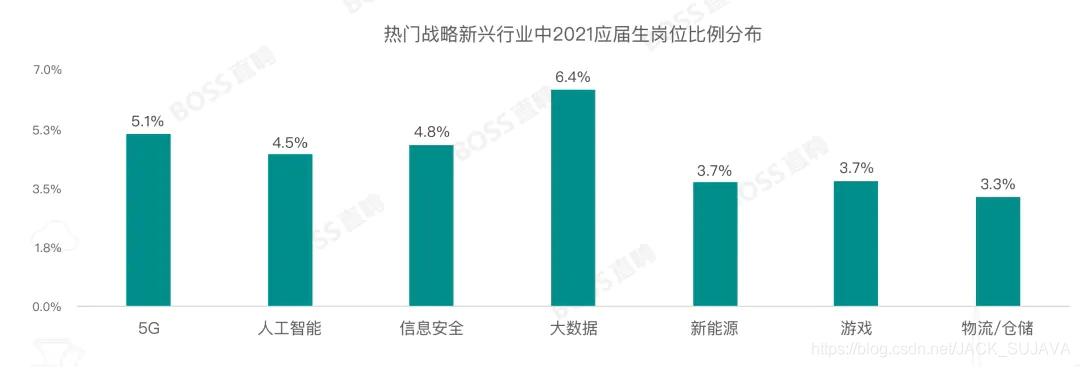

2021年秋招,薪资排行NO

The query did not generate a result set exception resolution when the dolphin scheduler schedules the SQL task to create a table

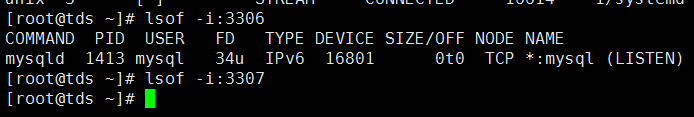

Port occupied 1

JMeter pressure test tool

freeCodeCamp----time_ Calculator exercise

Kettle--控件解析

Express middleware ③ (custom Middleware)

Static interface method calls are not supported at language level '5'

freeCodeCamp----arithmetic_ Arranger exercise

随机推荐

Three characteristics of volatile keyword [data visibility, prohibition of instruction rearrangement and no guarantee of operation atomicity]

Generate 32-bit UUID in Oracle

2022年江西最新建筑八大员(质量员)模拟考试题库及答案解析

About me

Utilisation de GDB

Analysis of cluster component gpnp failed to start successfully in RAC environment

MySQL [read / write lock + table lock + row lock + mvcc]

Oracle lock table query and unlocking method

Leetcode brush question 𞓜 13 Roman numeral to integer

Es introduction learning notes

Static interface method calls are not supported at language level '5'

Modification of table fields by Oracle

Oracle and MySQL batch query all table names and table name comments under users

Express ② (routing)

Oracle renames objects

Express②(路由)

Port occupied 1

美联储数字货币最新进展

The art of automation

Special window function rank, deny_ rank, row_ number