当前位置:网站首页>Points for attention in Modelsim simulation acceleration

Points for attention in Modelsim simulation acceleration

2022-04-22 07:21:00 【oFFCo】

Let's talk about my usage ( I usually linux Next use , Considering that most people use windows, So the following example is windows How to use it under ):

1. establish modelsim subdirectories

2. First run , You still need to get there first modelsim Of gui Let's do it vlib –work, I don't need it anymore

3. stay modelsim Subdirectory establishment run.bat file , The contents are as follows ( Everyone has their own environment , Make appropriate changes ) vlog -incr ../ modelsim/yourtest_tb.v -f test.cfg \ +incdir+../ modelsim /include vsim -c -do "log -ports -internal yourtestbench/*; log -r yourtestbench /u0/*; run -all "\ -l log/ yourtest _tb.log -wlf yourtest.wlf work.testbench vlog be used for verilog compile , If you use vhdl Is used vcom -incr Switch used to compile incrementally , Can greatly speed up compilation test.cfg For simulation cfg file , Inside is the file name to be compiled , And the directory of the library -c Run the switch... For the command line -do "log -ports -internal yourtestbench/*; log -r yourtestbench /u0/*; run -all " and -wlf yourtest.wlf work.testbench be used for dump Output all signal waveform files to be viewed ( The format of waveform file is wlf , Be similar to vcs Of vpd and vcd file ),yourtestbenc Is the name of the simulation entry module ,u0 For the top layer of the module you want to test instance Name ,yourtestbenc and u0 All need to be changed according to their own environment . After using this command, it will be very convenient for everyone to watch the waveform ,( Maybe when you were a beginner ( Including I just used modelsim when ), It's all about looking at a signal , First from signals Pull it out of the window , Then run a series again , Efficiency is very low ) And after using this method , from signals The signal pulled out of the window , You can see the waveform directly , No need to run again . After the above method is established , Can run run.bat 了 ( Direct double click ), This will pop up a dos The window of , All operations are under this window , Do not start again modelsim 了 .

① Use incremental compilation

vlog -incr

vcom -incr

② Is not enabled GUI Interface , Record the simulation waveform ( Look at the waveform after the simulation ), Print the observed signal to a file , Direct comparison

vsim -c -do run_sim.do -l vsim.log -wlf vsim.wlf

③ Enable nodebug Pattern ( The default is debug Pattern ), The speed will increase , But some debugging functions will be disabled , such as trace x The function can't be used

vsim -nodebug

④ If called IPCORE, Study official UG, Speed up the simulation (ex:SRIO Acceleration switch )

⑤ Modify the design , Without affecting the simulation results , Modify design documents , Speed up the simulation (ex: take counter from 1024 Change it to 128)

To speed up the modelsim Method of simulating speed

The higher the simulation accuracy , Simulation efficiency at the end of the month .

The simulation adopts `timescale 1ns/1ns Comparison and adoption 1ns/100ps The simulation efficiency is high

simulation was two billion ns.

②clock generation coding tips

(from<A BFM Simulation Strategy for Verilog>)

② Reduce hierarchy

The fewer hierarchies in the design , The faster the simulation , This is because the parameter is in module Passing through the port in will consume the time of the emulator

③ Fewer processes , The more efficient the simulation is

The fewer processes appear in the code , The faster the simulation . Because it also takes time for the emulator to switch between multiple processes .

④ Reduce the use of gate level primitives , Try to use behavior description

The higher the level of abstraction of modeling , The more efficient the simulation is . Describe the same function and try to use behavior description , Use less gate level primitives

⑤ Use as much as possible case sentence , instead of if ...else sentence

If you use case Statement and if..else Statement can implement the same circuit , Try to use case sentence , To improve the simulation efficiency .

⑥ Reduce begin...end Use of statement blocks

Without semantic ambiguity , Minimize the use of begin...end Sentence block , To improve the simulation efficiency

⑦ Reduce the output display of the simulator

Excessive use of simulator output display tasks , Such as $display,$fdisplay etc. , It will slow down the execution speed of the simulator .

Be careful : The above points are just suggestions to improve the efficiency of simulation , It's not that the design code must do this , Instead, it is recommended to ensure the function of the code , Readability , On the premise of maintainability and safety ,

Try to improve the simulation efficiency , Save simulation and debugging time . After all, code functions , Readability , Maintainability and security are the most important .

① Use incremental compilation , When the whole simulation system is composed of a large number of files , Every time you modify a module After some signals in , When you want to check the timing waveform , If all the files are compiled , Will waste a lot of time . At this time , Incremental compilation can effectively save simulation time

vlog -incr

vcom -incr

② Is not enabled GUI Interface , Is not enabled modelsim Of GUI The interface can complete all the work of simulation , And it will be faster ; Record the simulation waveform ( Look at the waveform after the simulation :do wave.do; Or print the observed signal to a file , Direct comparison )

vsim -c -do run_sim.do -l vsim.log -wlf vsim.wlf

xxx ③ Enable nodebug Pattern ( The default is debug Pattern ), The speed will increase , But some debugging functions will be disabled , such as trace x The function can't be used

vlog -nodebug

④ Avoid displaying unnecessary signals

Use log -r /* ( Record all the signals , After running this command, even if the signal is not added before simulation wave window , After the simulation is completed, directly add wave The waveform can be viewed in the window , It's more convenient , But the disadvantage is that when the project is large and the simulation time is long, the simulation speed is slow , It also takes up a large amount of memory .)

The advantage is : The waveform of all signals can be recorded , It is convenient to view all the waveforms you want to view later

The disadvantage is that : It will reduce the simulation speed

⑤ If called IPCORE, Study official UG, Speed up the simulation (ex:SRIO Acceleration switch )

⑥ Modify the design , Without affecting the simulation results , Modify design documents , Speed up the simulation (ex: take counter from 1024 Change it to 128)

⑧Use the vopt command to increase simulation speed.(modelsim.ini In file :“VoptFlow = 1” Optimization is on by default )

vsim -vopt

-vopt Run vopt optimization before elaborating the simulator

-voptargs="<arglist>" Pass the specified arguments to vopt

-novopt

(optional) Forces vlog to produce code if the VoptFlow variable is set to 1 (optimizations

turned on) in the modelsim.ini. (VoptFlow = 1 is the default behavior.) Use this argument

together with the vsim -novopt command to run the simulator without any optimizations.

For example, you may want to use this argument when you are coding an RTL block with a

small testcase.

-voptargs="+acc" :

The +acc switch is more

related to those, and is used to preserve visibility to certain categories of objects that might

otherwise be optimized away. Objects that get optimized away can make your debug and

analysis efforts more difficult

⑨ In order to improve the simulation performance , Sampling should be minimized .

Reduce the total number of simulation outputs , It can speed up the simulation process . Using the computer's output device slows down the program , therefore , The process of recording simulation output will slow down the simulation .

$monitor $write $display $strobe The application of such system functions helps debug, But it will slow down the simulation , Balance according to the actual situation .

An effective way to reduce data sampling is : When entering testcase Where you are interested in , Make the exciter turn on the sampling process . Monitoring can be started and closed through the following two system tasks :

$monitoron( Start the recently closed monitoring task ) ,$monitoroff( Close the active monitoring task )

+nospeicify: namely ncverilog Ignore the specified in the library file during simulation 50 time unit Time delay of .

+delay_mode_zero : Add the delay defined in the standard library cell 50 Replace with 0.

+notimingcheck : Timing check switch , such as setup/hold/width Check and so on , If used option, The timing is not checked during simulation , Behavior similar to RTL Simulation . stay PR not finished ,sdf When the anti bid document is not ready , This option can be used to ignore the delay , It can be used for a rough check of functionality . But in the real post run simulation , This option is not available , Otherwise, the effectiveness of simulation will be greatly reduced . You can use tfile To add a specific path to no timing check list file in .

always begin:clk_50M_blk

clk_50M = 1'b0;

forever #(20/2) clk_50M = ~clk_50M; //50Mhz

end

always begin:clk_100M_blk

clk_100M = 1'b0;

forever #(10/2) clk_100M = ~clk_100M; //100Mhz

end

ddr Simulation acceleration settings ,

1、 Skip calibration

2、

版权声明

本文为[oFFCo]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204220611029383.html

边栏推荐

- 【数论】同余(三):一元线性同余方程

- Quartus II prevents signals from being integrated

- MySQL learning notes

- vivado生成和调用edf网表文件

- 【数论】同余(五):多元线性同余方程

- 完成一个学生信息管理系统,系统练习面向对象、函数、字符串等知识。实现知识的综合应用。 使用类、函数、数据库等来实现

- JVM中唯一一个不会发生GC和OOM的存储区域

- [number theory] prime number (I): basic concepts, properties, conjectures and theorems

- 【数论】素数(二):素数筛法(埃式筛、欧拉筛、区间筛)

- 【数论】素数(一):基本概念、性质、猜想、定理

猜你喜欢

![Error: [HSI 55-1545], unable to generate fsbl normally, unable to read in MSS file, failed to close system mss](/img/4e/34e2820ff8579007b20b33b27d8f1d.png)

Error: [HSI 55-1545], unable to generate fsbl normally, unable to read in MSS file, failed to close system mss

最强操作符学习之路(C语言详解)

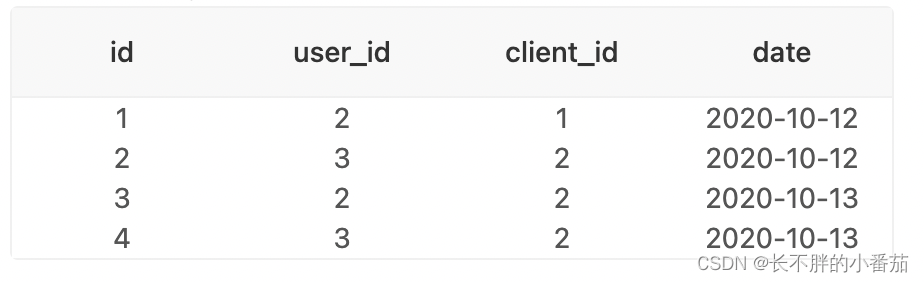

SQL复习语法笔记整理,新鲜出炉

写一个方法sanjiao(a, b, c),判断三个参数是否能构成一个三角形,如果不能则抛出异常IllegalArgumentException,显示异常信息a,b,c”不能构成三角形”,如果可以

1、编写学生信息管理系统以下三个模块:并检测执行。 1、添加学生信息 4、查询学生信息 5、查询全部学生信息

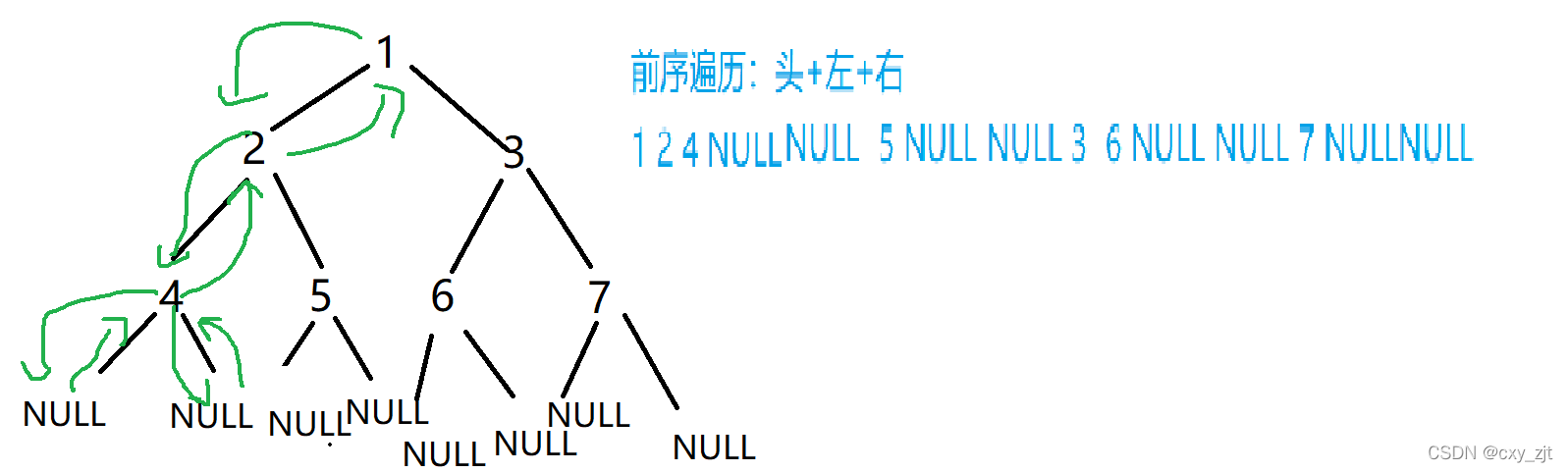

二叉树链式结构操作LeetCode+牛客(详解)

Pixhawk4+Up Board / NUC Implement VIO By Deploying T265

桥接模式下主机ping不通虚拟机

Jeecg project deployment notes

Review of the sixth edition of introduction to software engineering (notes)

随机推荐

Eight functions of random library

详解树状数组模板——理论和代码的实现

[DRC RTSTAT-1] Unrouted nets: 1 net(s) are unrouted

桥接模式下主机ping不通虚拟机

ERROR: [Hsi 55-1545] ,无法正常生成fsbl,Unable to read in MSS file,Failed to closesw system.mss

Find a notepad file by yourself, find the data material by yourself, and count the times of three keywords or sentence entries in the whole text.

win10 anaconda安装cocotb

最强数组学习之路

提示用户输入其名字 用户作出响应后 将其名字写 入到文件guest.txt 中 程序判断当不等于n的时候,就执行 创建文件data.txt,文件共10万行,每行存放一个1~100之间的随机一个整数

ASP. Net daily development notes ---- export to excel

If an error is reported, process the ES6 filter to filter the array

Pycharm only needs five steps to improve the download speed by using Tsinghua image source

vivado生成和调用edf网表文件

Define the class shape as the parent class, and define the method to calculate the perimeter and area in the class; (2) Define the shape subclass circle, with radius attribute and constant PI, and ove

写一个方法sanjiao(a, b, c),判断三个参数是否能构成一个三角形,如果不能则抛出异常IllegalArgumentException,显示异常信息a,b,c”不能构成三角形”,如果可以

【数论】【不定方程】n元一次不定方程、佩尔方程、毕达哥拉斯定理、费马大定理

【数论】素数(五):梅森素数(Lucas_Lehmer判定法)

[SVN] subversion installation notes

ASP. Net daily development notes ---- record logs with text documents

Shift left and right