当前位置:网站首页>HDLBits: 在线学习 SystemVerilog(零)-在线“巡礼” HDLBits

HDLBits: 在线学习 SystemVerilog(零)-在线“巡礼” HDLBits

2022-08-10 17:05:00 【碎碎思】

HDLBits: 在线学习 SystemVerilog(零)-在线“巡礼” HDLBits

关于HDLBits,已经不止一次推荐给大家了,我也不在唠叨了,今天之后将使用约二十几篇文章使用SV实现HDLBits。

开篇第零篇当然是带大家先熟悉一下HDLBits网站。

网站介绍

网址如下:

https://hdlbits.01xz.net/

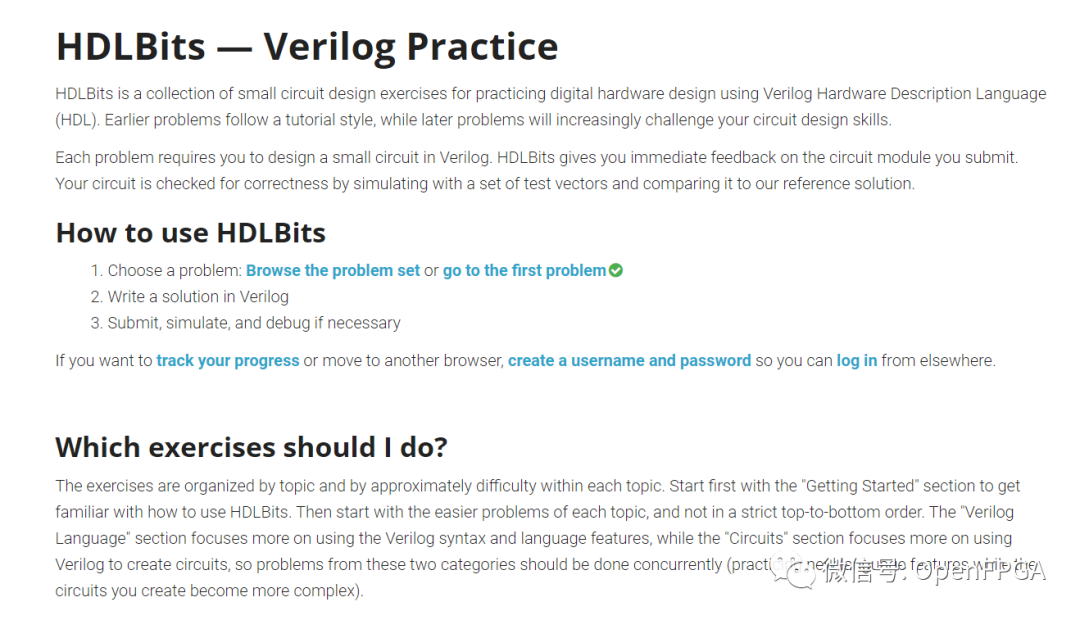

打开网页,首先就是网站的介绍:

简单翻译以下就是:

HDLBits 是一组小型电路设计习题集,使用 Verilog 硬件描述语言 (HDL) 练习数字硬件设计~

这里特意提醒了以下,如果想跟踪学习的进度或换到另一个浏览器使用,最好创建一个用户名和密码,以便可以从其他地方登录使用。

创建《用户名和密码》很简单,下面的界面:

点击箭头位置后,填写用户名和密码后,点击箭头位置就创建完成了。

完成后登录就可以在箭头位置看到你的用户名和密码了。

核心内容

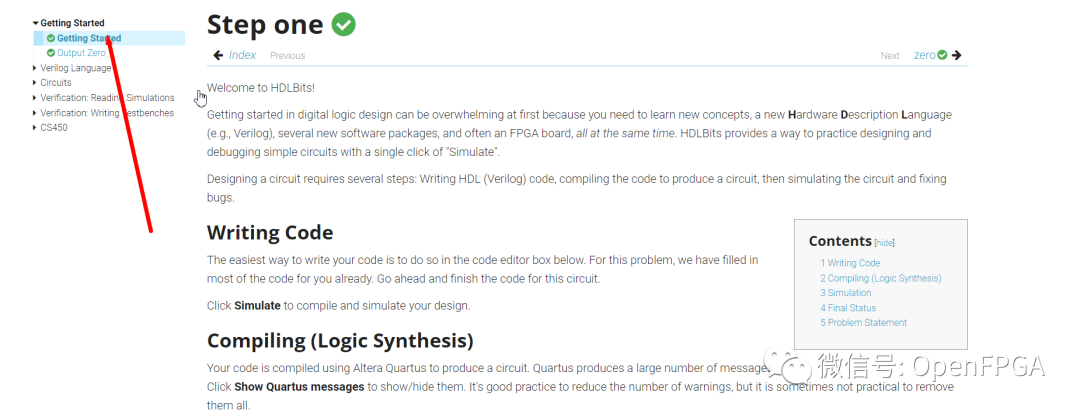

网站的核心当然是相关语法和题目了。首先就是几大主题:

相关内容就是和Verilog相关的组合逻辑和时序逻辑了。点击Geting Started,开始练习题目。

进去后就可以当成一本“语法书”使用了,涉及Verilog的相关语法整理,层级关系很Nice。

点击进去相关标题就可以联系题目了~

关于题目

整个网站大约180道题左右,没有标准答案,网上很多关于Verilog的参考答案,度娘就有了,我们这次是使用SystemVerilog,网上目前好像还没有答案,不过我尽量快点更新~

练习题

我们今天更新两道练手用的练习题,主要熟悉整个网站的使用环境。

Step one

点击图片上的位置就可以第一道题目练习了,前面关于很多网站题目的介绍,大家有兴趣可以看看。

进度条拉到最后就看到第一道题目了:

其中:

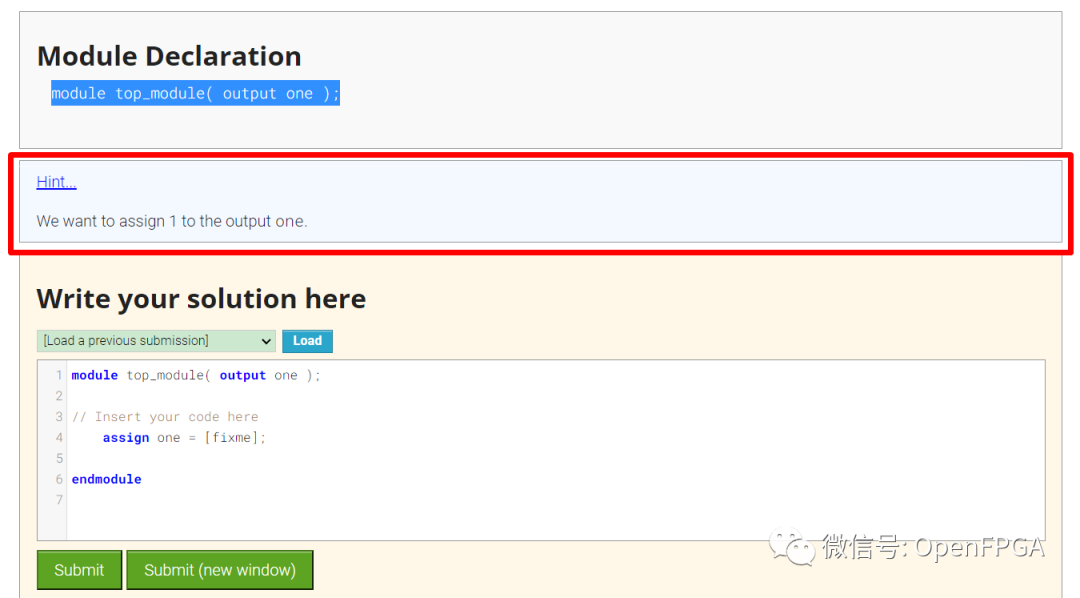

区域1:说明题目是实现什么功能;

区域2:顶层声明(输入、输出声明一定要使用定义好的);

区域3:编写代码

编写完代码后点击区域3中的Submit,就可以进行综合仿真了,我们接下来实际操作一下。

题目说明

设计一个没有输入和一个输出的电路,该输出端口时钟驱动逻辑 1(或逻辑高电平)。

模块端口声明如下:

module top_module( output one );PS:这里注意一下下图中位置,这是在你不理解题目的情况下可以查看作者给的小小提示~

题目解析

这个没什么说的,一句话就可以了“assign one = 1;”。难度不大,对于SV来说,我们要修改一下输出端口的变量类型为logic,这部分内容可以查看《数字硬件建模SystemVerilog(八)-端口声明》,然后将下面的代码输入到区域3中即可。

module top_module (

output var logic one

);

assign one = '1 ;

endmodule

点击Submit,等待一会就能看到下图结果:

第一题就完美结束,我们今天再做一道。

Zero

点击下图位置就可以进入到下一题了。

题目说明

设计一个没有输入和一个输出的电路,输出一个常数0(或逻辑低电平)

模块端口声明如下:

module top_module(

output zero

);题目解析

这个没什么说的,一句话就可以了“assign one = 0;”。难度不大,对于SV来说,我们要修改一下输出端口的变量类型为logic,这部分内容可以查看《数字硬件建模SystemVerilog(八)-端口声明》,然后将下面的代码输入到区域3中即可。

module top_module (

output var logic zero

);

assign zero = '0 ;

endmodule

点击Submit,等待一会就能看到下图结果:

第二题就结束了。

总结

今天简单介绍了一下HDLBits这个网站,简单又不失严谨,真的很适合入门学习Verilog/SV。题目由浅入深,大家可以试着自己学习解答,然后在找网上的代码对比学习(无标准答案)。

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

边栏推荐

猜你喜欢

随机推荐

自适应模糊神经网络与bp神经网络的区别

How to use bitwise operators in C language

如何使用Swift Package插件生成代码

DGIOT平台实时展示OPC上报数据全流程代码剖析

fastjson链分析(1.2.22-47)

聊聊云原生数据平台

如何搭建知识库,让您的内容更丰富?

JWT 实现登录认证 + Token 自动续期方案

v-model指令:获取和设置表单元素的值

未来5年的9大技术趋势

defi质押借贷理财挖矿dapp系统开发逻辑

Pytorch GPU模型推理时间探讨2——显卡warm up

奥迪的极致高端属于一个大写的H?重塑时空,谁会是这个夜晚的主角?

华为-求int型正整数在内存中存储时1的个数

李斌带不动的长安新能源高端梦,华为和“宁王”能救吗?

深度学习培训二笔记

从宠爱到嫌弃,蒸发1500亿后,这家明星企业为何陨落?

MySQL增加字段SQL语句

网易云信亮相LiveVideoStackCon2022,解构基于WebRTC的开源低延时播放器实践

node环境变量配置,npm环境变量配置