当前位置:网站首页>Arm common assembly instructions

Arm common assembly instructions

2022-04-23 06:48:00 【tilblackout】

1、 Commonly used instructions

(1)LDR、STR、MOV

LDR R0,[R1] #R0 = *R1, Read R1 Points to the contents of the memory area , Deposit in R0

STR R0,[R1] #*R1 = R0, take R0 write in R1 Point to memory area

MOV R0,R1 #R0 = R1

MOV R0,#0X10 #R0 = 0x10

LDR R0,=0X12345678 #R0 = 0x12345678 # If there is no equal sign, it will 0x12345678 The value pointing to memory is taken out and put into R0

Pseudo instruction , All instructions are 32 position , but MOV You can't do it all at once 32 The value of a , Because it has several bits to represent registers and instructions (2)add、sub

add r0,r1,#4 #r0=r1+4

sub r0,r1,#4 #r0=r1-4

sub r0,r1,r2 #r0=r1-r2(3)B、bl

B # An unconditional jump order

bl main # Jump to main, And save the address of the next instruction in lr In the register (4)ldmia、stmdb

// The stack is stored down from the high address

ldmia sp,{fp,sp,pc}

1.ldm Read memory for ,m by many

2. There is a high value in the memory number register , It has nothing to do with the order written later

3.ia by increase after, That is, read first and then add

stmdb sp!,{sp,ip,lr,pc}

1.db by decrease before, That is, reduce first and then deposit

2. Exclamation mark indicates SP Equal to the final modified SP value (5)MRS、MSR

MRS: Transfer the contents of the program status register to the general register .MRS <Rd>,CPSR/SPSR

MSR: Transfers the contents of the operands to a specific field in the program status register .MSR CPSR/SPSR,<Rd>

MRC and MCR similar .(6)teq、cmp

teq: Test register and register / Whether the immediate values are equal , If equal set CPSR The median condition is 1

teq r0, r1

ADDeq R0, R0, #1; # if R0 == R1, eq It's true , be R1=R1 + 1

cmp: Compare the size of two operands

CMP R0, R1;

ADDHI R0, R0, #1; # if R0>R1,HI It's true , be R0=R0+1

ADDLS R1, R1, #1; # if R0<=R1,LS It's true , be R1=R1+1(7)adr Instructions : Calculate the relative offset , The front and back addressing space is 4K

start:MOV r0,#10

ADR r4,start # Equivalent to SUB r4,pc,#0xc, Because of the current pc Value for this instruction +8 , therefore -0xc2、 Other

ADC Add instruction with carry

ADD Add instruction

AND Logic and instruction

B Jump instruction

BIC Bit clear instruction

BL Jump instruction with return

BX Jump instructions with state switching , The lowest is 1 when , perform Thumb Instructions , by 0 when , perform ARM Command execution

BLX Jump instructions with return and state switching

CDP Coprocessor data operation instructions

CMN Compare inverse instructions

CMP Comparison instruction

EOR XOR instruction

LDC Data transfer instructions from memory to coprocessor

LDM Load multiple register instructions

LDR Memory to register data transfer instructions

MCR from ARM Register to coprocessor register data transfer instructions

MLA Multiply and add instructions

MOV Data transfer instructions

MRC From coprocessor registers to ARM Register data transfer instructions

MRS delivery CPSR or SPSR Content to general register instruction

MSR Transfer general registers to CPSR or SPSR Instructions

MUL 32 Bit multiplication instructions

MLA 32 Bit multiply plus command

MVN Reverse data transfer instruction

ORR Logic or instruction

RSB Reverse subtraction instruction

RSC Reverse subtraction with borrow

SBC With borrow subtraction instructions

STC Coprocessor registers write memory instructions

STM Bulk memory word write instructions

STR Register to memory data transfer instruction

SUB Subtraction instructions

SWI Software interrupt command

SWP Exchange instructions

TEQ Equality test instructions

TST Bit test instructions

--------------------------------------------------

Condition code Mnemonic suffix sign meaning

0000 EQ Z Set up equal

0001 NE Z Zero clearing It's not equal

0010 CS C Set up The unsigned number is greater than or equal to

0011 CC C Zero clearing The unsigned number is less than

0100 MI N Set up negative

0101 PL N Zero clearing A positive number or zero

0110 VS V Set up overflow

0111 VC V Zero clearing No overflow

1000 HI C Set up Z Zero clearing The unsigned number is greater than

1001 LS C Zero clearing Z Set up The unsigned number is less than or equal to

1010 GE N be equal to V The signed number is greater than or equal to

1011 LT N It's not equal to V The signed number is less than

1100 GT Z Clear and [N be equal to V] There are signs greater than

1101 LE Z Set or [N It's not equal to V] The signed number is less than or equal to

1110 AL Ignore Unconditional execution 版权声明

本文为[tilblackout]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204230549282527.html

边栏推荐

- cartographer_node 编译没问题,但是运行直接挂掉的bug

- Informatics one book pass - small ball

- [learn] HF net training

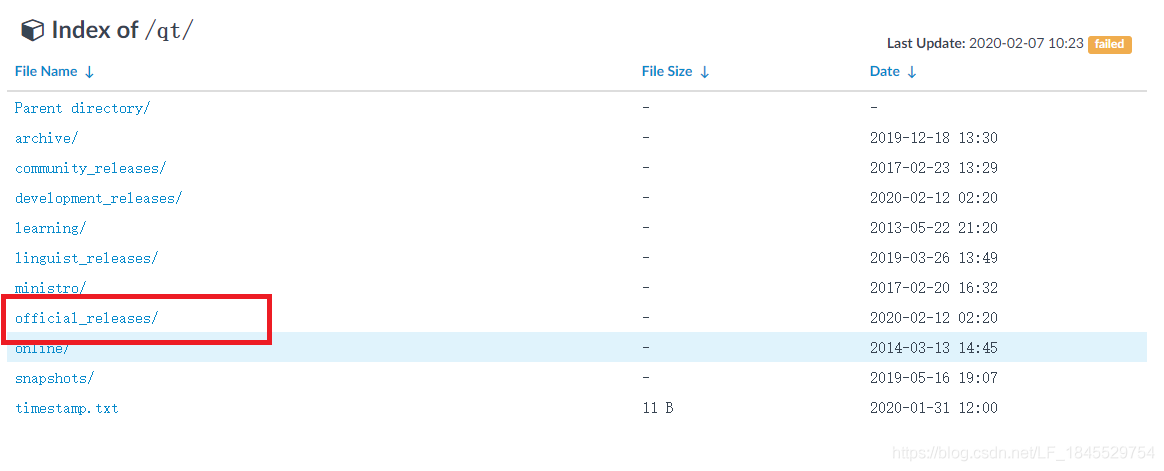

- Qt 添加QSerialPort类 实现串口操作

- The difference between single quotation mark, double quotation mark and back quotation mark in shell script

- 修改注册表的值

- TensorFlow张量介绍

- el-table添加序号

- FOC single resistance sampling position loop control servo motor

- Shell脚本 &&和||的使用

猜你喜欢

Eigen 学习总结

QT add qserialport class to realize serial port operation

![[UDS unified diagnostic service] II. Network layer protocol (2) - data transmission rules (single frame and multi frame)](/img/4f/315a9b4cd85ebaad39cfa985dea45b.png)

[UDS unified diagnostic service] II. Network layer protocol (2) - data transmission rules (single frame and multi frame)

微信小程序之 js 时间戳/1000 转换 秒,六个小时后,一天后,本周五 选项计算时间

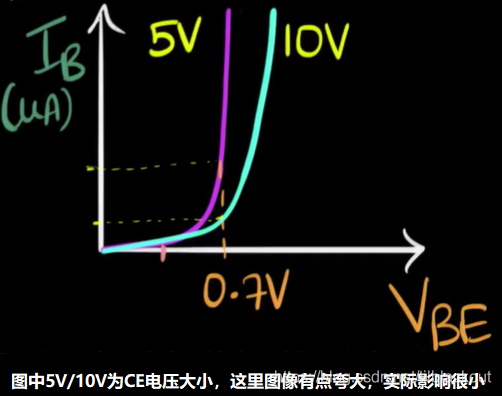

Principle and characteristic analysis of triode

![[UDS unified diagnosis service] i. diagnosis overview (1) - diagnosis overview](/img/c5/4b3092daeabf0f4889d93fef327c88.png)

[UDS unified diagnosis service] i. diagnosis overview (1) - diagnosis overview

Introduction to nonparametric camera distortion model

谈谈v-if显示隐藏问题

cv_bridge 与opencv 版本不匹配的解决

基于SSD的物体检测案例实现

随机推荐

FOC single resistance sampling position loop control servo motor

C语言进阶要点笔记2

Palindromic Primes

SQLite3 encrypted version

HDU-Memory Control

[UDS unified diagnosis service] i. diagnosis overview (1) - diagnosis overview

CUDA环境安装

[UDS unified diagnostic service] IV. typical diagnostic service (2) - data transmission function unit

C language code specification

Using printf in MFC

深蓝学院激光slam 理论与实践 第三章激光雷达去畸变 作业习题

查漏补缺(一)

QT icon application

查漏补缺(五)

Node的数据库编程

el-form表单多重循环校验

HDU-Tunnel Warfare

Shell脚本 单引号、双引号和反引号的区别

Qt 添加QSerialPort类 实现串口操作

软件工程中的十三种文档