当前位置:网站首页>VHDL arbitrary frequency divider (50% duty cycle)

VHDL arbitrary frequency divider (50% duty cycle)

2022-04-23 06:47:00 【Round moon】

Preface

Before last winter vacation, one of my relatives asked me how to make a five frequency divider . I don't think it's easy , Isn't it just a counter , But the discovery is not that simple , Because the even frequency divider can count according to the rising edge , But odd dividers can also , But I can't 50% Duty cycle . In today's class, the teacher solved this problem perfectly .

Even frequency division

We've studied counters before , Even allocation is nothing more than a counter , When using the signal as the intermediate variable, it should be noted that it is a lag variable , Therefore, when modifying, you should consider clearing . There's nothing to say about this. Go directly to the code .

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity Test is

generic(constant N:integer:=6);

port(signal clk:in std_logic;signal cout:out std_logic);

end Test;

architecture even of Test is

signal temp:integer:=0;

constant half:integer:=N/2;

begin

process(clk)

begin

if rising_edge(clk) then

temp<=temp+1;

if temp<half then

cout<='1';

elsif temp<N-1 then

cout<='0';

else

temp<=0;

cout<='0';

end if;

end if;

end process;

end even;

Here we can realize an even frequency division . This must be no problem for everyone , So let's continue to look at odd frequency division

Odd frequency division

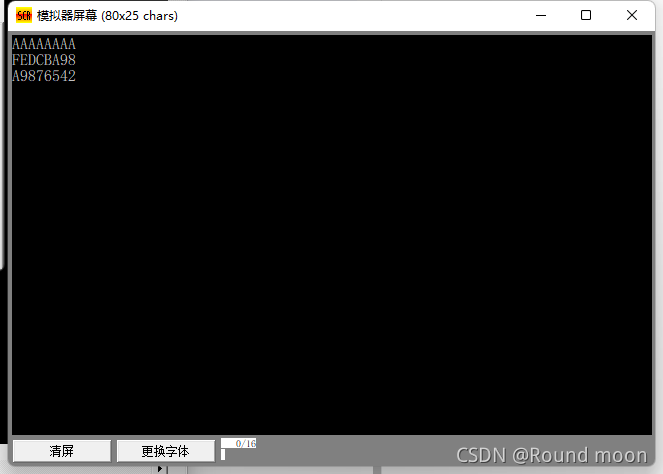

It's easy to think of odd frequency division 50% The duty cycle of must be related to both rising and falling edges , So we count both rising and falling edges , Take a look at the effect .

We find that only when the states in both directions are 0 Only when 0

Because looking in the right direction , He will have a delay of half a clock cycle , So you can do it 3.5 A cycle of high level . Then the rest is naturally low level .

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity div_any is

generic(constant N:integer:=5);

port(signal clk:in std_logic;signal cout:out std_logic);

end div_any;

architecture even of div_any is

signal tempA,tempB:integer:=0;

signal coutA,coutB:std_logic;

constant half:integer:=N/2;

begin

process(clk)

begin

if rising_edge(clk,coutA,coutB) then

tempA<=tempA+1;

if tempA<half then

coutA<='1';

elsif tempA<N-1 then

coutA<='0';

else

tempA<=0;

coutA<='0';

end if;

elsif falling_edge(clk) then

tempB<=tempB+1;

if tempB<half then

coutB<='1';

elsif tempB<N-1 then

coutB<='0';

else

tempB<=0;

coutB<='0';

end if;

end if;

cout<=coutA or coutB;

end process;

end even;

Arbitrary frequency division

So how to achieve arbitrary frequency division ?

We can find out , If the current number is even , Then it's just the same as the rising edge . But let's make a special judgment here ,1 The situation of .

The following code changes the frequency division status by entering the frequency division value .

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity div_any is

port(signal clk:in std_logic;

signal scaler:in integer range 0 to 63;

signal clk_out,clk_f,clk_r:out std_logic);

end div_any;

architecture DIV of div_any is

signal f_count:integer range 0 to 63:=0;

signal r_count:integer range 0 to 63:=0;

signal half:integer;

signal even:integer;

signal clk_f_temp,clk_r_temp:std_logic;

begin

half<=scaler/2;

even<= scaler rem 2;

with even*scaler select

clk_out<=clk_r_temp when 0,

clk when 1,

clk_f_temp or clk_r_temp when others;

process(clk,scaler)

begin

if rising_edge(clk) then

r_count<=r_count+1;

if r_count<half then

clk_r_temp<='1';

elsif r_count<scaler-1 then

clk_r_temp<='0';

else

clk_r_temp<='0';

r_count<=0;

end if;

elsif falling_edge(clk) then

f_count<=f_count+1;

if f_count<half then

clk_f_temp<='1';

elsif f_count<scaler-1 then

clk_f_temp<='0';

else

clk_f_temp<='0';

f_count<=0;

end if;

end if;

end process;

clk_f<=clk_f_temp;

clk_r<=clk_r_temp;

end DIV;

By-Round Moon

版权声明

本文为[Round moon]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204230549498912.html

边栏推荐

- SDOI2009-HH的项链

- Log writing method (with time)

- Eigen 学习总结

- copy constructor

- 20220222回归职场

- Wechat applet request encapsulation

- [UDS unified diagnostic service] II. Network layer protocol (2) - data transmission rules (single frame and multi frame)

- For() loop parameter call order

- 卷积神经网络实现CIFAR100数据集分类

- 金额输入框,用于充值提现

猜你喜欢

![[UDS unified diagnostic service] III. application layer protocol (1)](/img/e7/813e29a30e08eb92ccc836743be9aa.png)

[UDS unified diagnostic service] III. application layer protocol (1)

锚点定位——如何设置锚点居页面顶部距离,锚点定位并距离顶部一定偏移

For() loop parameter call order

汇编 32位无符号加法计算器

【UDS统一诊断服务】五、诊断应用示例:Flash Bootloader

![微信小程序之点击取消,返回上页,修改上页的参数值,let pages=getCurrentPages() let prevPage=pages[pages.length - 2] // 上一页的数据](/img/ed/4d61ce34f830209f5adbddf9165676.png)

微信小程序之点击取消,返回上页,修改上页的参数值,let pages=getCurrentPages() let prevPage=pages[pages.length - 2] // 上一页的数据

FOC电机库 定点PID代码分析

Call procedure of function

![[UDS unified diagnostic service] II. Network layer protocol (2) - data transmission rules (single frame and multi frame)](/img/4f/315a9b4cd85ebaad39cfa985dea45b.png)

[UDS unified diagnostic service] II. Network layer protocol (2) - data transmission rules (single frame and multi frame)

![C [document operation] PDF files and pictures are converted to each other](/img/6b/0742aa3eb45fbca091d6d20bc55326.png)

C [document operation] PDF files and pictures are converted to each other

随机推荐

sqlite编译

[UDS unified diagnostic service] II. Network layer protocol (1) - overview and functions of network layer

Log writing method (with time)

Sdoi2009-hh Necklace

[learn] HF net training

Modify registry values

基于VGG对五种类别图片的迁移学习

[UDS unified diagnosis service] i. diagnosis overview (3) - ISO 15765 architecture

欢迎使用Markdown编辑器

在visual stdio中运行qt程序

Opencv uses genericindex for KNN search

cartographer_node 编译没问题,但是运行直接挂掉的bug

带默认模板实参的类模板与模板模板形参的匹配

js获取链接?后边的参数名称或者值,根据url ?后的参数做判断

卷积神经网络实现CIFAR100数据集分类

Collection of practical tips for C language (continuously updated)

[UDS unified diagnosis service] i. diagnosis overview (1) - diagnosis overview

copy constructor

CUDA环境安装

死区时间的分析与设置