当前位置:网站首页>CPU-MIPS32指令架构(无内锁流水线微处理器)

CPU-MIPS32指令架构(无内锁流水线微处理器)

2022-08-09 12:35:00 【51CTO】

MIPS32中使用了大量的寄存器。因为寄存器的存取可以在一个时钟周期内完成,同时也简化了寻址方式。

MIPS32中除了加载和存储指令外,都是使用寄存器或立即数作为操作数的

MIPS32的寄存器分为两类:

1,、通用寄存器

寄存器名字 约定命名 用途

$0 zero 总是为0

$1 at 留作汇编器生成一些合成指令

$2-3 v0 v1 用于存放子程序的返回值

$4-7 a0-a3 调用子程序时,使用者4个寄存器传输前4个非浮点参数

$8-15 t0-t7 临时寄存器 子程序使用时可以不用储存和恢复

$16-23 s0-s7 子程序寄存器变量,改变这些寄存器值的子程序必须存储旧的值并在退出前恢复,对调用程序来说值不变

$24 $25 t8 t9 临时寄存器 子程序使用时可以不用储存和恢复

$26 27 $k0 $k1 由异常处理程序使用

$28 gp 全局指针

$29 sp 堆栈指针

$30 s8/fp 子程序可以用来作为堆栈帧指针

$31 ra 存放子程序返回地址

2、特殊寄存器

MIPS32架构中定义了三个特殊寄存器

1.PC 程序计数器

2.HI 乘除结果高位寄存器

3.LO 乘除结果低位寄存器

字节次序

大端模式 m[n] m[n+1] m[n+2] m[n+3]

小端模式 m[n+3] m[n+2] m[n+1] m[n]

指令格式

R类型(操作由op和func决定 rs RT 是源寄存器编号 rd 是目的寄存器的编号 sa只有在移位指令中使用)

| op | rs | rt | rd | sa | func |

6位 5 5 5 5 6

I类型(操作由op决定 16位的是操作的立即数)

| op | rs | rt | immediate

6位 5 5 16

J类型(操作由op决定 一般是跳转指令)

| op | address

6 26

寻址方式:

MIPS32架构的寻址方式有寄存器寻址、立即数寻址、寄存器相对寻址、PC相对寻址

1)寄存器相对寻址

这种寻址方式主要用于加载/存储指令使用,将一个16位的立即数作为符号拓展,然后与制定通用寄存器的值相加,从而得到一个有效地址

2)PC相对地址

这种寻址方式主要用于转移指令使用,在转移指令中有一个16位的立即数,将其左移两位并作为符号拓展,然后与程序计数寄存器进行相加 从而获得有效地址

协处理器CPO

MIPS32架构提供了最多4个协处理器CP0-CP3

CP0 用作系统控制

CP1 CP3 用作浮点处理单元

CP2 被保留用于特定实现

MIPS32指令集架构简介

本书设计的处理器遵循MIPS32 Release 1架构,所以本节介绍的MIPS32指令集架构指的就是MIPS32 Release 1。

1.4.1 数据类型

指令的主要任务就是对操作数进行运算,操作数有不同的类型和长度,MIPS32提供的基本数据类型如下。

位(b):长度是1bit。

字节(Byte):长度是8bit。

半字(Half Word):长度是16bit。

字(Word):长度是32bit。

双字(Double Word):长度是64bit。

此外,还有32位单精度浮点数、64位双精度浮点数等。

1.4.2 寄存器

在前文介绍RISC的特点时提到一点:大量使用寄存器。这是因为寄存器的存取可以在一个时钟周期内完成,同时也简化了寻址方式。MIPS32的指令中除加载/存储指令外,都是使用寄存器或立即数作为操作数的。MIPS32中的寄存器分为两类:通用寄存器(GPR:General Purpose Register)、特殊寄存器。

1、通用寄存器

MIPS32架构定义了32个通用寄存器,使用$0、$1……$31表示,都是32位。其中$0一般用做常量0。

在硬件上没有强制指定寄存器的使用规则,但是在实际使用中,这些寄存器的用法都遵循一系列约定,例如:寄存器$31一般存放子程序的返回地址。MIPS32中通用寄存器的约定用法如表1-1所示。在本书大部分章节中,测试程序都是直接使用汇编指令编写的,对寄存器的约定用法还不需要十分在意,但是本书的最后一章移植μC/OS-II时,因为涉及到C语言、汇编混合编程,对寄存器的约定用法就需要十分在意了。读者届时可以体会到表1-1中各个寄存器约定用法的作用。

2、特殊寄存器

MIPS32架构中定义的特殊寄存器有三个:PC(Program Counter程序计数器)、HI(乘除结果高位寄存器)、LO(乘除结果低位寄存器)。进行乘法运算时,HI和LO保存乘法运算的结果,其中HI存储高32位,LO存储低32位;进行除法运算时,HI和LO保存除法运算的结果,其中HI存储余数,LO存储商。

1.4.3 字节次序

数据在存储器中是按照字节存放的,处理器也是按照字节访问存储器中的指令或数据,但是如果需要读出一个字,也就是4个字节,比如读出的是mem[n]、mem[n+1]、mem[n+2]、mem[n+3]这四个字节,那么最终交给处理器的有两种结果。

{mem[n],mem[n+1],mem[n+2],mem[n+3]}

{mem[n+3],mem[n+2],mem[n+1],mem[n]}

前者称为大端模式(Big-Endian),也称为MSB(Most Significant Byte),后者称为小端模式(Little-Endian),也称为LSB(Least Significant Byte)。在大端模式下,数据的高位保存在存储器的低地址中,而数据的低位保存在存储器的高地址中。图1-4给出0x12345678在两种模式下的存储情况。本书实现的处理器采用的是大端模式(Big-Endian)。

1.4.4 指令格式

MIPS32架构中的所有指令都是32位,也就是32个0、1编码连在一起表示一条指令,有三种指令格式。如图1-5所示。其中op是指令码、func是功能码。

(1)R类型:具体操作由op、func结合指定,rs和rt是源寄存器的编号,rd是目的寄存器的编号,比如:假设目的寄存器是$3,那么对应的rd就是00011(此处是二进制)。MIPS32架构中有32个通用寄存器,使用5位编码就可以全部表示,所以rs、rt、rd的宽度都是5位。sa只有在移位指令中使用,用来指定移位位数。

(2)I类型:具体操作由op指定,指令的低16位是立即数,运算时要将其扩展至32位,然后作为其中一个源操作数参与运算。

(3)J类型:具体操作由op指定,一般是跳转指令,低26位是字地址,用于产生跳转的目标地址。

1.4.5 指令集

在“计算机的简单使用模型”中已经介绍过,可以直接使用0、1编码进行程序设计,但是那样显然太不方便、容易出错,于是人们使用一些助记符来表示各种指令,这就是汇编指令,使用汇编程序将汇编指令翻译为计算机可以识别的0、1编码。也就是将汇编指令翻译为图1-5所示的格式,这样处理器就可以识别了。MIPS32架构中定义的指令可以分为以下几类。注意:其中不包括浮点指令,因为本书实现的处理器不包含浮点处理单元,也就没有实现浮点指令,所以此处不介绍浮点指令。

1、逻辑操作指令

有8条指令:and、andi、or、ori、xor、xori、nor、lui,实现逻辑与、或、异或、或非等运算。本书设计的处理器实现了所有逻辑操作指令,将在第4、5章详细介绍各个逻辑操作指令的格式、作用、用法,及其实现过程。

2、移位操作指令

有6条指令:sll、sllv、sra、srav、srl、srlv。实现逻辑左移、右移、算术右移等运算。本书设计的处理器实现了所有移位操作指令,将在第5章详细介绍各个移位操作指令的格式、作用、用法,及其实现过程。

3、移动操作指令

有6条指令:movn、movz、mfhi、mthi、mflo、mtlo,用于通用寄存器之间的数据移动,以及通用寄存器与HI、LO寄存器之间的数据移动。本书设计的处理器实现了所有移动操作指令,将在第6章详细介绍各个移动操作指令的格式、作用、用法,及其实现过程。

4、算术操作指令

有21条指令:add、addi、addiu、addu、sub、subu、clo、clz、slt、slti、sltiu、sltu、mul、mult、multu、madd、maddu、msub、msubu、div、divu,实现了加法、减法、比较、乘法、乘累加、除法等运算。本书设计的处理器实现了所有算术操作指令,将在第7章详细介绍各个算术操作指令的格式、作用、用法,及其实现过程。

5、转移指令

有14条指令:jr 、jalr 、j 、jal、b、bal、beq、bgez、bgezal、bgtz、blez、bltz、bltzal、bne,其中既有无条件转移,也有条件转移,用于程序转移到另一个地方执行。本书设计的处理器实现了所有转移指令,将在第8章详细介绍各个转移指令的格式、作用、用法,及其实现过程。

6、加载存储指令

有14条指令:lb、lbu、lh、lhu、ll、lw、lwl、lwr、sb、sc、sh、sw、swl、swr,以“l”开始的都是加载指令,以“s”开始的都是存储指令,这些指令用于从存储器中读取数据,或者向存储器中保存数据。本书设计的处理器实现了所有加载存储指令,将在第9章详细介绍各个加载存储指令的格式、作用、用法,及其实现过程。

7、协处理器访问指令

有2条指令:mtc0、mfc0,用于读取协处理器CP0中某个寄存器的值,或者将数据保存到协处理器CP0中的某个寄存器。本书设计的处理器实现了所有协处理器访问指令,将在第10章详细介绍协处理器、协处理器访问指令的格式、作用、用法,及其实现过程。

8、异常相关指令

有14条指令,其中有12条自陷指令,包括:teq、tge、tgeu、tlt、tltu、tne、teqi、tgei、tgeiu、tlti、tltiu、tnei,此外还有系统调用指令syscall、异常返回指令eret。本书设计的处理器实现了所有异常相关指令,将在第11章详细介绍异常相关指令的格式、作用、用法,及其实现过程。

9、其余指令

有4条指令:nop、ssnop、sync、pref,其中 nop是空指令,ssnop是一种特殊类型的空指令,sync指令用于保证加载、存储操作的顺序,pref指令用于缓存预取。本书设计的处理器对这4条指令进行了简化并加以实现,将在第5章详细介绍简化后的实现过程。

1.4.6 寻址方式

MIPS32架构的寻址模式有寄存器寻址、立即数寻址、寄存器相对寻址和PC相对寻址四种。其中寄存器相对寻址、PC相对寻址介绍如下。

(1)寄存器相对寻址

这种寻址模式主要是加载/存储指令使用,其将一个16位的立即数做符号扩展,然后与指定通用寄存器的值相加,从而得到有效地址,如图1-6所示。

(2)PC相对寻址

这种寻址模式主要是转移指令使用,在转移指令中有一个16位的立即数,将其左移两位并作符号扩展,然后与程序计数寄存器PC的值相加,从而得到有效地址。如图1-7所示。

1.4.7 协处理器CP0

协处理器一词通常用来表示处理器的一个可选部件,负责处理指令集的某个扩展,拥有与处理器相独立的寄存器。MIPS32架构提供了最多4个协处理器,分别是CP0-CP3。协处理器CP0用作系统控制,CP1、CP3用作浮点处理单元,而CP2被保留用于特定实现。除CP0外的协处理器都是可选的。

协处理器CP0的具体作用有:配置CPU工作状态、高速缓存控制、异常控制、存储管理单元控制等。CP0通过配置内部的一系列寄存器来完成上述工作。本书设计的处理器实现了CP0的部分功能,将在第10章详述。

1.4.8 异常

在处理器运行过程中,会从存储器中依次取出指令,然后执行,但是有一些事件会打断正常的程序执行流程,这些事件有中断(Interrupt)、陷阱(Trap)、系统调用(System Call)等等,统称为异常。异常发生后,处理器会转移到一个事先定义好的地址,在那个地址有异常处理例程,在其中进行异常处理,这个地址称为异常处理例程入口地址。异常处理完成后,使用异常返回指令eret,返回到异常发生前的状态继续执行。本书设计的处理器实现了对硬件复位、中断(包含软中断、硬中断)、syscall系统调用、无效指令、溢出、自陷等6种异常的处理,将在第11章详述。

---------------------

作者:leishangwen

边栏推荐

- Flutter入门进阶之旅(八)Button Widget

- 你没见过的《老友记》镜头,AI给补出来了|ECCV 2022

- Flutter入门进阶之旅(四)文本输入Widget TextField

- Flutter Getting Started and Advanced Tour (4) Text Input Widget TextField

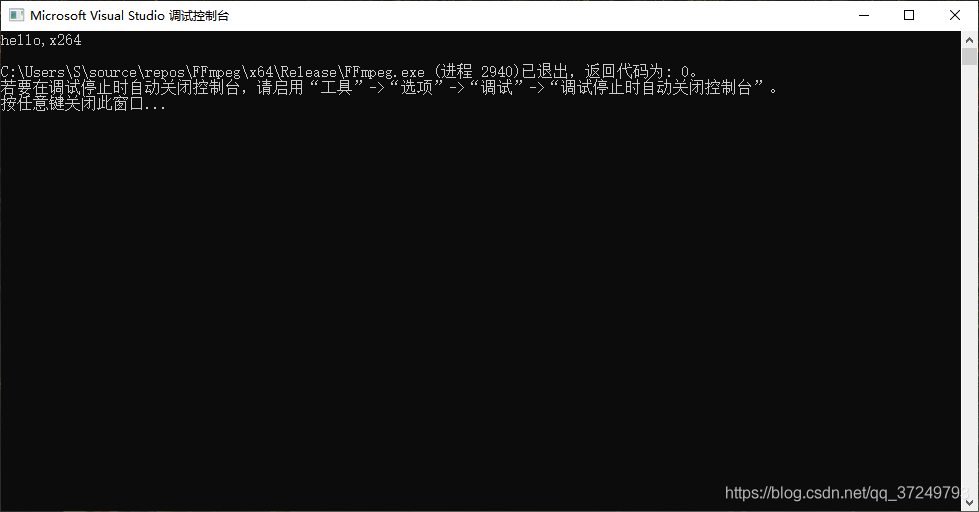

- FFmpeg在win10上编译安装(配置libx264)

- 900页数学论文证明旋转的黑洞不会爆炸,丘成桐:30多年来广义相对论首次重大突破...

- Scala 高阶(七):集合内容汇总(上篇)

- 我的2020年终总结

- 西湖大学教授怎么看AI制药革命?|量子位智库圆桌实录

- Customize VIEW to realize in-app message reminder to rotate up and down

猜你喜欢

告别手摇织布机的AI时代

Flutter入门进阶之旅(八)Button Widget

Customize VIEW to realize in-app message reminder to rotate up and down

在北极都可以穿短袖了,温度飙升至32.5℃

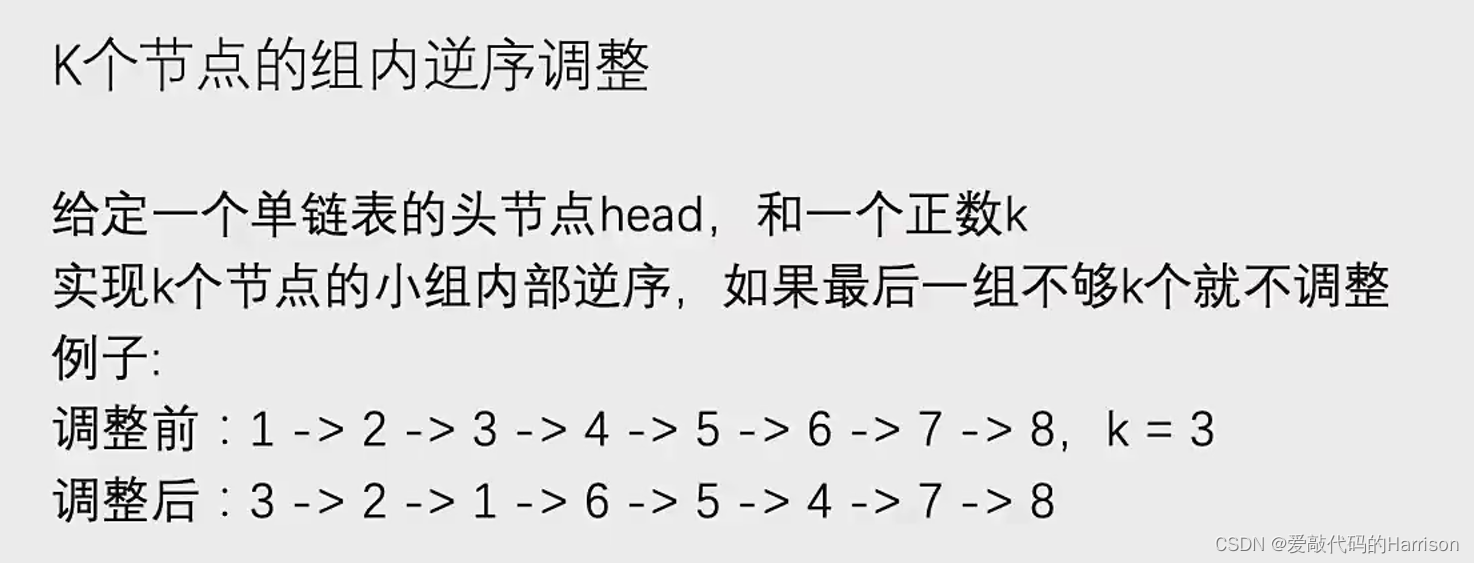

Intra-group reverse order adjustment of K nodes

链表噩梦之一?5000多字带你弄清它的来龙去脉

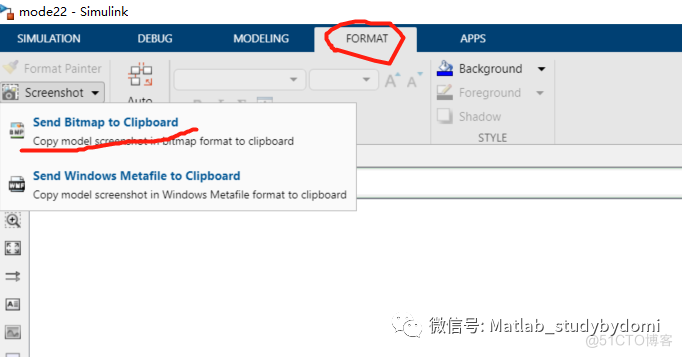

How to save Simulink simulation model as image or PDF

win10编译x264库(也有生成好的lib文件)

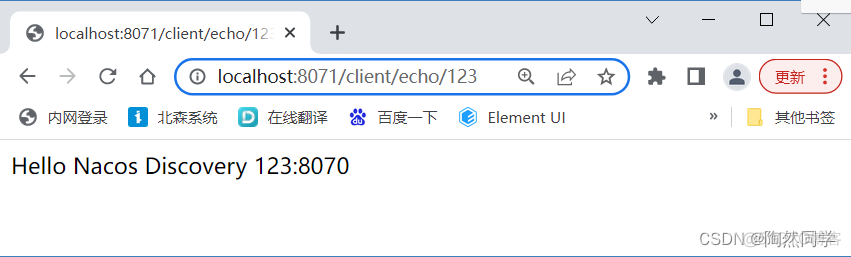

【微服务~远程调用】整合RestTemplate、WebClient、Feign

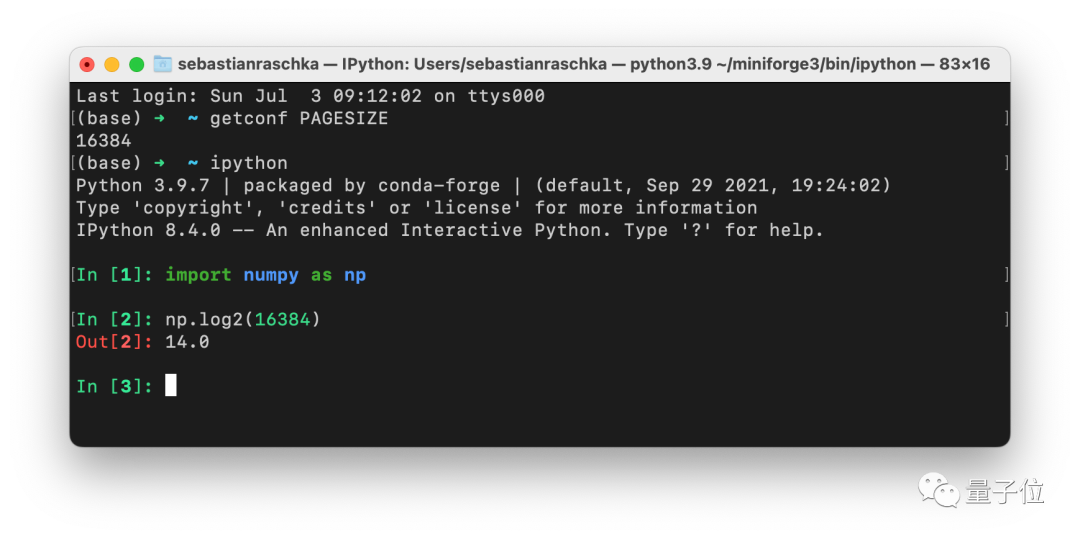

The batch size does not have to be a power of 2!The latest conclusions of senior ML scholars

随机推荐

00后写个暑假作业,被监控成这笔样

#Internet of Things essay#Xiaoxiong pie equipment development actual combat

系统提供的堆 VS 手动改写堆

非科班AI小哥火了:他没有ML学位,却拿到DeepMind的offer

ABP中的数据过滤器 (转载非原创)

Report: The number of students who want to learn AI has increased by 200%, and there are not enough teachers

[Microservice ~ Remote Call] Integrate RestTemplate, WebClient, Feign

h264协议

世界第4疯狂的科学家,在103岁生日那天去世了

win10编译x264库(也有生成好的lib文件)

链表噩梦之一?5000多字带你弄清它的来龙去脉

JVM之配置介绍(一)

Redis源码剖析之robj(redisObject)

Go Affair, How to Become a Gopher and Find a Go Job in 7 Days, Part 1

Adalvo收购其首个品牌产品Onsolis

Scala 高阶(七):集合内容汇总(上篇)

Redis源码剖析之跳表(skiplist)

Scala Advanced (7): Collection Content Summary (Part 1)

中科院打脸谷歌:普通电脑追上量子优越性,几小时搞定原本要一万年的计算...

ERP不规范,同事两行泪 (转载非原创)