当前位置:网站首页>SystemVerilog: Verifying knowledge bits and pieces

SystemVerilog: Verifying knowledge bits and pieces

2022-08-11 00:50:00 【Slow Cultivation】

目录

1. The software and hardware is world

3. import pkg::*是将pkgAll are imported?

1. The software and hardware is world

ClassOn behalf of the software world,ModuleOn behalf of the hardware of the world,InterfaceIs the bridge connecting the software and hardware of the world,But some more partial hardware.

PackageIs software world,相当于是SV中用于定义namescope的东西.Interface和Module(Because contain hardware world)不能包含在(Software belongs to the world)Package中.

类中的成员(数据、函数、任务)By default areautomatic类型.如果需要staticType members,需要用static显式地指定.Module中的所有变量、函数、Tasks are the default asstatic.如果需要automaticType members,需要用automatic显式地指定.

ModuleAre instantiated static.ClassObject creation is a dynamic.Here refers to the so-called static compiled already generated.And dynamic is refers to the simulation of actual after the start of executionnew()创建.

ModuleOnce instantiated,All the module instance has always been.而SVFor object lifetime management is used in automatic recovery mechanism,If an object has no ahandle指向它,它就被自动回收了.

由于Module和InterfaceThe hardware of the world,They are instantiated static,So in the compiled them has already been created.But it is dynamic object creation,Must be at the beginning of the simulation and real will be created after.以QuestaSimThe simulation for example,Even in the performvsim命令后,Object actually has not been created,直到执行了“run 0ns”以后(Those should be created in the beginning)Object really is created.

2. 什么是package

Ref: SystemVerilog Package (chipverify.com)

SystemVerilog中的packageProvides a save and share data、Parameters and the method of mechanism,可以在多个module、class、program和interface中重用.

packageThe content of the statement in the belong to thispackage作用域(scope).

如果要想使用package中的东西,就需要先import这个package,然后通过package引用.SV中的import与python中的import是相同的功能.

package my_pkg;

typedefenumbit [1:0] { RED,YELLOW, GREEN, RSVD } e_signal;

typedefstruct { bit [3:0]signal_id;

bit active;

bit [1:0] timeout;

} e_sig_param;

function my_func();

$display ("mypkg::my_func is called...");

endfunction

endpackageimportWhen can one by oneimportWant to use something,Or the ones will bepackageAll the thingsimport进来,如以下例子所示:

//import my_pkg::* ; // Import all things defined in my_pkg

import my_pkg::my_func ;// Import my_func only from my_pkg

module tb_top;

initial begin

my_func();

end如果在packageThe definition of a variable or function names and other external definition of a variable or function name conflict,需要用pkg_name::varIn the form of a reference to distinguish.

import my_pkg::* ; // Import all things defined in my_pkg

typedef enum bit [1:0] { RED,YELLOW,GREEN} e_pixel;

module tb_top;

initial begin

e_signal signal = RED;

e_pixel pixel = RED;

my_func();

end

endmodule以上例子中,用到了两个RED,会发生冲突.This is to addpackageA prefix is used to distinguish between,如下所示

...

e_signal signal = my_pkg::RED;

...3. import pkg::*是将pkgAll are imported?

A common misconception is the use of“import pkg::*”会将一个packageAll the things together, imported.So someone will worry about it will not make to compile the library become unduly large and simulation memory nervous?

其实不会.

“import pkg::*”The effect of this statement is to tell the emulator,当在当前namescopeIs not found in a class、变量或者函数、Tasks such as stating can go to thepkg中去找.And simulators are looking for a类、变量、函数、任务等Is to follow the so-called“就近原则”.

当有多个packgeContains a to search{ 类、变量、函数、任务}名,And they all with“import pkg::*”The form of import,此时会发生name collision,The most sensible thing to do is as above mentioned in section as topkg::nameThe explicit form for reference.

4. import vs include

如上所述,import是用于package的导入.

`includeInsert the file all the text in the same file contains.这是一个预处理语句,`include在import之前执行.

importDon't copy the text content.但是import可packageContent in the introduction ofimportStatements in the scope of the.

To put it simply, include is equivalent to copy/paste or insertion of whatever is present in that file to wherever you include; import is used to make all/select variables from a package visible.

边栏推荐

- rhel7.0解决yum无法使用(system is not registered to Red Hat Subscription Management)

- 【js】获取当前时间的前后n天或前后n个月(时分秒年月日都可)

- vim simple save window id

- Web APIs BOM- 操作浏览器之综合案例

- 小程序onPageNotFound的坑

- 【pypdf2】安装、读取和保存、访问页面、获取文本、读写元数据、加密解密

- 【openpyxl】只读模式、只写模式

- Distributed. Performance optimization

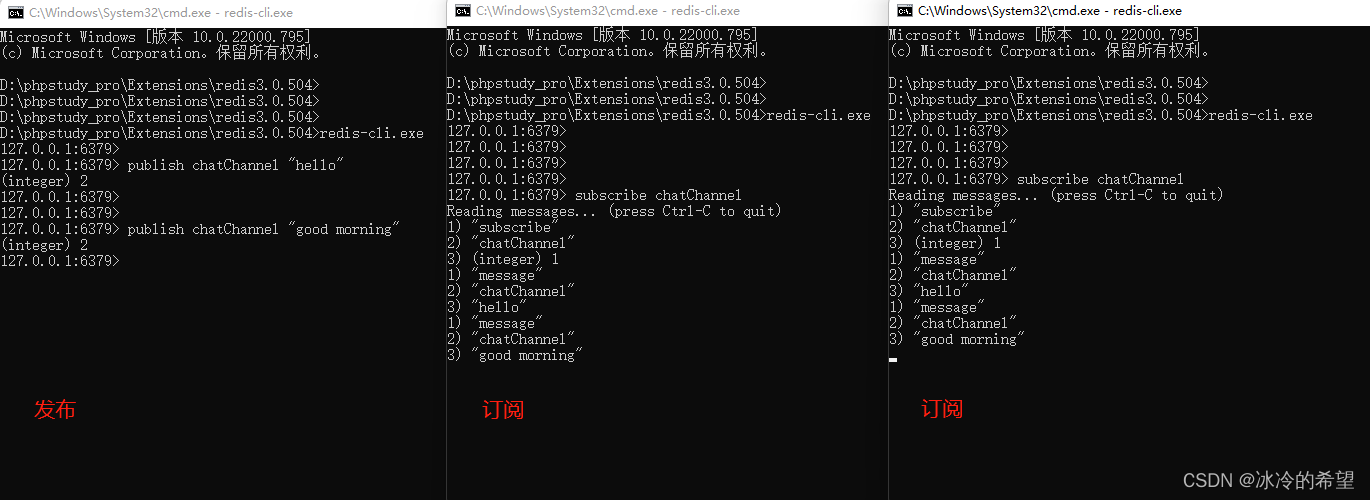

- Linux安装redis数据库

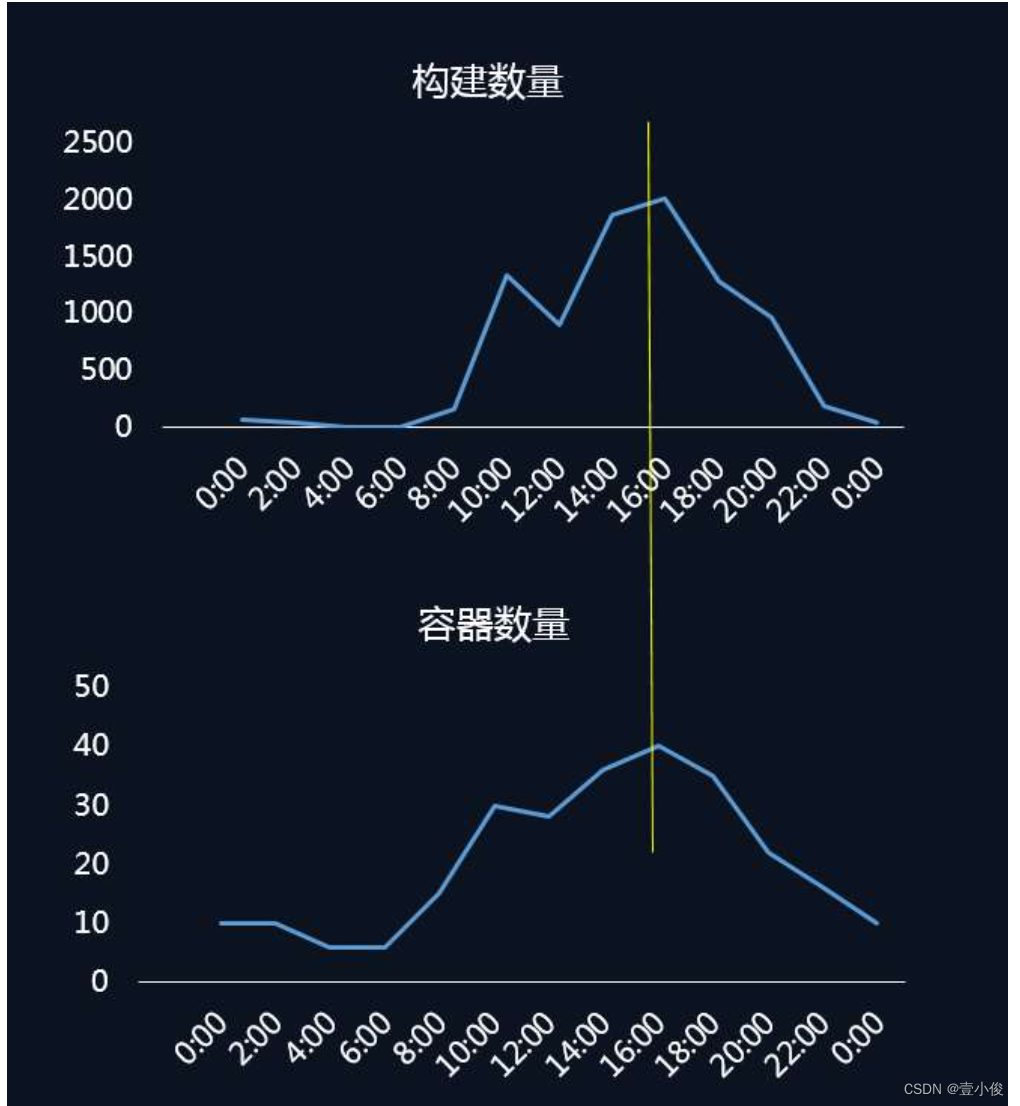

- 容器技术真的是环境管理的救星吗?

猜你喜欢

随机推荐

PMP每日一练 | 考试不迷路-8.10(包含敏捷+多选)

electron -autoUpdater 更新

① 数据库介绍 及 关系型数据库的关系代数表达式

Shell 文本三剑客 Sed

Go项目配置管理神器之viper使用详解

Single-chip human-computer interaction--matrix key

SQL语句--获取数据库表信息,表名、列名、描述注释等

input输入框超出部分用省略号表示以及判断内容是否有超出(PC端)

异常:try catch finally throws throw

SystemVerilog: 验证知识点点滴滴

rhel7.0解决yum无法使用(system is not registered to Red Hat Subscription Management)

【pypdf2】安装、读取和保存、访问页面、获取文本、读写元数据、加密解密

ADC和DAC记录

异常和异常处理机制

力扣------值相等的最小索引

两个数组的交集

【C语言】探索数据的存储(整形篇)

【经典排序】快速排序

Shell编程三剑客之sed

【mysql】mysql分别按年/月/日/周分组统计数据