当前位置:网站首页>CPU-MIPS32 instruction architecture (unlocked pipeline microprocessor)

CPU-MIPS32 instruction architecture (unlocked pipeline microprocessor)

2022-08-09 13:44:00 【51CTO】

MIPS32The use of a large number of register.Because access to register can be completed in one clock cycle,At the same time also simplifies the addressing mode.

MIPS32In addition to load and store instructions,All number immediately register or use as operands

MIPS32There are two types of register:

1,、通用寄存器

寄存器名字 约定命名 用途

$0 zero 总是为0

$1 at Reserved for the compiler to generate some synthetic instruction

$2-3 v0 v1 Used to store the return value of a subroutine

$4-7 a0-a3 调用子程序时,使用者4A register transfer before4个非浮点参数

$8-15 t0-t7 临时寄存器 Subroutine can need not when using storage and recovery

$16-23 s0-s7 A subroutine register variables,Change the register values subroutine must store the old values and before exiting recovery,Values for the caller

$24 $25 t8 t9 临时寄存器 Subroutine can need not when using storage and recovery

$26 27 $k0 $k1 The exception handler to use

$28 gp 全局指针

$29 sp 堆栈指针

$30 s8/fp A subroutine can be used as a stack frame pointer

$31 ra 存放子程序返回地址

2、特殊寄存器

MIPS32Architecture defines three special register

1.PC 程序计数器

2.HI , the high register

3.LO , the results of the low register

Byte order

大端模式 m[n] m[n+1] m[n+2] m[n+3]

小端模式 m[n+3] m[n+2] m[n+1] m[n]

指令格式

R类型(操作由op和func决定 rs RT Is the source register number rd Is the destination register number saOnly use in shift instruction)

| op | rs | rt | rd | sa | func |

6位 5 5 5 5 6

I类型(操作由op决定 16A number of is operation immediately)

| op | rs | rt | immediate

6位 5 5 16

J类型(操作由op决定 Usually jump instruction)

| op | address

6 26

寻址方式:

MIPS32Architecture of the addressing mode has register addressing、立即数寻址、寄存器相对寻址、PC相对寻址

1)寄存器相对寻址

This way of addressing is mainly used for loading/Storage instructions to use,将一个16A number of immediate as symbols to expand,Then the value for general-purpose registers with together,从而得到一个有效地址

2)PC相对地址

This way of addressing is mainly used for transfer instruction to use,In transfer instruction has a16位的立即数,Will the two left and as a symbol to expand,And then combined with program counter register In order to gain the effective address

协处理器CPO

MIPS32Architecture provides the most4个协处理器CP0-CP3

CP0 Used for system control

CP1 CP3 Used as a floating point processing unit

CP2 Be retained for a specific implementation

MIPS32指令集架构简介

本书设计的处理器遵循MIPS32 Release 1架构,So this sectionMIPS32Instruction set architecture means theMIPS32 Release 1.

1.4.1 数据类型

The main task of the instruction is the operand arithmetic,The operands have different types and length,MIPS32Provide the basic data types as follows.

位(b):长度是1bit.

字节(Byte):长度是8bit.

半字(Half Word):长度是16bit.

字(Word):长度是32bit.

双字(Double Word):长度是64bit.

此外,还有32位单精度浮点数、64A double-precision floating-point number, etc.

1.4.2 寄存器

在前文介绍RISCThe characteristics of the point:大量使用寄存器.This is because the access to the register can be completed in one clock cycle,At the same time also simplifies the addressing mode.MIPS32Instructions in addition to the loading/Storage instructions,All number immediately register or use as operands.MIPS32There are two types of registers in the:通用寄存器(GPR:General Purpose Register)、特殊寄存器.

1、通用寄存器

MIPS32架构定义了32个通用寄存器,使用$0、$1……$31表示,都是32位.其中$0Generally used for constant0.

There is no force on hardware specified rules for use of the register,但是在实际使用中,这些寄存器的用法都遵循一系列约定,例如:寄存器$31General store subroutine return address.MIPS32In the terms of the general purpose register usage as table1-1所示.Most of the chapters in this book,The test program is written in assembly instructions directly,To the provisions of the register usage also don't need to care a lot,But the book's final chapter transplantμC/OS-II时,因为涉及到C语言、汇编混合编程,To the provisions of the register usage will need to care a lot.When readers to experience to the table1-1The role of each register agreed usage in.

2、特殊寄存器

MIPS32Architecture defined in the special register has three:PC(Program Counter程序计数器)、HI(, the high register)、LO(, the results of the low register).进行乘法运算时,HI和LO保存乘法运算的结果,其中HI存储高32位,LO存储低32位;进行除法运算时,HI和LOSave the result of the division,其中HI存储余数,LO存储商.

1.4.3 Byte order

The data is in accordance with the bytes in memory storage,The processor is in accordance with the instruction or data in bytes access memory,But if you need to read a word,也就是4个字节,Such as the reading is thatmem[n]、mem[n+1]、mem[n+2]、mem[n+3]这四个字节,So eventually there are two kinds of results to the processor.

{mem[n],mem[n+1],mem[n+2],mem[n+3]}

{mem[n+3],mem[n+2],mem[n+1],mem[n]}

The former is called the big end mode(Big-Endian),也称为MSB(Most Significant Byte),The latter is called the small end mode(Little-Endian),也称为LSB(Least Significant Byte).在大端模式下,数据的高位保存在存储器的低地址中,而数据的低位保存在存储器的高地址中.图1-4给出0x12345678In the two modes of storage situation.Book of the processor is big end mode(Big-Endian).

1.4.4 指令格式

MIPS32All the instructions are in the architecture32位,也就是32个0、1Coding together said an instruction,There are three kinds of instruction format.如图1-5所示.其中op是指令码、func是功能码.

(1)R类型:具体操作由op、funcCombined with the specified,rs和rtIs the source register number,rdIs the destination register number,比如:Assumes that the destination register is$3,那么对应的rd就是00011(This is a binary).MIPS32架构中有32个通用寄存器,使用5A coding can all said,所以rs、rt、rd的宽度都是5位.saOnly use in shift instruction,Used to specify displacement figures.

(2)I类型:具体操作由op指定,Instruction of low16位是立即数,To extend operation to32位,Then as one source to participate in the operation.

(3)J类型:具体操作由op指定,Usually jump instruction,低26Who is the word address,Used to generate a jump target address.

1.4.5 指令集

在“Simple to use computer model”中已经介绍过,可以直接使用0、1Coding for program design,But that is too inconvenient、容易出错,So some people use mnemonics to represent various instructions,This is the assembly instructions,Use the assembler translate assembly instructions for the computer can identify the0、1编码.And assembly instruction is translated into figure1-5所示的格式,So that the processor can recognize.MIPS32Architecture defined in the instructions can be divided into the following categories.注意:Not including floating-point instructions,Because book realize processor does not include the floating-point processing unit,There would be no realization of floating-point instructions,So don't introduce floating-point instructions here.

1、逻辑操作指令

有8条指令:and、andi、or、ori、xor、xori、nor、lui,实现逻辑与、或、异或、Or non arithmetic.Book design of the processor implements all logical operation instruction,将在第4、5Chapter introduces the logical operation instruction format、作用、用法,And its implementation process.

2、移位操作指令

有6条指令:sll、sllv、sra、srav、srl、srlv.Implementation logic left、右移、Arithmetic moves to the right and other operations.Book design of the processor implements all shift operation instruction,将在第5Chapter in detail each shift operation instruction format、作用、用法,And its implementation process.

3、Mobile operating instructions

有6条指令:movn、movz、mfhi、mthi、mflo、mtlo,Used for general purpose register data movement between,As well as general-purpose registers andHI、LORegister data movement between.Book design of the processor implements all mobile operating instructions,将在第6Chapter in detail various mobile operating instruction format、作用、用法,And its implementation process.

4、算术操作指令

有21条指令:add、addi、addiu、addu、sub、subu、clo、clz、slt、slti、sltiu、sltu、mul、mult、multu、madd、maddu、msub、msubu、div、divu,实现了加法、减法、比较、乘法、乘累加、除法等运算.Book design of the processor implements all arithmetic operation instructions,将在第7Chapter in detail each arithmetic operation instruction format、作用、用法,And its implementation process.

5、转移指令

有14条指令:jr 、jalr 、j 、jal、b、bal、beq、bgez、bgezal、bgtz、blez、bltz、bltzal、bne,Both unconditional jump,There is also a conditional transfer,Used for execution transferred to another place.Book design of the processor implements all transfer instruction,将在第8Chapter details the transfer instruction format、作用、用法,And its implementation process.

6、加载存储指令

有14条指令:lb、lbu、lh、lhu、ll、lw、lwl、lwr、sb、sc、sh、sw、swl、swr,以“l”Start is loading instruction,以“s”The start of the are stored instructions,These instructions to read data from memory,Or to save the data in memory.Book design of the processor implements all loading storage instructions,将在第9Chapter in detail various loading storage instruction format、作用、用法,And its implementation process.

7、Coprocessor access instructions

有2条指令:mtc0、mfc0,Used to read coprocessorCP0中某个寄存器的值,Or to save the data to the coprocessorCP0中的某个寄存器.Book design of the processor implements all coprocessor access instructions,将在第10Chapter introduces coprocessor、Coprocessor access instruction format、作用、用法,And its implementation process.

8、异常相关指令

有14条指令,其中有12The instruction to the,包括:teq、tge、tgeu、tlt、tltu、tne、teqi、tgei、tgeiu、tlti、tltiu、tnei,In addition to the system call instructionsyscall、异常返回指令eret.Book design of the processor implements all exceptions related instructions,将在第11Chapter introduces related instruction format、作用、用法,And its implementation process.

9、其余指令

有4条指令:nop、ssnop、sync、pref,其中 nop是空指令,ssnopIs a special type of empty instruction,syncInstructions to ensure load、Store operation order,prefCommands used to cache prefetching.Book design of the processor to this4Instruction and implement simplified,将在第5Chapter details the realization of the simplified process.

1.4.6 寻址方式

MIPS32架构的寻址模式有寄存器寻址、立即数寻址、寄存器相对寻址和PCRelative addressing four.其中寄存器相对寻址、PC相对寻址介绍如下.

(1)寄存器相对寻址

This addressing mode is mainly is to load/Storage instructions to use,其将一个16A number of immediate do sign extension,Then with a specified general-purpose registers values,从而得到有效地址,如图1-6所示.

(2)PC相对寻址

This addressing mode mainly transfer instruction to use,In transfer instruction has a16位的立即数,Move the left two and sign extension,Then with the program counter registerPC的值相加,从而得到有效地址.如图1-7所示.

1.4.7 协处理器CP0

协处理器一词通常用来表示处理器的一个可选部件,负责处理指令集的某个扩展,Have and are independent of the processor register.MIPS32Architecture provides the most4个协处理器,分别是CP0-CP3.协处理器CP0Used for system control,CP1、CP3Used as a floating point processing unit,而CP2Be retained for a specific implementation.除CP0Outside the coprocessor are optional.

协处理器CP0The specific role have:配置CPU工作状态、高速缓存控制、异常控制、Storage management unit control, etc.CP0Through the configuration of a series of internal registers to finish the work.Book design of the processor implementsCP0的部分功能,将在第10章详述.

1.4.8 异常

In the process of running,Will in turn to take out the instructions from memory,然后执行,But there are some events will interrupt normal program execution process,These events have a break(Interrupt)、陷阱(Trap)、系统调用(System Call)等等,统称为异常.异常发生后,Processor will transfer to a previously defined address,Have the exception handling routine at that address,在其中进行异常处理,This address is called the exception handling routine entry address.异常处理完成后,Using abnormal return instructionseret,返回到异常发生前的状态继续执行.Book design of the processor implements the hardware reset、中断(Contains softirqs、硬中断)、syscall系统调用、无效指令、溢出、Traps, etc.6Kind of exception handling,将在第11章详述.

---------------------

作者:leishangwen

边栏推荐

- 大佬们,请教一下,我看官方文档中,sqlserver cdc只支持2012版之后的,对于sqlser

- 系统提供的堆 VS 手动改写堆

- Compensation transaction and idempotency guarantee based on CAP components

- 随机快排时间复杂度是N平方?

- ERP不规范,同事两行泪 (转载非原创)

- 陈强教授《机器学习及R应用》课程 第十四章作业

- 造自己的芯,让谷歌买单!谷歌再度开源 180nm 工艺的芯片

- K个结点的组内逆序调整

- 批量读取word docx文件指定表格内容,保存在excel文件中

- About the handling of variable parameters in the Retrofit network request URL

猜你喜欢

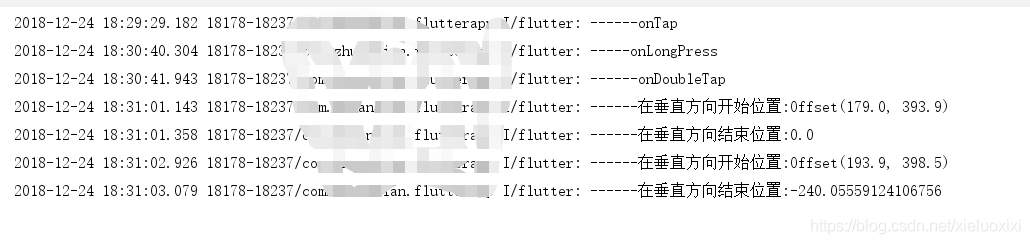

Flutter入门进阶之旅(七)GestureDetector

Fragment中嵌套ViewPager数据空白页异常问题分析

Flutter入门进阶之旅(八)Button Widget

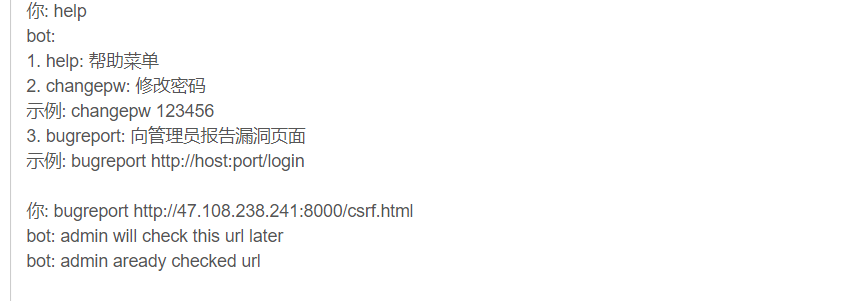

第六届“强网杯”全国网络安全挑战赛

#WeArePlay | 与更多开发者一起,探索新世界

Resolved IndentationError: unindent does not match any oute r indentation Level

新起之秀 DPU,正在掀起数据中心变革!

World's 4th mad scientist dies on his 103rd birthday

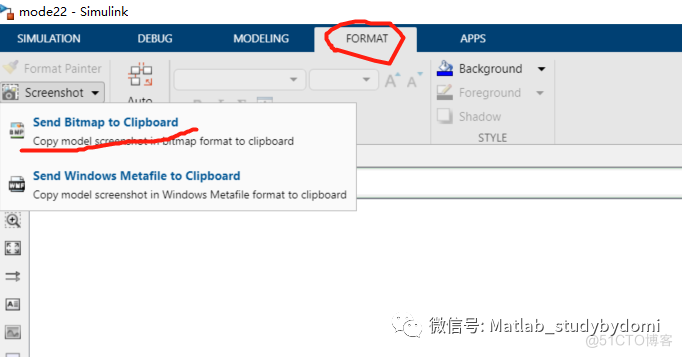

保存Simulink仿真模型为图片或者PDF的方法

Flutter entry and advanced tour (6) Layout Widget

随机推荐

5G Unicom Network Management Design Ideas

二叉树的序列化和反序列化

Bitmaps and bit operations

Flutter Getting Started and Advanced Tour (3) Text Widgets

GIN初探,环境安装

JVM内存泄漏和内存溢出的原因

Go 事,如何成为一个Gopher ,并在7天找到 Go 语言相关工作,第1篇

一维数组&指针

乐东消防救援大队应邀为干部开展消防安全培训

WebView注入Js代码实现大图自适应屏幕点击图片预览详情

2022年非一线IT行业就业前景?

Flutter Getting Started and Advanced Tour (8) Button Widget

注释、关键字、标识符的区别你知道吗?

技术分享 | 接口自动化测试如何处理 Header cookie

K个结点的组内逆序调整

卷积神经网络表征可视化研究综述(1)

两个链表相加

Flutter Getting Started and Advanced Tour (2) Hello Flutter

WebView injects Js code to realize large image adaptive screen click image preview details

kustomize入门示例及基本语法使用说明