当前位置:网站首页>VHDL 有限状态机(FSM) 代码示例

VHDL 有限状态机(FSM) 代码示例

2022-04-23 05:51:00 【Round moon】

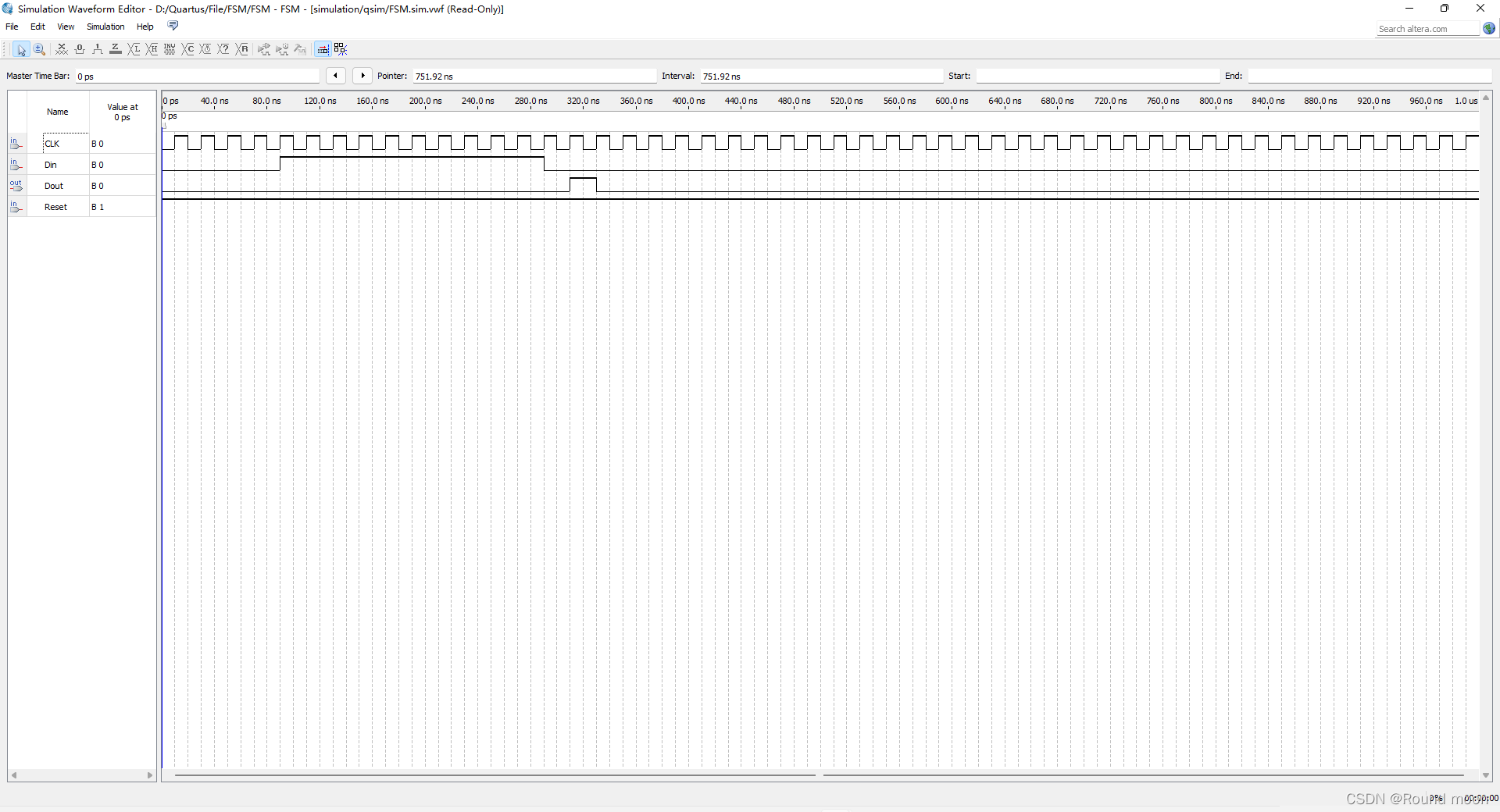

示例一 "10"检测器

library ieee;

use ieee.std_logic_1164.all;

entity FSM is

port(Din,CLK,Reset:in std_logic;Dout:out std_logic);

end FSM;

architecture behave of FSM is

type state is(S0,S1,S2);

signal currentstate: state:=S0;

signal nextstate:state:=S0;

begin

state_trans:process(Din,currentstate)

begin

case currentstate is

when S0=>if Din='1' then nextstate<=S1;else nextstate<=S0;end if;

when S1=>if Din='0' then nextstate<=S2;else nextstate<=S1;end if;

when S2=>if Din='0' then nextstate<=S0;else nextstate<=S1;end if;

end case;

end process;

state_latch:process(CLK,reset)

begin

if reset='0' then

currentstate<=S0;

else

if CLK'event and CLk='1' then

currentstate<=nextstate;

end if;

end if;

end process;

Dout<='1' when currentstate=S2 else '0';

end behave;

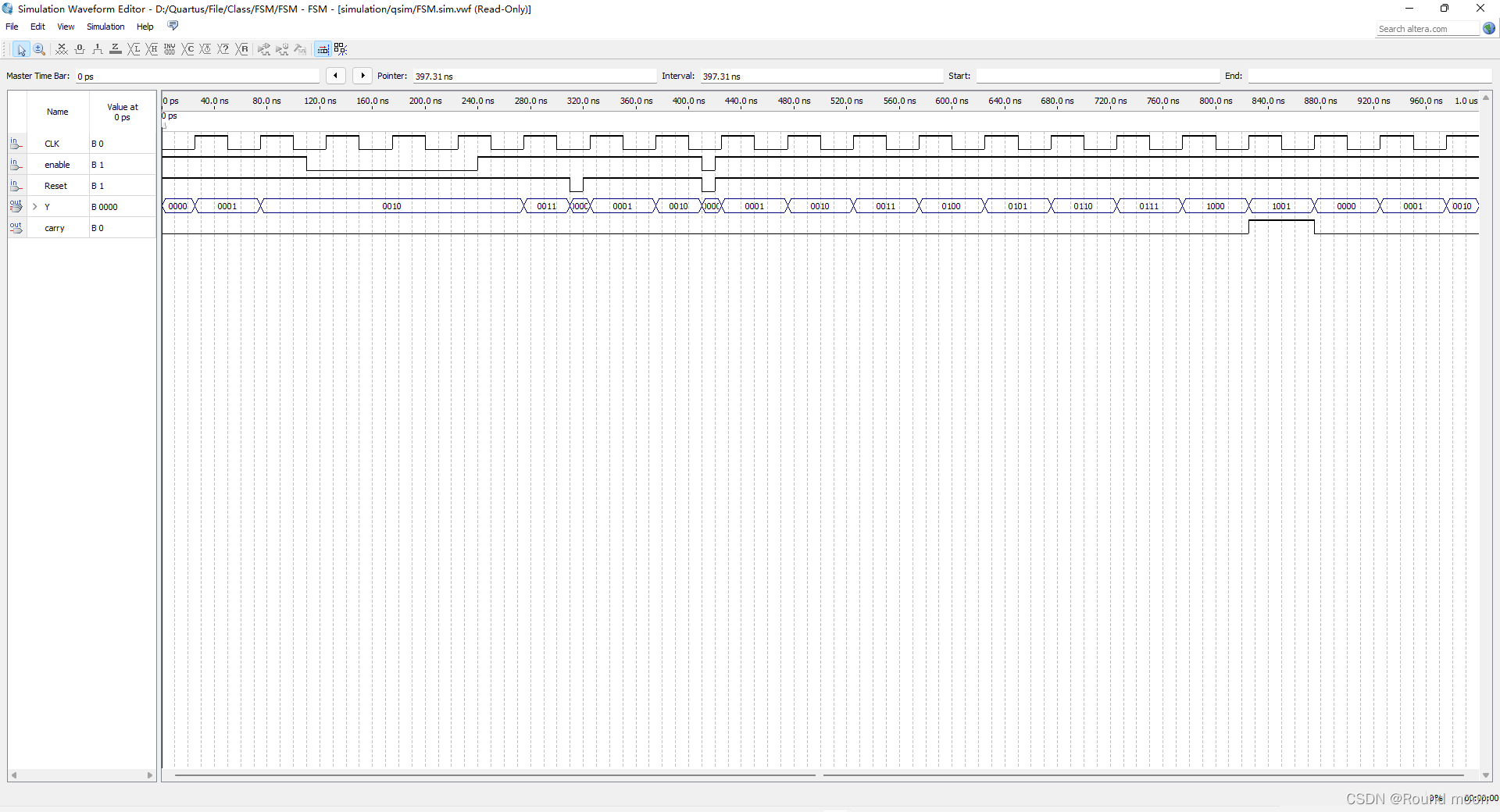

示例二 十进制计数器

library ieee;

use ieee.std_logic_1164.all;

entity FSM is

port(CLK,Reset,enable:in std_logic;Y:out std_logic_vector(3 downto 0);carry:out std_logic);

end FSM;

architecture behave of FSM is

type state is(S0,S1,S2,S3,S4,S5,S6,S7,S8,S9);

signal currentstate:state:=S0;

signal nextstate:state:=S0;

begin

process(currentstate)

begin

case currentstate is

when S0=>if enable='1' then nextstate<=S1;else nextstate<=S0;end if;

when S1=>if enable='1' then nextstate<=S2;else nextstate<=S1;end if;

when S2=>if enable='1' then nextstate<=S3;else nextstate<=S2;end if;

when S3=>if enable='1' then nextstate<=S4;else nextstate<=S3;end if;

when S4=>if enable='1' then nextstate<=S5;else nextstate<=S4;end if;

when S5=>if enable='1' then nextstate<=S6;else nextstate<=S5;end if;

when S6=>if enable='1' then nextstate<=S7;else nextstate<=S6;end if;

when S7=>if enable='1' then nextstate<=S8;else nextstate<=S7;end if;

when S8=>if enable='1' then nextstate<=S9;else nextstate<=S8;end if;

when S9=>if enable='1' then nextstate<=S0;else nextstate<=S9;end if;

end case;

end process;

process(clk,reset)

begin

if reset='0' then

currentstate<=S0;

elsif CLK'event and CLK='1' then

if enable='1' then

Currentstate<=nextstate;

end if;

end if;

end process;

with currentstate select

Y<="0000" when S0,

"0001" when S1,

"0010" when S2,

"0011" when S3,

"0100" when S4,

"0101" when S5,

"0110" when S6,

"0111" when S7,

"1000" when S8,

"1001" when S9;

carry<='1' when currentstate=S9 else '0';

end behave;

By-Round Moon

版权声明

本文为[Round moon]所创,转载请带上原文链接,感谢

https://blog.csdn.net/qq_35339563/article/details/123723641

边栏推荐

- Shell脚本 单引号、双引号和反引号的区别

- [UDS unified diagnostic service] III. application layer protocol (1)

- Round up a little detail of the round

- C语言实用小技巧合集(持续更新)

- [UDS unified diagnosis service] i. diagnosis overview (2) - main diagnosis protocols (K-line and can)

- 产生随机数

- [stepping on the pit] MELD in win11 wsl2 cannot be used normally. Problem repair

- C51/C52 特殊功能寄存器表

- 【UDS统一诊断服务】一、诊断概述(1)— 诊断概述

- C语言的运算符

猜你喜欢

随机推荐

【UDS统一诊断服务】三、应用层协议(1)

[ThreadX] ThreadX source code reading plan (I)

Graduation project, curriculum link, student achievement evaluation system

vs中的多字节与unicode

cuda工程更换环境(电脑)后遇到的一系列编译问题

函数的调用过程

C语言中volatile的使用

Shell脚本 单引号、双引号和反引号的区别

jenkspy包安装

Shell脚本 &&和||的使用

PM2 deploy nuxt project

[learn] HF net training

C语言进阶要点笔记3

FOC 单电阻采样 位置环控制伺服电机

Installation of GCC, G + +, GDB

vs中能编译通过,但是会有红色下划线提示未定义标示符问题

基于VGG卷积神经网络的图像识别代码实现

C语言的浪漫

在MFC中使用printf

Round up a little detail of the round

![[ThreadX] h743 + ThreadX + Filex migration record](/img/5b/6796335fd9deeee878cad3e21ab2d9)