当前位置:网站首页>FPGA-近日工作总结

FPGA-近日工作总结

2022-08-09 12:35:00 【51CTO】

工作概述:

1)看《电子技术基础》和《fpga数字逻辑设计》学习数字电路的组合逻辑部分,卡诺图的化简和降维法。

2)复习加法器,全加器,译码器,编码器,数据选择器,数值比较器,巩固这些组合逻辑的工作原理以及用verilog在ISE的实现。

3)看《verilog基本语法》学习和巩固verilog的基本语法。

1.摘抄:

组合电路某一时刻的输出仅与该时刻的输入有关,而与电路前一时刻的状态无关。

组合电路的特点

1) 电路由逻辑门构成,不含记忆元件

2) 输出与输入间无反馈延迟回路

3) 输出与电路原来状态无关

当一逻辑门的两个输入端同时向着相反方向变化,而变化的时间有差异。这种现象称作竞争。由于竞争产生的输出干扰脉冲的现象称作为冒险。

-《电子技术基础》和数电ppt

1.理解:

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

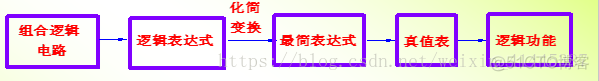

逻辑电路的设计的基本思路:

1)分析实际问题的实际功能

2)根据实际需要写出真值表

3)根据真值表来写出逻辑表达式

4)根据卡诺图来化简表达式来避免产生竞争冒险

2.摘抄:

如何理解这里说的冒险与竞争?

首先来说产生冒险与竞争的原因:当我们在数字逻辑电路中,我们认为电路的输入输出都是平稳的逻辑电平,但是信号在实际的传递中,经过逻辑电路需要一定的时间。或者因为门的延时的差异,将会出现和稳态情况不同的状态,产生输出错误,这就叫电路中的竞争冒险。

--《电子技术基础》

2.理解:

冒险不一定会对实际的输出逻辑有影响,但是为了避免冒险竞争的情况出对死实际电路中的输入输出产生影响,应该尽量避免这样的情况出现。在逻辑设计时候,在PC端进行仿真模拟时体现不出来他的作用,但是在实际工作操作中,这个是不可忽略的。

那么就总结一下消除竞争冒险的方法:

1)发现并消去互补相乘项。

2)增加乘积项避免互补项相加。

3)输出端并联电容器。

3.摘抄:

正因为组合逻辑和时序逻辑的逻辑上的功能特点所以组合逻辑电路使用阻塞赋值,时序逻辑电路使用非阻塞赋值。

什么是阻塞赋值和非阻塞赋值

阻塞赋值操作符用等号(即 = )表示。“阻塞”是指在进程语句(initial和always)中,当前的赋值语句阻断了其后的语句,也就是说后面的语句必须等到当前的赋值语句执行完毕才能执行。

非阻塞赋值操作符用小于等于号 (即 <= )表示。“非阻塞”是指在进程语句(initial和always)中,当前的赋值语句不会阻断其后的语句,可以简单理解为几条非阻塞赋值语句可以同时执行。

非阻塞赋值操作过程:

1)在赋值开始时刻,计算非阻塞赋值右边表达式。

2)在赋值结束时刻,更新非阻塞赋值左边表达式。

-《verilog基本语法》

3.理解:

EG:如果a=3 b=8;a=b,c=a;

- 如果阻塞赋值第一条执行的时候a的值立刻变为了a=8;执行第二条的时候c=8;

- 如果是非阻塞赋值的方式根据非阻塞赋值的操作过程:计算开始计算出右边的值分别为8 3,第二步刷新左边表达式的值则a=8 c=3;

4.摘抄:

Memory型变量

尽管memory型数据和reg型数据的定义格式很相似,但是要注意不同之处。Memory描绘的是深度,reg描绘的是宽度。

Reg [ n-1:0 ] rega; //一个n位寄存器

Reg mema [ n-1 ] //一个由n个一位寄存器组成的存储器组

一个n位的寄存器可以在一条赋值语句里进行赋值。而一个完整的存储器不行

Rega = 0;//合法的赋值语句

Mema=0;//非法的赋值语句

Mema[3]=0;//合法,给memory中的第三个单元赋值为0

边栏推荐

猜你喜欢

西湖大学教授怎么看AI制药革命?|量子位智库圆桌实录

1小时直播招募令:行业大咖干货分享,企业报名开启丨量子位·视点

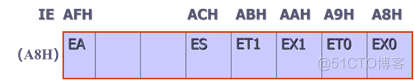

中断系统结构及中断控制详解

腾讯欲成育碧最大股东/ 米哈游招NLP内容生成研究员/ AI发现四千余物种濒临灭绝...今日更多新鲜事在此...

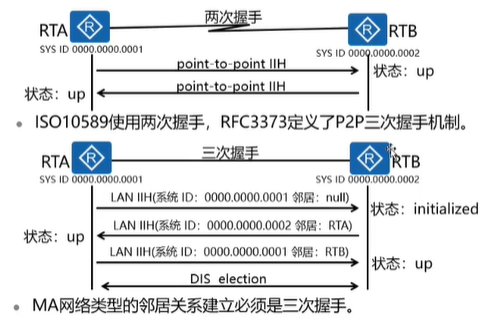

【HCIP持续更新】IS-IS协议原理与配置

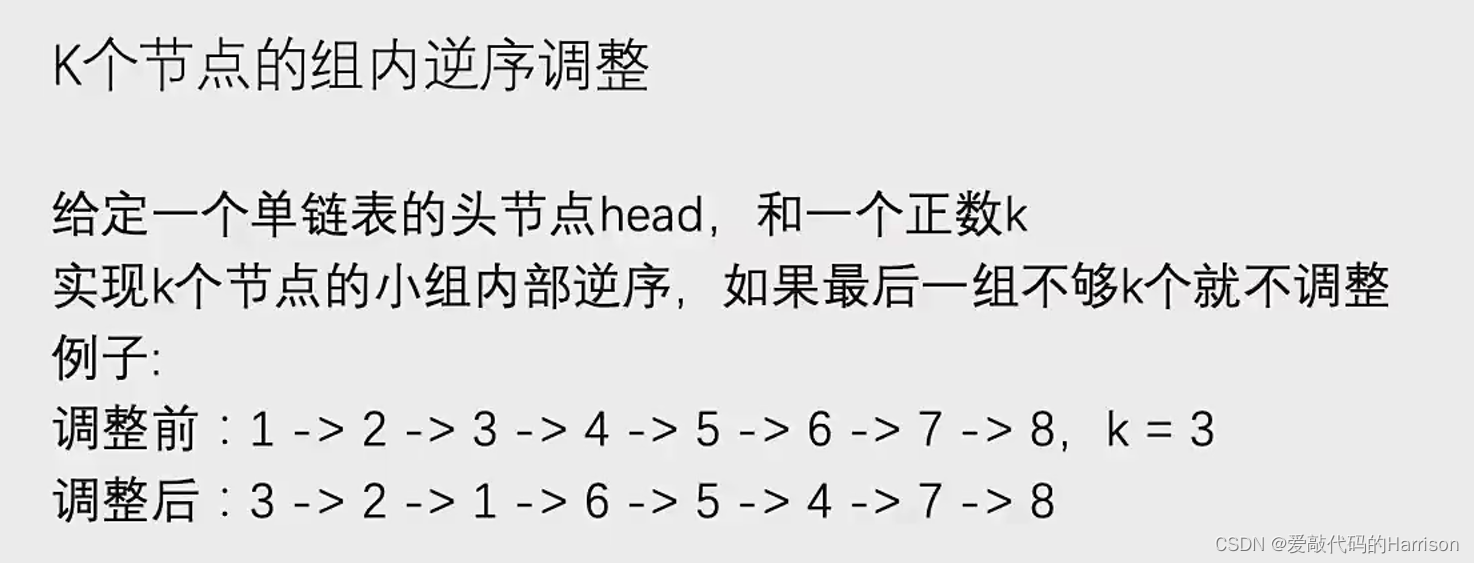

K个结点的组内逆序调整

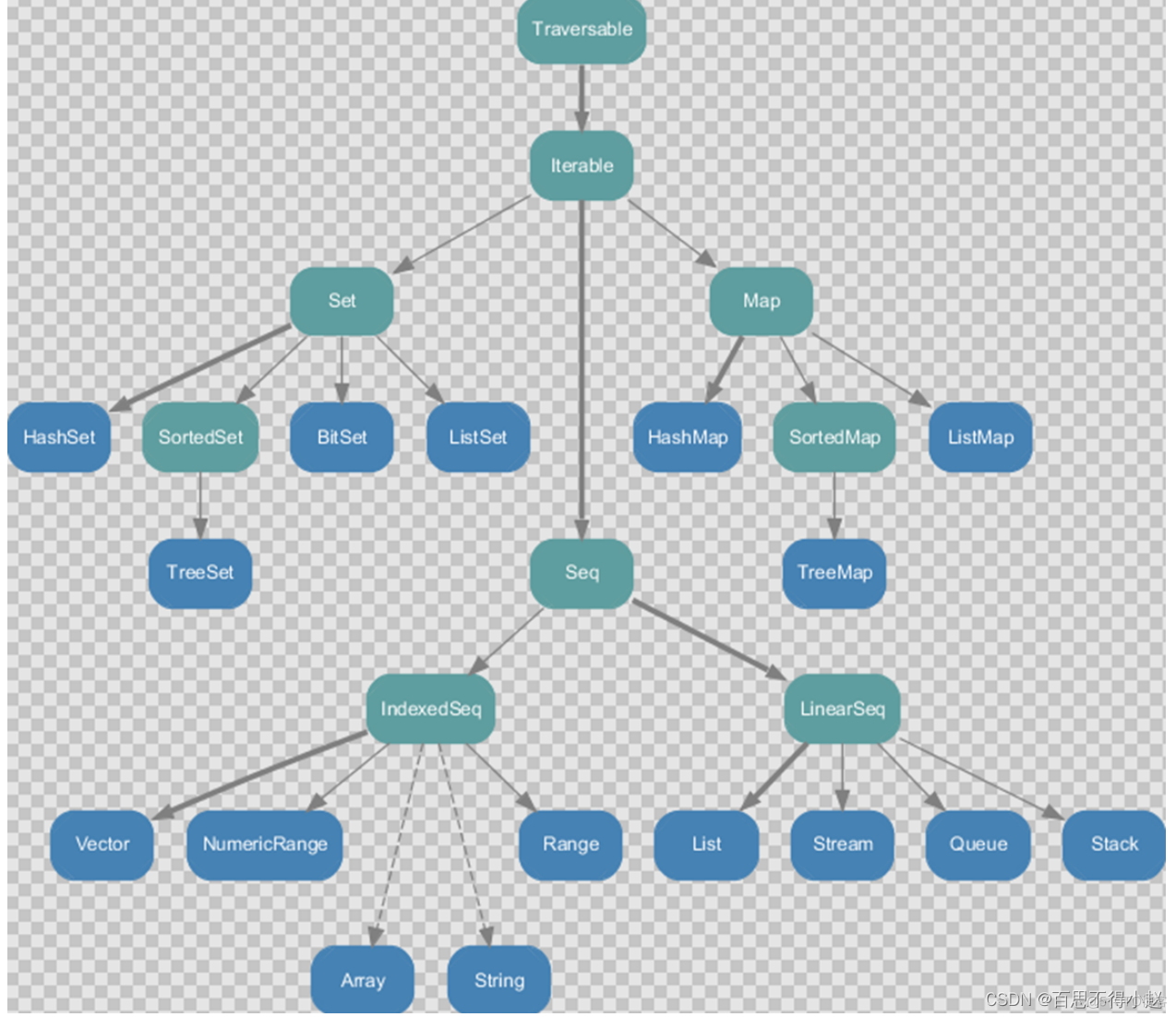

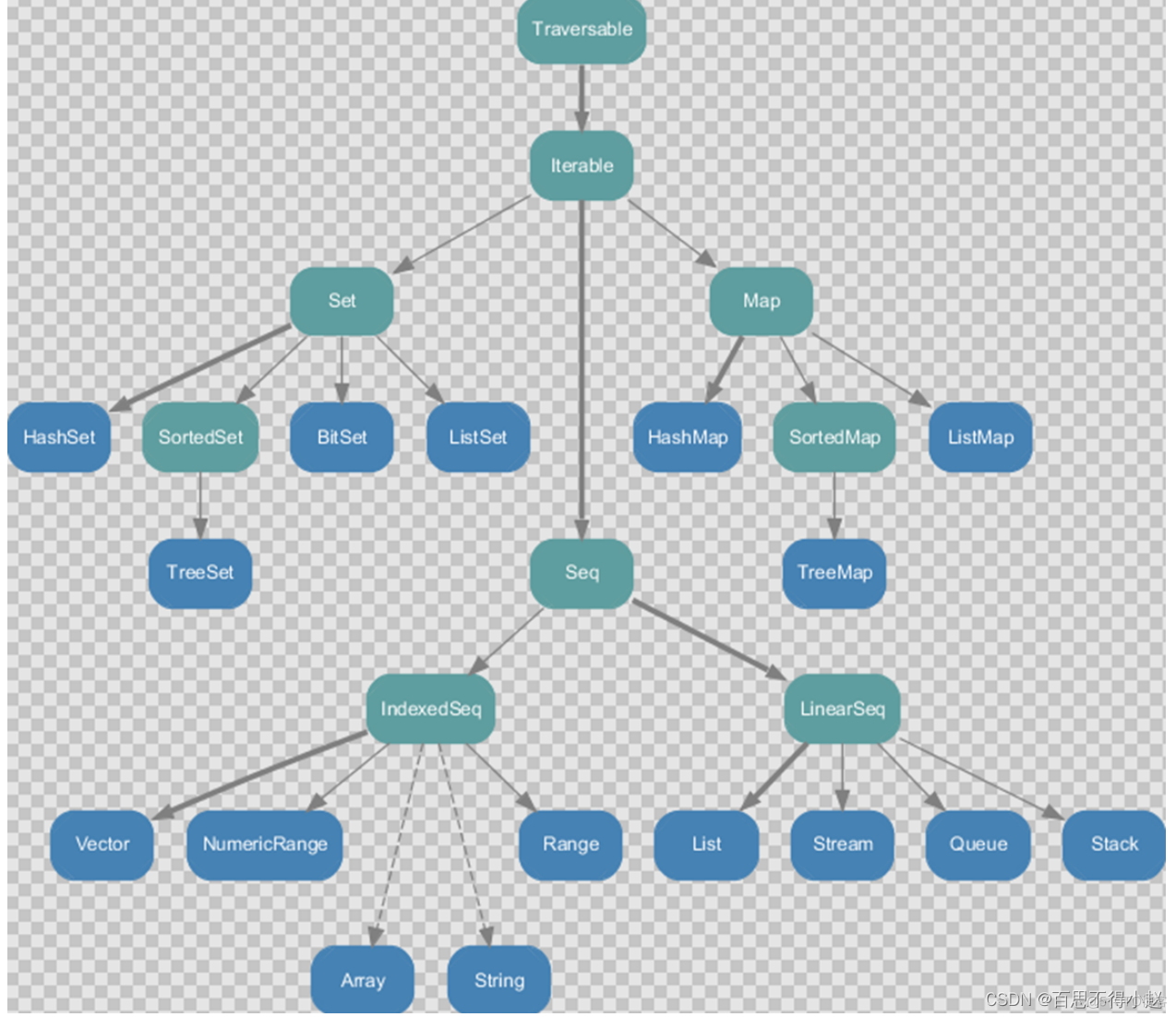

Scala Advanced (7): Collection Content Summary (Part 1)

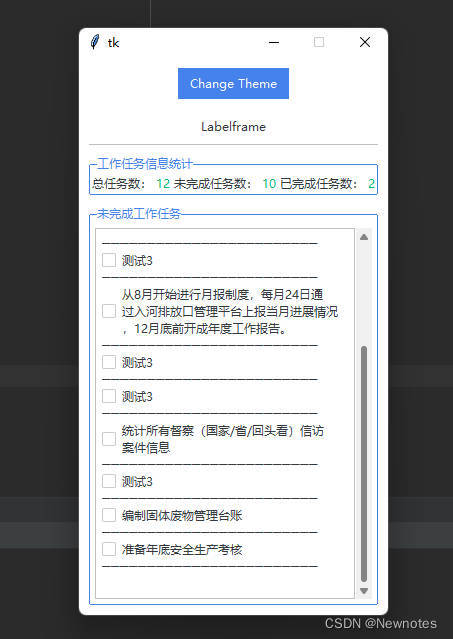

工作任务统计

Scala 高阶(七):集合内容汇总(上篇)

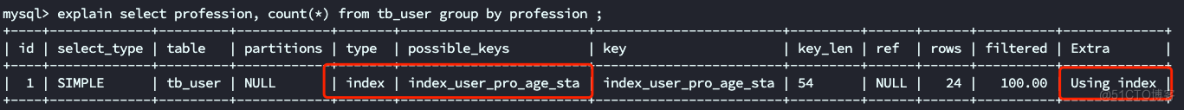

MySQL principle and optimization of Group By optimization techniques

随机推荐

两分钟录音就可秒变语言通!火山语音音色复刻技术如何修炼而成?

生成上传密钥和密钥库

数据挖掘-06

Go-based web access parameters

Intra-group reverse order adjustment of K nodes

在北极都可以穿短袖了,温度飙升至32.5℃

Nature:猪死亡1小时后,器官再次运转

Data Mining-05

Two minutes recording can pass by second language!The volcano how to practice and become voice tone reproduction technology?

罗振宇折戟创业板/ B站回应HR称用户是Loser/ 腾讯罗技年内合推云游戏掌机...今日更多新鲜事在此...

手写大根堆

面试题精选:神奇的斐波那契数列

苹果Meta都在冲的Pancake技术,中国VR团队YVR竟抢先交出产品答卷

Flutter入门进阶之旅(六)Layout Widget

ViewPager fragments of nested data blank page abnormal problem analysis

一维数组&指针

使用注解将EventBus封装抽取到基类

注释、关键字、标识符的区别你知道吗?

Rust从入门到精通04-数据类型

Flutter入门进阶之旅(一)-初识Flutter