当前位置:网站首页>Clock frequency and baud rate count for serial communication in FPGA

Clock frequency and baud rate count for serial communication in FPGA

2022-08-09 13:44:00 【fpga and matlab】

Table of Contents

3. The relationship between the counter frequency division of the clock frequency and the baud rate

1. What is a waveBit rate

The baud rate bandrate refers to the rate of serial communication, that is, how many binary bits can be transmitted per second during serial communication.For example, 9600 bits can be transmitted per second (the time required to transmit one binary bit is 1/9600 second), and the baud rate is 9600.

The communication baud rate of the serial port cannot be set arbitrarily because:

First, both parties must set the same baud rate in advance so that they can communicate successfully. If the sender and receiver communicate according to different baud rates, they will not receive it at all, so the baud rate is best known to everyone.rather than arbitrarily specified.

Second: The commonly used baud rate has been developed for a long time, and a consensus has been formed. The commonly used baud rate is 9600 or 115200.

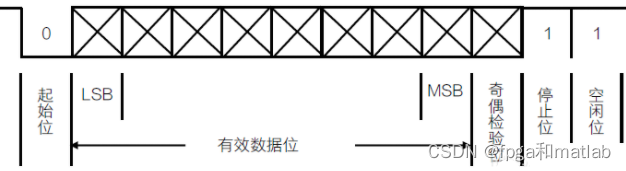

2.Serial transmission format

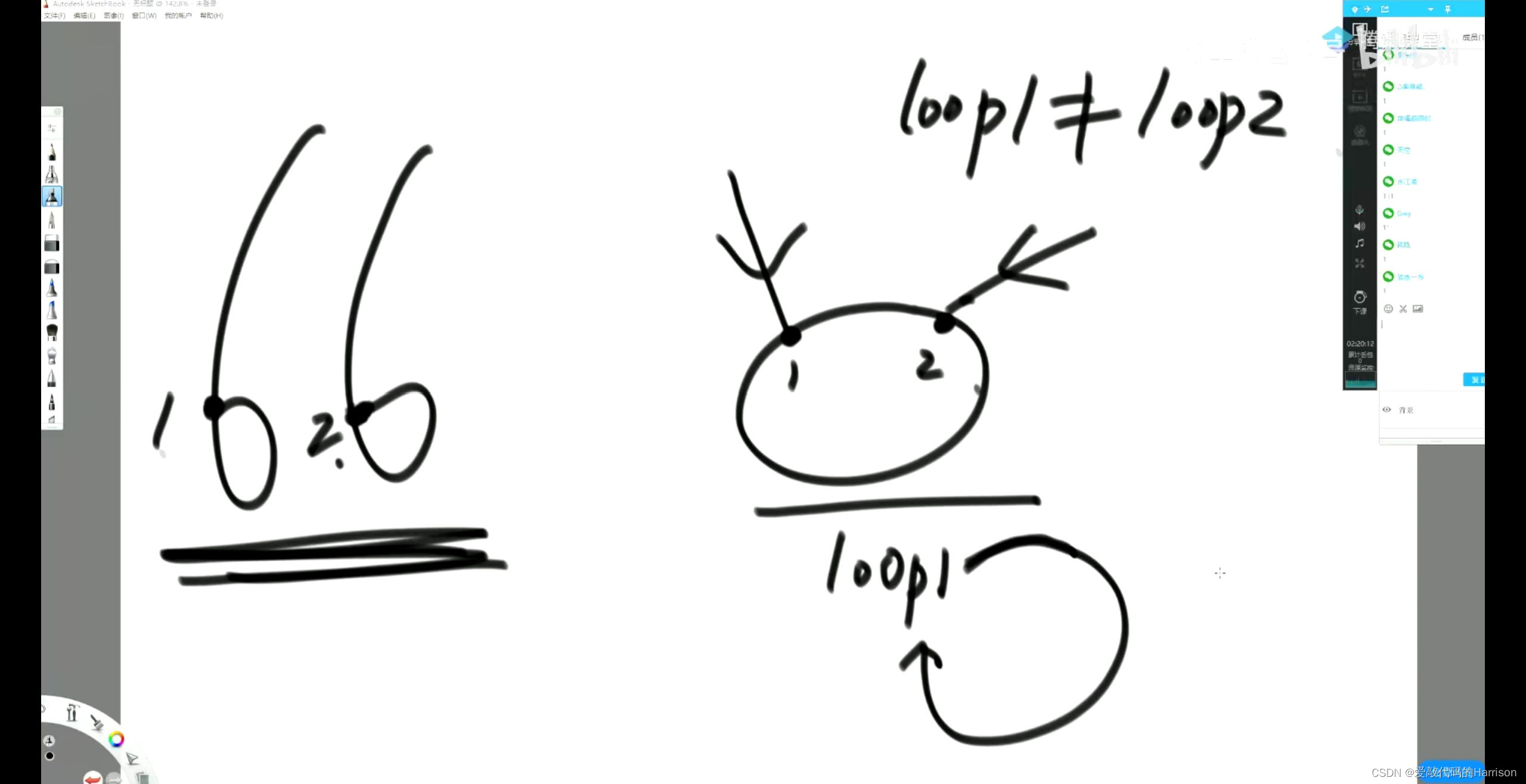

The serial transmission format is generally as follows:

It includes a 1bit start bit + 8bit data bit + 1bit stop bit (no parity bit)

3.The relationship between the counter frequency division of the clock frequency and the baud rate

In FPGA, since the clock frequency is generally fixed at 50MHz, 100MHz, in serial communication, the clock frequency needs to be divided so that the clock frequency is approximately equal to the baud rate.

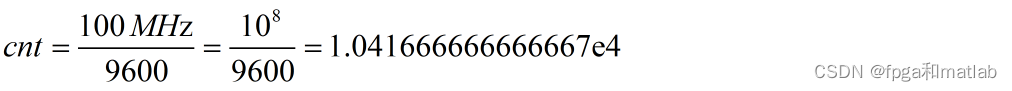

We assume that the clock frequency of the FPGA hardware board is 100Mhz, if the required baud rate is 9600, then the frequency division process of the clock is as follows:

First, calculate the number of continuous clock cycles corresponding to the transmission of 1 bit:

Approximately equal to 10417.

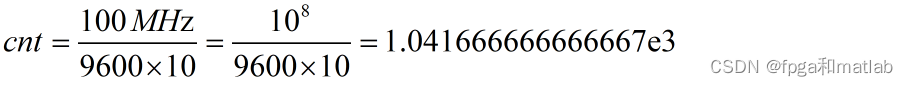

According to the above serial port transmission structure diagram, a complete serial port frame, assuming that the parity check is not considered, requires 10 bits, so the corresponding counter value is:

So, set the counter frequency division value of the clock to 1042.

边栏推荐

- 第六届”蓝帽杯“全国大学生网络安全技能大赛 半决赛

- WSA工具箱安装应用商店提示无法工作怎么解决?

- CPU-MIPS32指令架构(无内锁流水线微处理器)

- How to reduce the size of desktop icons after the computer is reinstalled

- About the handling of variable parameters in the Retrofit network request URL

- Intranet penetration tool ngrok usage tutorial

- Flutter入门进阶之旅(七)GestureDetector

- Jenkins API groovy调用实践: Jenkins Core Api & Job DSL创建项目

- 安踏携手华为运动健康共同验证冠军跑鞋 创新引领中国体育

- 如何修改data work上jdbc驱动的版本

猜你喜欢

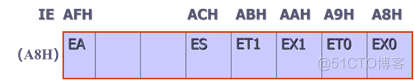

中断系统结构及中断控制详解

FPGA-近日工作总结

安踏携手华为运动健康共同验证冠军跑鞋 创新引领中国体育

第六届”蓝帽杯“全国大学生网络安全技能大赛 半决赛

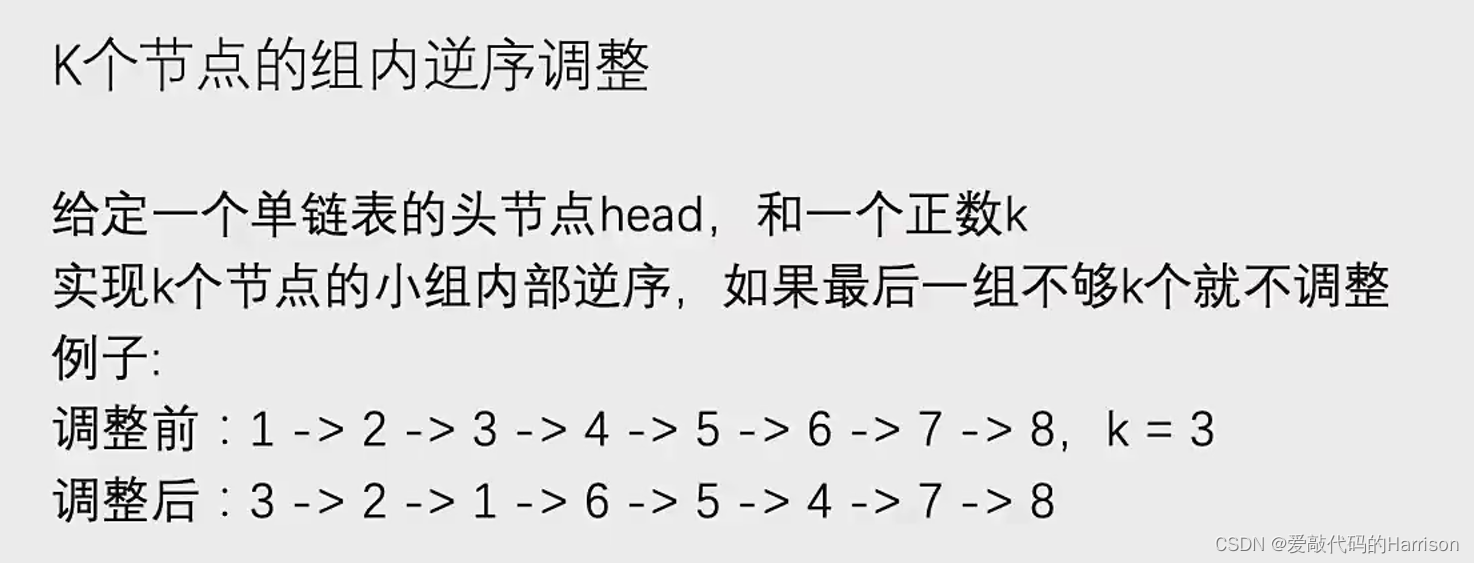

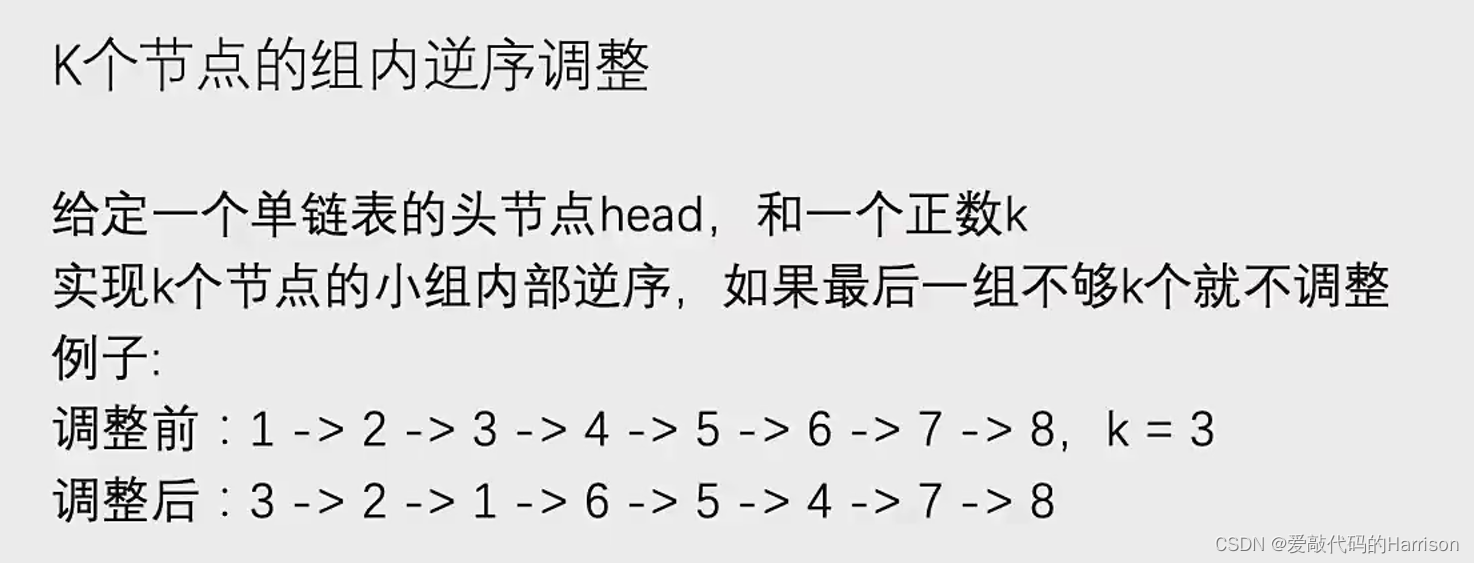

Intra-group reverse order adjustment of K nodes

K个结点的组内逆序调整

链表噩梦之一?5000多字带你弄清它的来龙去脉

AI basketball referee, walking is special, ask harden care don't care

第六届“强网杯”全国网络安全挑战赛

Go Affair, How to Become a Gopher and Find a Go Job in 7 Days, Part 1

随机推荐

Redis源码剖析之字典(dict)

ViewPager fragments of nested data blank page abnormal problem analysis

Glory to the Blue Yonder, speeds up the strategic growth

流量焦虑背后是企业对客户关系管理的不足

[FPGA Tutorial Case 48] Image Case 8 - Realization of Converting RGB Image to HSV Image Based on FPGA, Assisted Verification by MATLAB

腾讯发布第二代四足机器人Max,梅花桩上完成跳跃、空翻

read stream special attention

leetcode 20. Valid Parentheses 有效的括号(中等)

Ten minutes to teach you how to use VitePress to build and deploy a personal blog site

陈强教授《机器学习及R应用》课程 第十三章作业

Rust从入门到精通04-数据类型

合并两个有序列表

联通网管协议框图

在已打开图片上加水印(文字)

30行代码实现微信朋友圈自动点赞

造自己的芯,让谷歌买单!谷歌再度开源 180nm 工艺的芯片

GIN中GET POST PUT DELETE请求

无重复字符的最长子串

Compensation transaction and idempotency guarantee based on CAP components

十六进制字符→十进制数字