当前位置:网站首页>HyperLynx(五)反射仿真

HyperLynx(五)反射仿真

2022-08-11 11:01:00 【小幽余生不加糖】

反射仿真

1.学过物理的工程师都知道,光在传输过程中不在介质的表面会发生反射和折射现象,如图所示。同样,对于信号而言,信号在传递的的过程中,遇到阻抗不连续的点(不同的介质或不同的物理结构时),一部分信号会产生反谢,另一部分信号继续传递。信号反射是信号完整性当中非常重要的一个课题,也是非常普遍和严重的一个问题。

如图所示是一个信号在高速电路中传递互连链路的简单示意图,,包含发送端、接收端、PCB、过孔、分立器件、连接器/线缆等。

信号从发送端芯片内部发送出来,一直到另外一颗芯片I/O口接收,需要经过链路传输,这可能会存在很多的阻抗不连续点,如口芯片与 PCB 的焊盘、换层的过孔、连接器与

PCB 的焊盘、连接器、分立元器件等。另外传输线本身存在的分支、传输线的拓扑结构、 芯片的输出阻抗与传输线本身可能存在阻抗不匹配等,这些情况都有可能造成信号的反射。

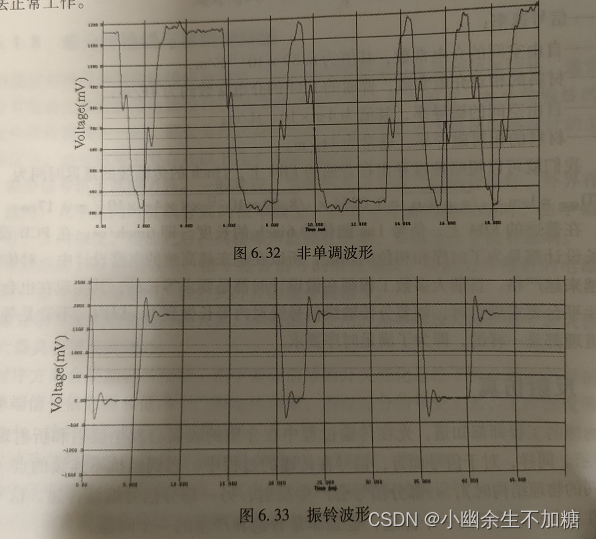

阻抗不连续会引起信号的反射,信号的反射也会带来很多信号完整性问题,如过冲、非单调、振铃等,如图所示为队组抗不连续导致的非单调波形和振铃的波形,非单调和振铃现象又会导致信号完整性质量和日时序的问题,进而导致系统工作时误码率增多或者无法正常工作。

2.反射阶梯图

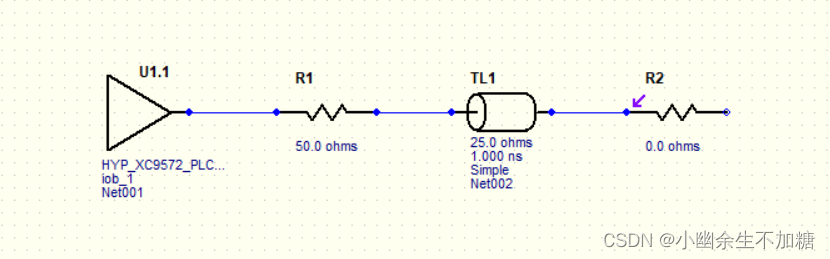

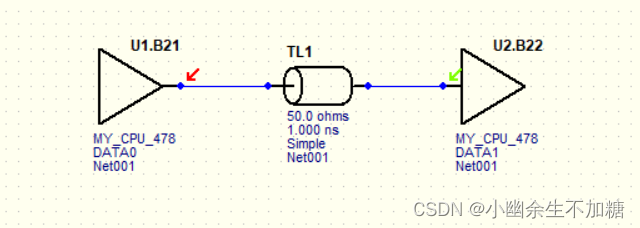

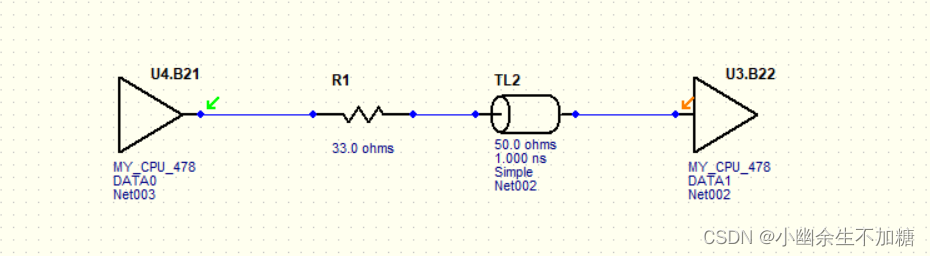

在反射中有一个比较著名的反射阶梯图实验,在LineSim中搭建拓扑结构如图所示:

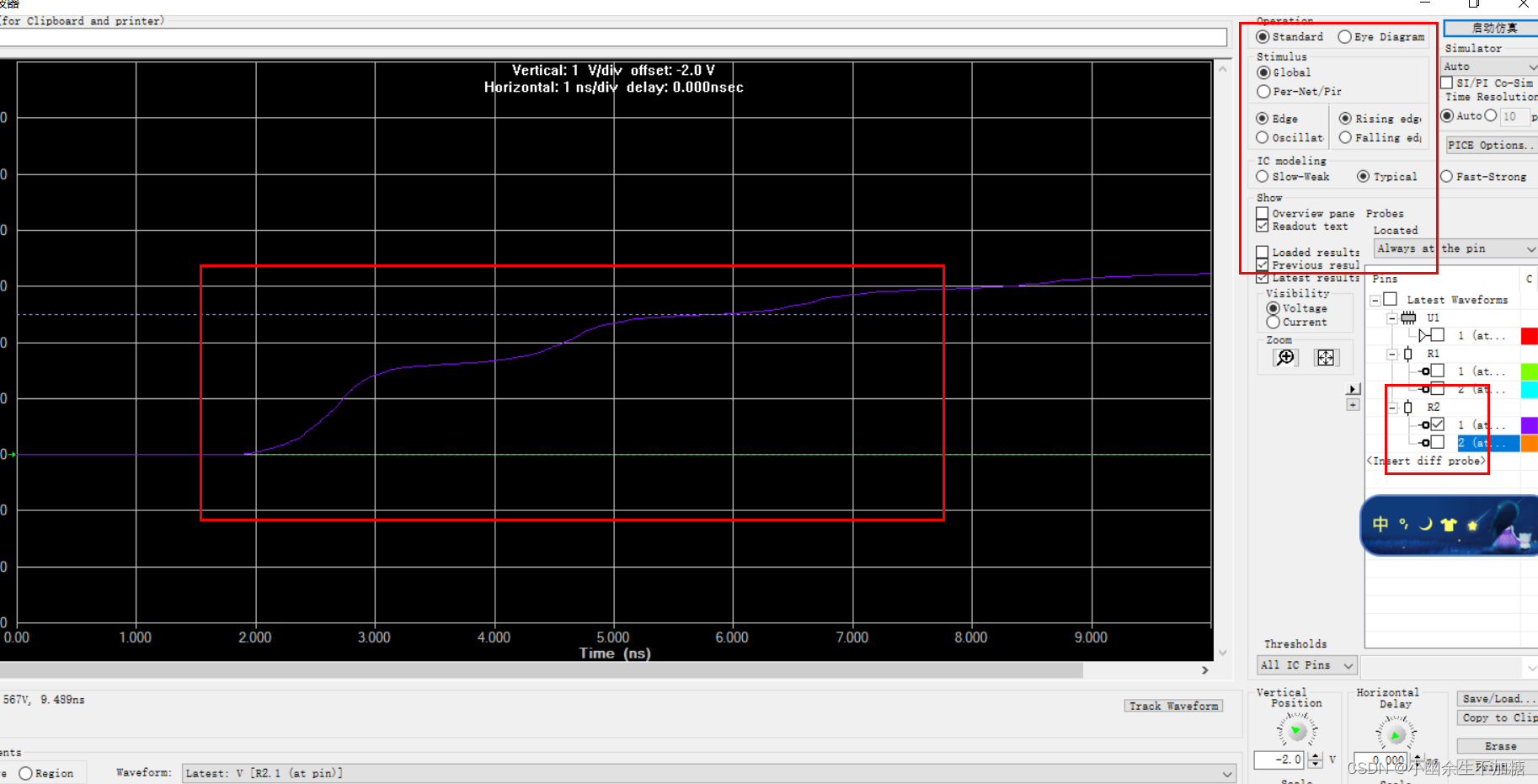

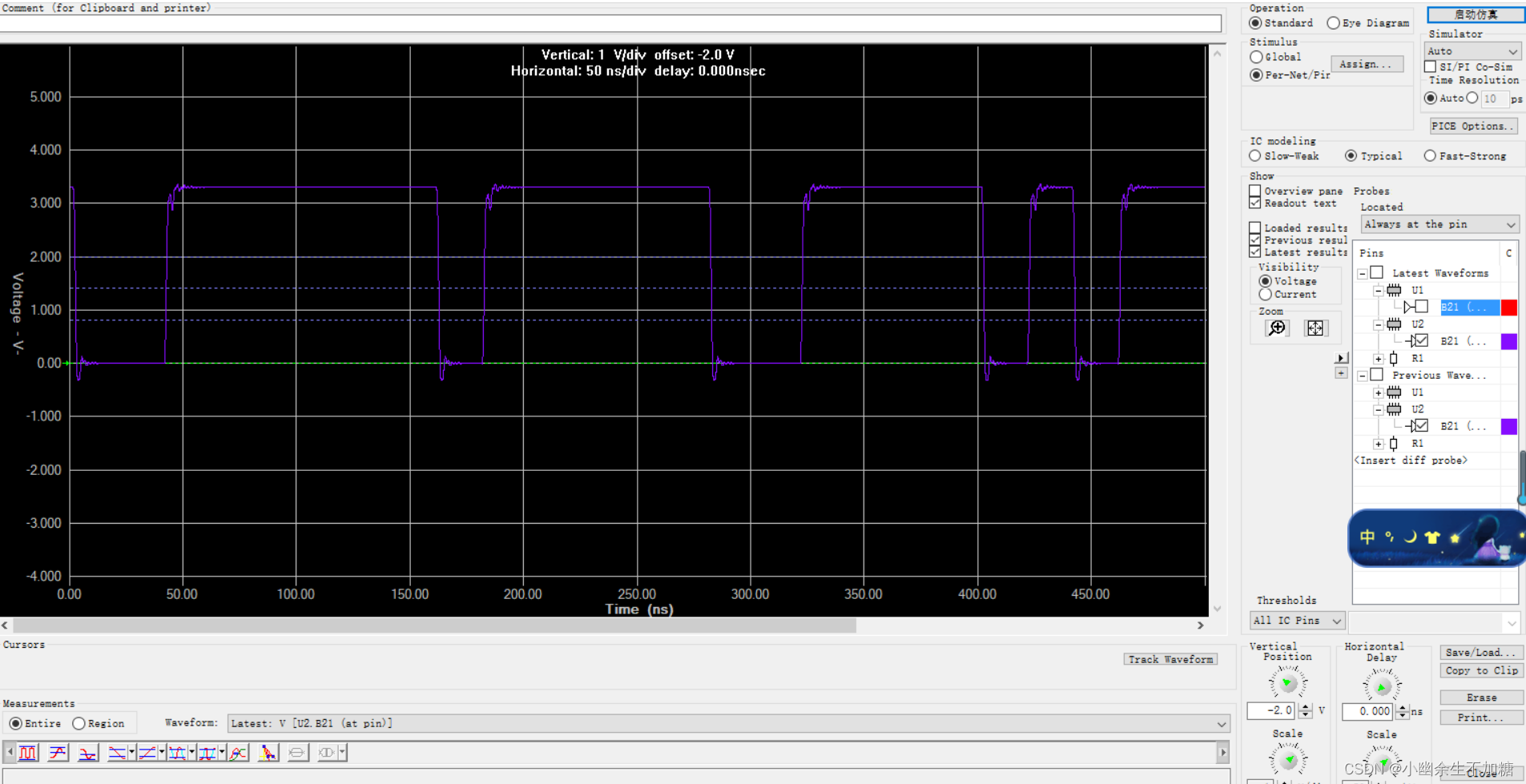

仿真设置和仿真结果如图所示:

从仿真曲线中可以看到,随着时间的推移,在R2处观察的幅值随着多次叠加后会趋于稳定,以达到 源端发送信号的幅值。

3.短桩线的反射

在前面中,主要考虑的是阻抗不连续点,其实反射不仅是因为阻抗不连续造成的,还有很多不规范的设计也会造成信号的反射。例如, 有的工程师在设计过程中,总会一不小心多出一部分布线线头,或者为了兼容设计,也会留有一些开路的线头。这些线头通常称为短桩线或残桩线,如图中的传输线 TL2。

短桩线拓扑结构

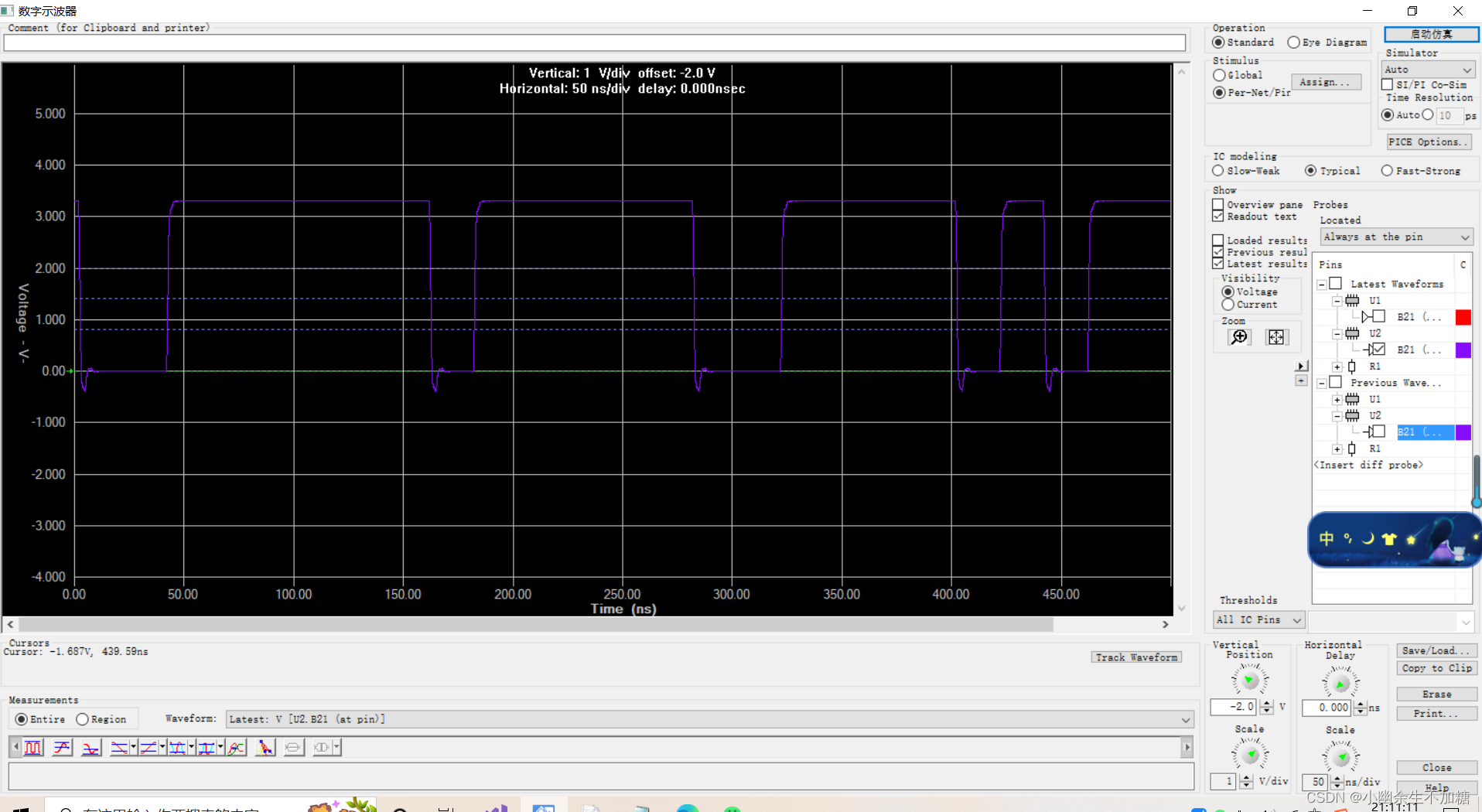

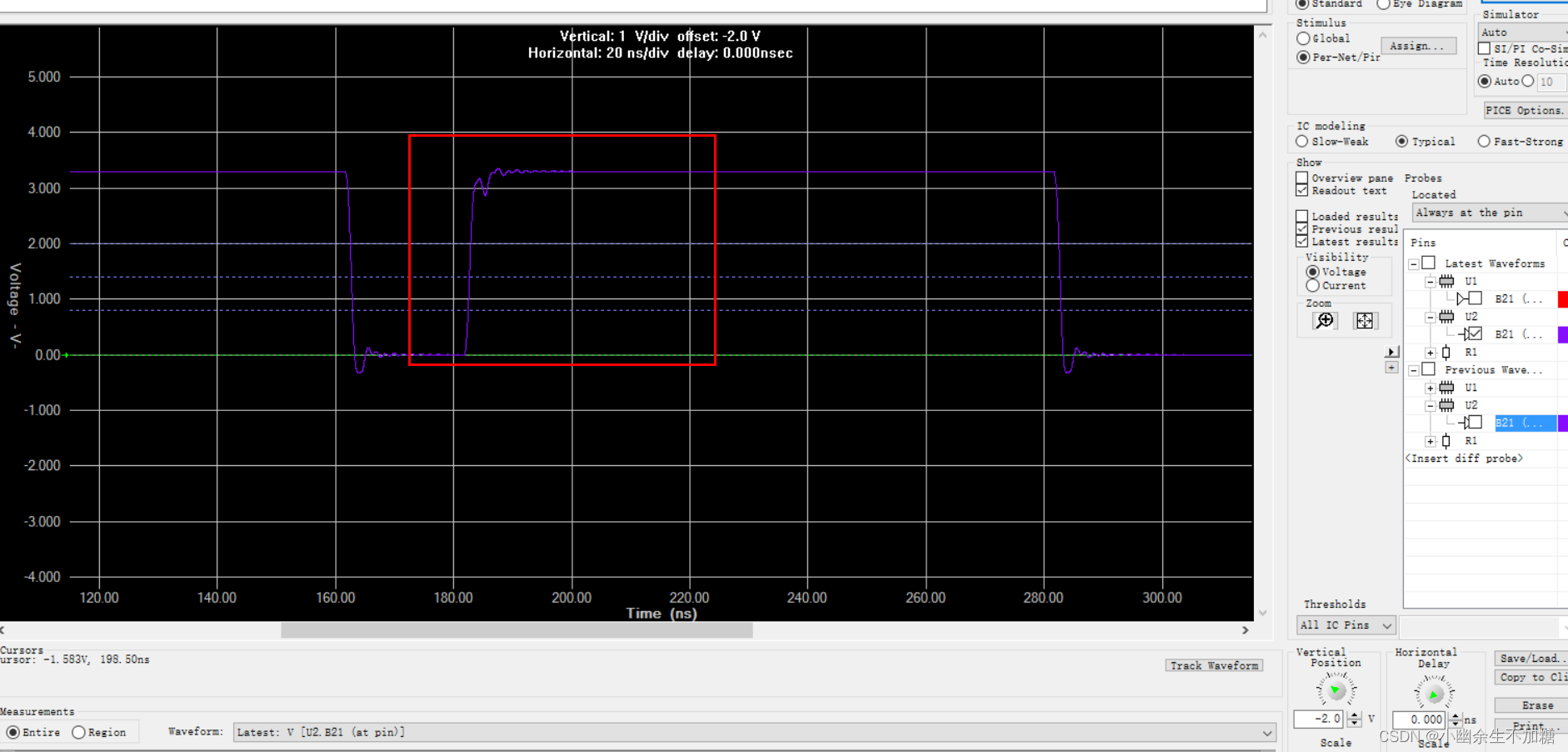

短桩线仿真获得的波形如图所示:

无短桩线时候的波形:

对比可以看到去掉短桩线和加上短桩线相比,短桩线存在时,接收端的波形存在振铃现象。问题就是当振铃大到一定程度时,就可能造成对门限电平的误触发。

4.如何消除反射

既然反射会造成很多信号完整性的问题,那么如何解决反射的问题或减少反射对信号完整性的影响?工程师在分析这些问题时,需要从导致反射问题的原因着手。

第一,如前面中的短桩线存在的问题导致的反射,就可以从设计上找原因,是否必须保留短桩线,如果不是,去掉短桩线就可以解决反射的问题。

第二,PCB设计导致反射。例如,芯片与 PCB 连接点、传输线换层过孔、连接器与 PCB的连接点等。这种情况下可以通过优化PCB设计,使阻抗尽量与传输线的阻抗一致或接近。这种反射只能尽量减少,很难被消除。

第三、电路设计导致的反射。通常是芯片内部的阻抗与传输线阻抗不匹配导致的反射。这种情况在并行总线和低速电路设计中常常出现,这就需要通过外部端接处理。常用的端接方式主要包括源端端接、终端端接、并联端接、戴维宁端接、RC 端接、差分端接等。

5.端接

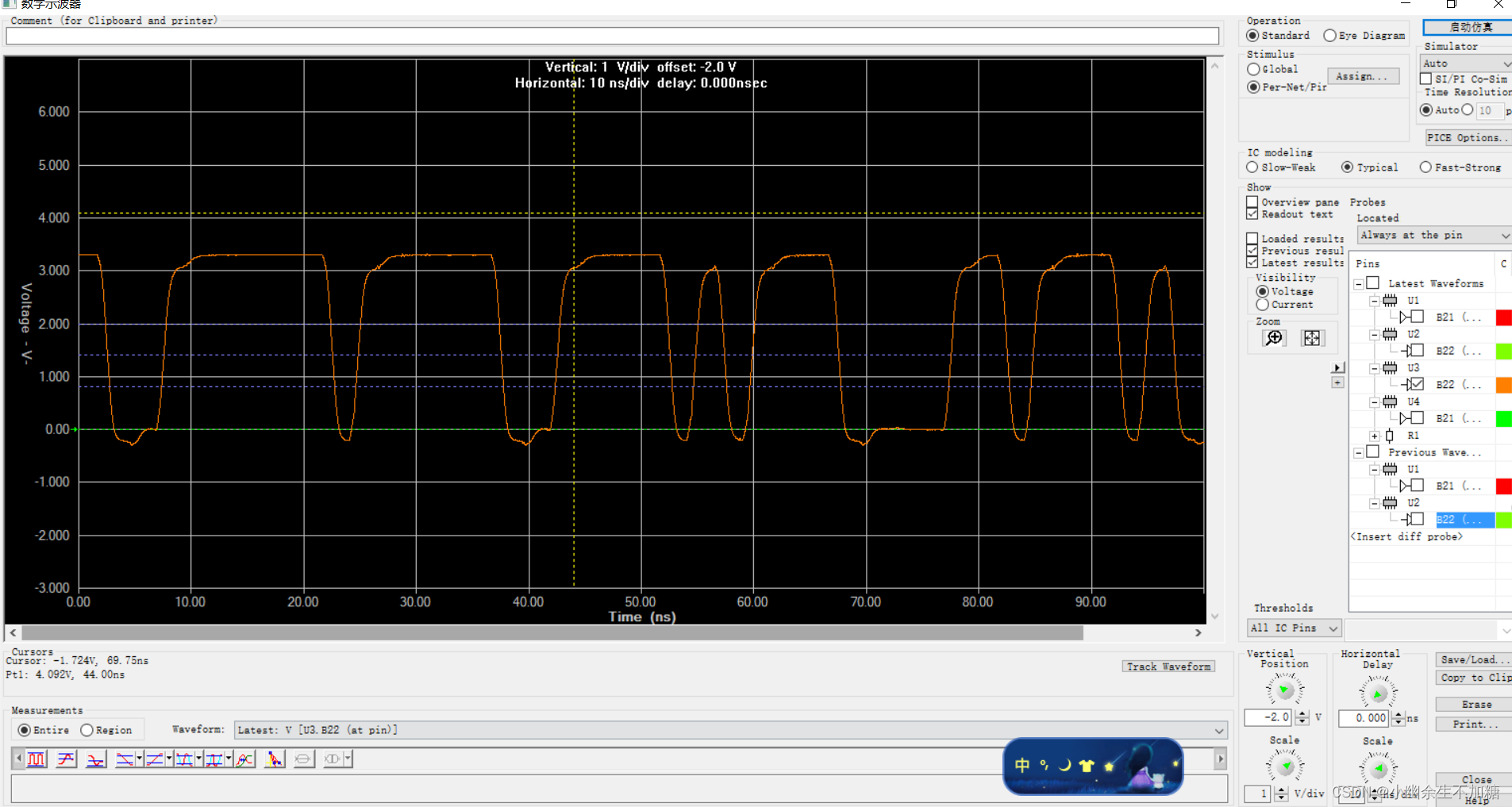

(1)点对点无端接仿真设计

点对点设计对于工程师来讲是最常用的,也是最简单的,但有时由于驱动端的阻抗与传输线的阻抗不匹配会造成信号的失真,即产生信号完完整性问题,如图所示分别是点对点的拓扑结构和仿真波形。(注:以下仿真使用激励源类型为 PRBS 7,速率为400Mb/s。)

点对点无端接拓扑结构

点对点无端接仿真波形

从波形上分析,信号的稳定电压为3.3V,但最最大值达到了 4.09V,有 792.6mV 的过冲。这样的信号在电路中需要尽量避免出现。所以工程师需要想办法把过冲压低,尽量保证电压幅值在电路可接受的范围内,如3.3V±5%。

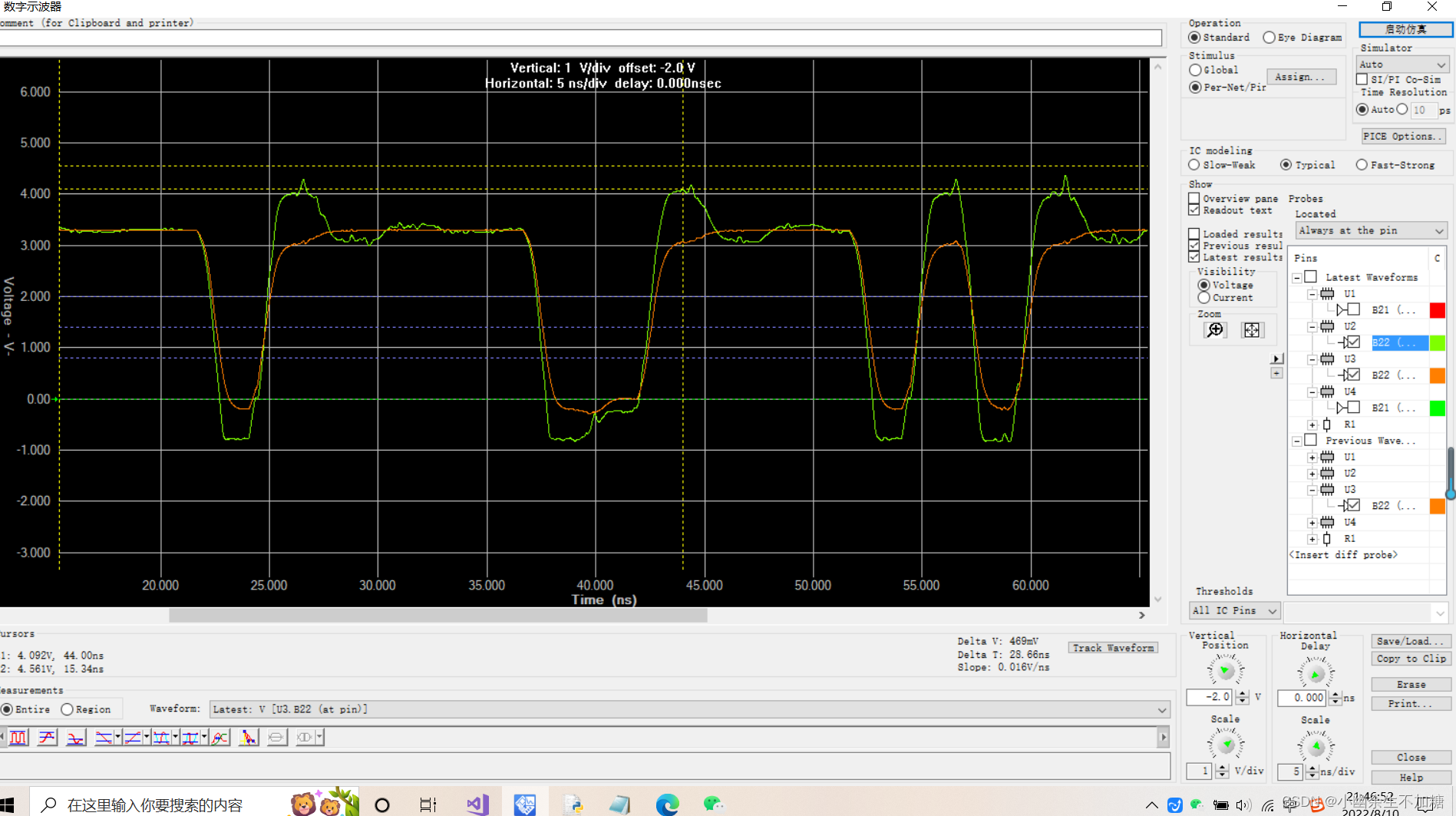

(2)源端端接仿真设计

源端设计是一种常用的端接方式,只在芯片端出来之后加入一个端接电阻,尽量靠近输出端。在此电路结构中,关键的一点是加多大阻值的电阻,这需要根据电路的实际情况进行仿真确认。原则是源端阻抗与所加电阻的值等于传输线的阻抗。在实验中,加入的是33Ω的电阻,仿真拓扑结构如图所示。

从仿真波形结果分析,很显然,端接使信号质量得到了极大的改善,过冲基本为零。只是在加入端接之后,信号的上升沿变缓,上升时间变长。对比如图所示:

源端端接在电路匹配时,可以使电路阻抗匹配得非常好,但并不是适合每一种电路设计,适用或不适用,大致归纳如下。

第一,当驱动端器件的输出阻抗与传输线特性阻抗不匹配时,可以使用源端端接。

第二,当电路不受终端阻抗影响时,可以使用。

第三,当电路信号频率比较高时,或者信号上升时间比较短(特别是高频时钟信号)时,不适合使用源端端接。因为加入端接电阻后,会使电路路的上升时间变长。

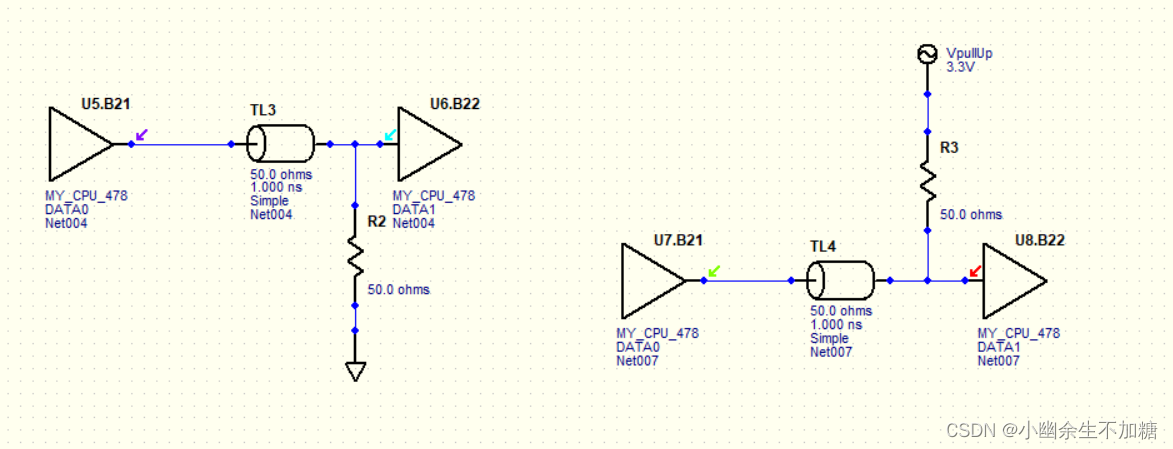

(4)并联端接仿真设计

并联端接一般在信号接收端的位置,使用上拉电阻或下拉电阻进行端接,电路拓扑如图所示:

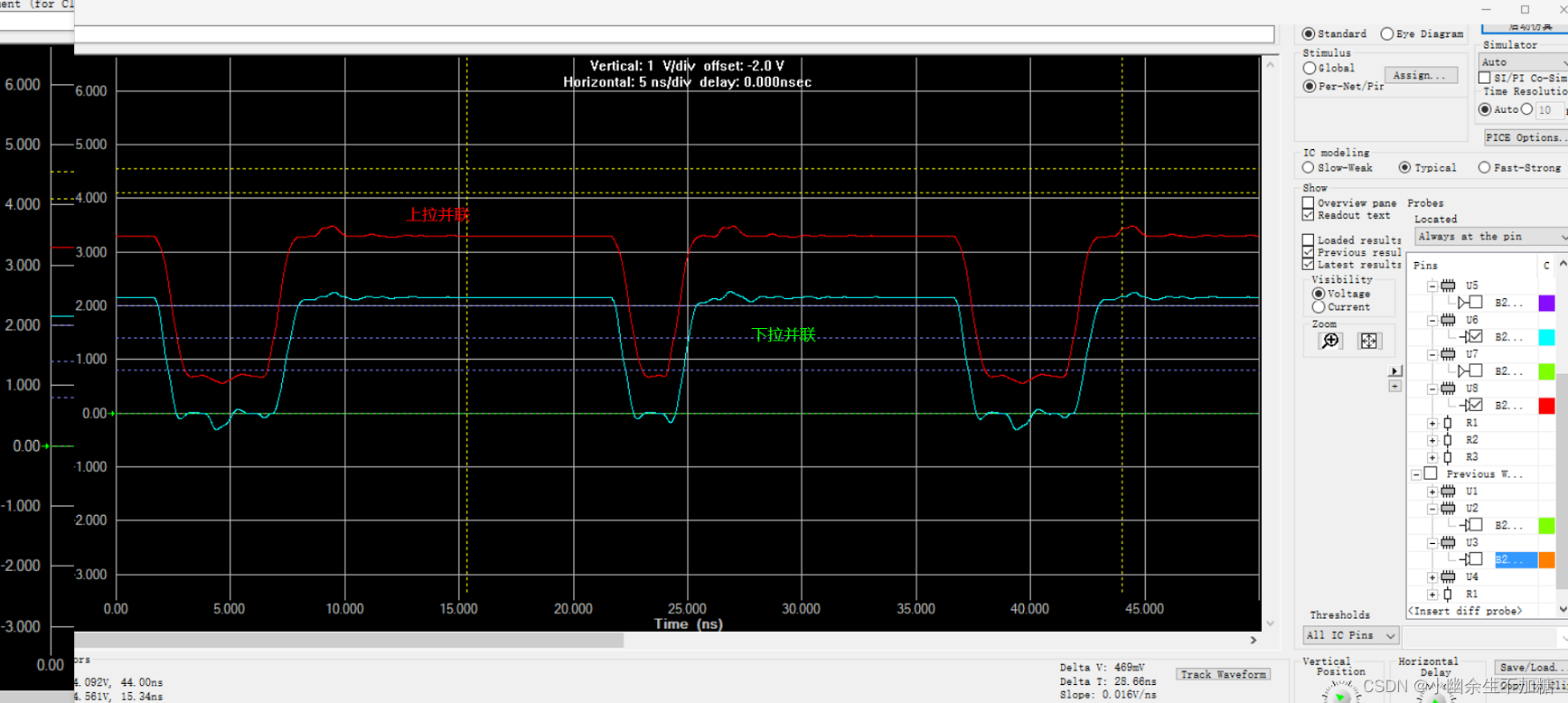

并联端接一般需要消耗电路比较多的电流,很多驱动器无法满足要求,特别是多负载时,驱动端更加难以满足并联端接需要消耗的电流。并联端接仿真的波形如图所示:

从仿真波形分析,上拉并联端接的波形低电平有明显的上移,下拉并联的端接的波形高电平有明显的下移,信号的,信号波形的峰峰值比使用串联端接时小了很多,明显的减少了反射造成的过冲的现象。

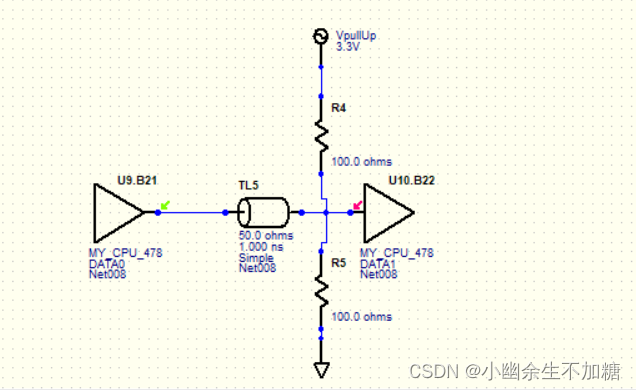

(5)戴维宁端接仿真设计

戴维宁端接就是使用两个电阻组成分压电路,即用上拉电阻R4 和下拉电阻R5构成端接,通过 R4 和 R5 吸收反射能量。这种端接方式,由于一直存在直流功耗,所以对电源的功耗要求比较高,也会降低源端的驱动能力。戴维宁端接拓扑结构如图所示:

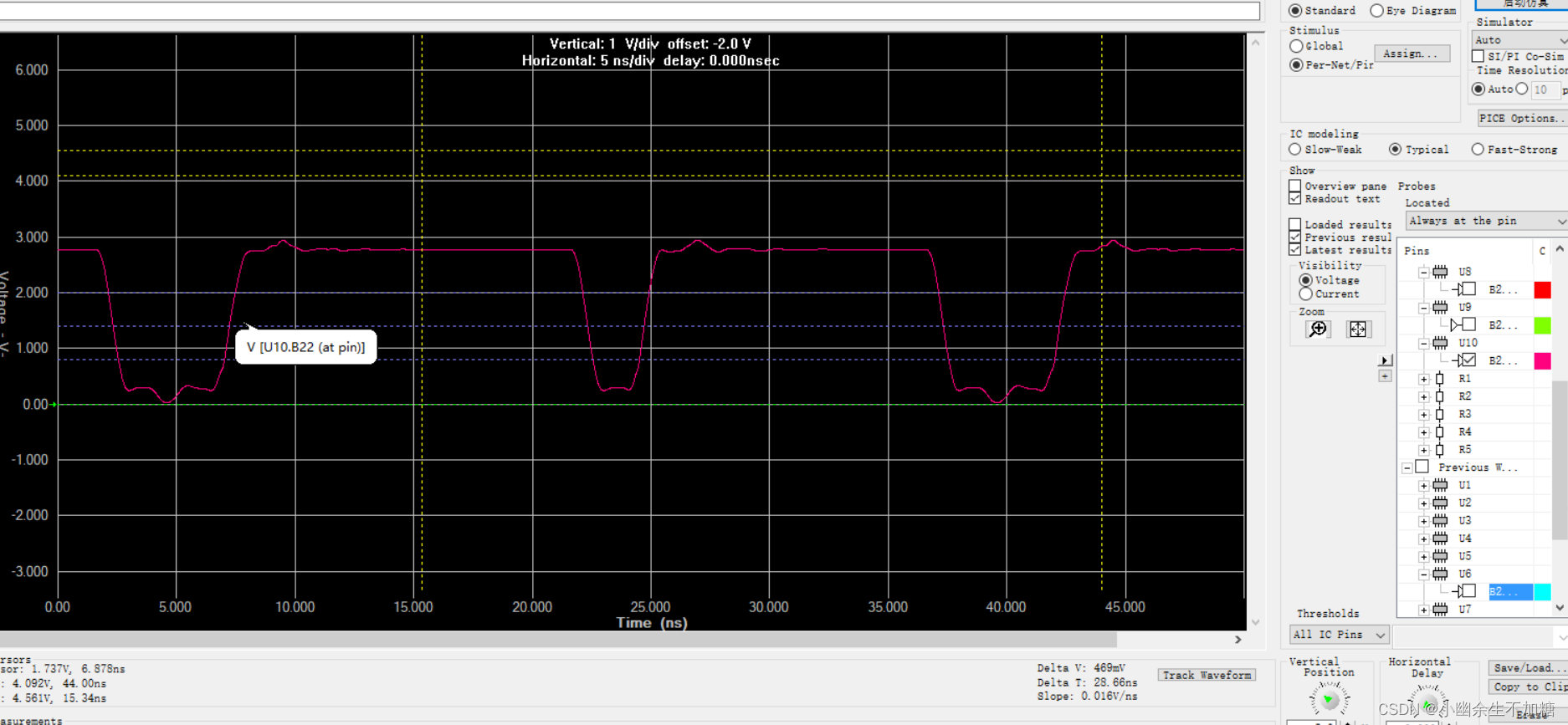

戴维宁端接能比较好地匹配电路,但由于其直流功耗一直存在的特点,以及需要要使用两个分压电阻,使很多电路 设计工程师在使用这类端接时非常谨慎。戴维宁端接仿真波形如图所示:

从仿真波形分析,戴维宁端接匹配效果也非常好,只是驱动能力相对弱一点。

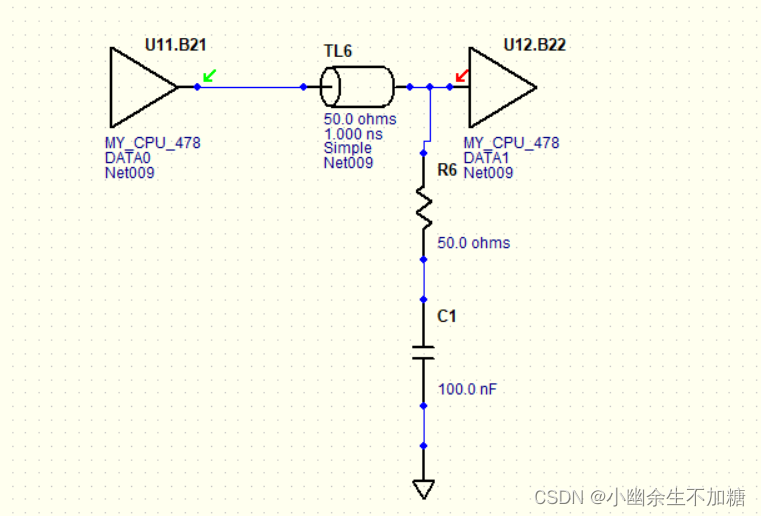

(6)RC端接仿真

RC端接就是在并联下拉端接的电阻下面增加一个电容,并下拉到地,拓扑如图所示:

RC 端接直流消耗较小,但这种电路会引入延时,延时的大小与 RC 值有关。RC 端接仿真波形如图所示。

从仿真波形分析,**高电平没有被降低,低电平提升了很多;**端接后,边沿也稍微变缓慢,变化的程度与RC的值有关,这就可能带来一些潜在的时序影响。一般在选择时也需要非常谨慎。

从上面分析的几种类型来看,基本都能达到电路匹配端接的效果。但是,对于电子产品设计来讲,信号完整性永远都不是独立存在的,其中涉及各个方面,包括电源完整性、电磁兼容性、电路复杂性、可加工性、成本等。那么在解决反射问题时,也要考虑这些方面的原因。在实际项目的应用中,需要工程师根据项目工程的应用综合选择端接的类型。

边栏推荐

- Are there any foreign application cases for domestic databases?

- The crawler is encapsulated into an api

- 7 天找个 Go 工作,Gopher 要学的条件语句,循环语句 ,第3篇

- 安装nodejs

- 字符函数和字符串函数的进阶

- PerfView专题 (第一篇):如何寻找热点函数

- Summary of darknet structures

- 【Mask2Former】 解决代码中一些问题

- 03列中新增子行

- Incredible, thanks to this Android interview question, I have won offers from many Internet companies

猜你喜欢

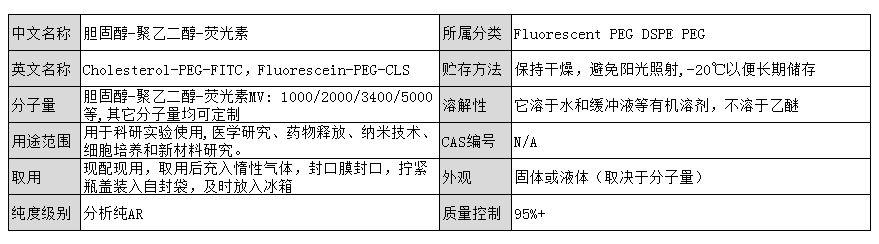

Cholesterol-PEG-FITC,Fluorescein-PEG-CLS,胆固醇-聚乙二醇-荧光素水溶性

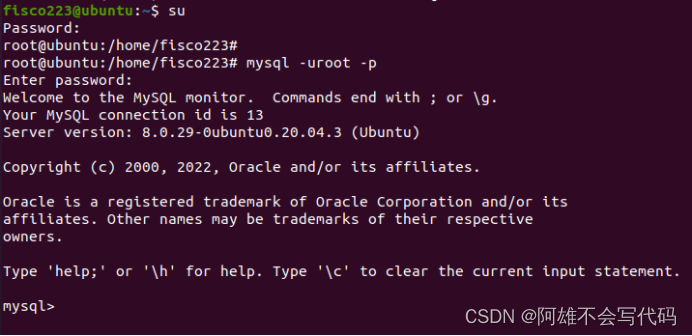

【教程】区块链是数据库?那么区块链的数据存储在哪里?如何查看数据?FISCO-BCOS如何更换区块链的数据存储,由RocksDB更换为MySQL、MariaDB,联盟链区块链数据库,区块链数据库应用

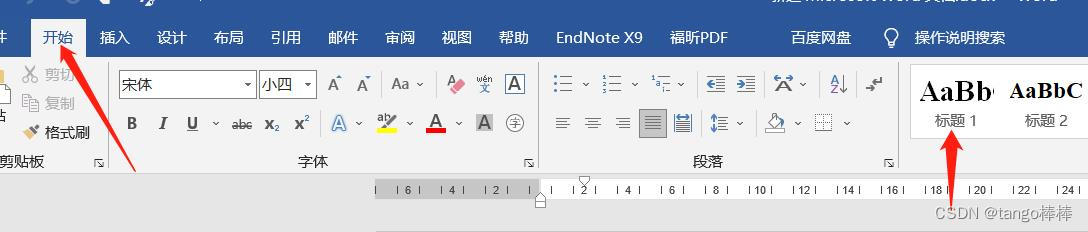

Word小技巧之图表实现自动编号和更新

SDS Observatory

a-upload上传图片

chrome is set to dark mode (including the entire webpage)

SDS观察站

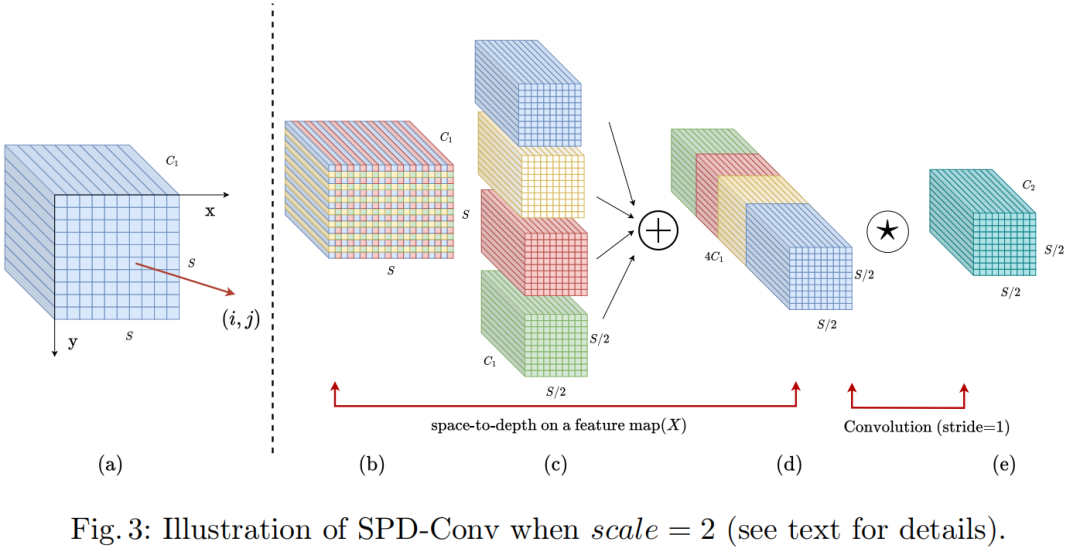

小目标绝技 | 用最简单的方式完成Yolov5的小目标检测升级!

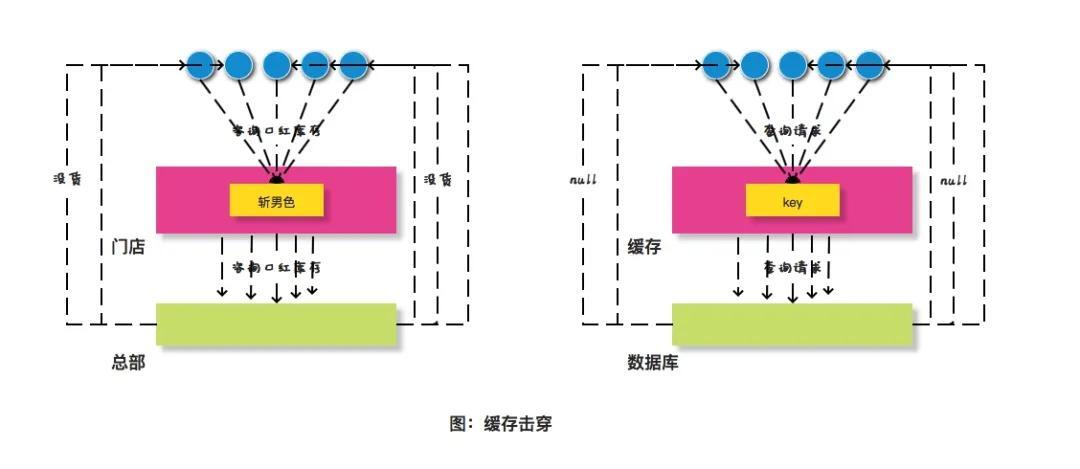

How to explain to my girlfriend what is cache penetration, cache breakdown, cache avalanche?

LeetCode · Question of the Day · 1417. Reformatting String · Simulation

随机推荐

C# Call AutoNavi Map API to obtain latitude, longitude and positioning [Detailed 4D explanation with complete code]

日志使用注意事项和建议

C# 调用高德地图API获取经纬度以及定位【万字详解附完整代码】

Getting Started with Chrome Plug-in Development - Nanny Level Raiders

servlet——servlet执行流程 | servlet关系视图

servlet——servlet介绍 | 发布动态资源

What areas of the deep neural network are related to the human brain neural network?

B端产品需求分析与优先级判断

Jetpack Compose学习(9)——Compose中的列表控件(LazyRow和LazyColumn)

杰理AC632N蓝牙芯片iokey使用解析(通用MCU版)

使用函数计算打包下载OSS文件【遇坑锦集】

[Building a 2D rasterized map using SLAM technology]

The fertile soil cloud innovation plan is coming

【Ackerman Motion Control】

你必须懂的一些MySQL索引技巧

使用.NET简单实现一个Redis的高性能克隆版(七-完结)

如何在游戏中实现一场下雨效果

1.TCP/IP基础知识

【Mysql系列】03_系统设计

Some time function records commonly used in mysql