当前位置:网站首页>FPGA中BEL Site Tile FSR SLR分别指什么?

FPGA中BEL Site Tile FSR SLR分别指什么?

2022-08-10 08:42:00 【yundanfengqing_nuc】

在Xilinx FPGA中,从底层到整个设备可以划分为6个层次:

BEL

Site

Tile

FSR

SLR

Device

下面我们从下到上依次来看一下各个定义。

BEL(Basic Element of Logic)

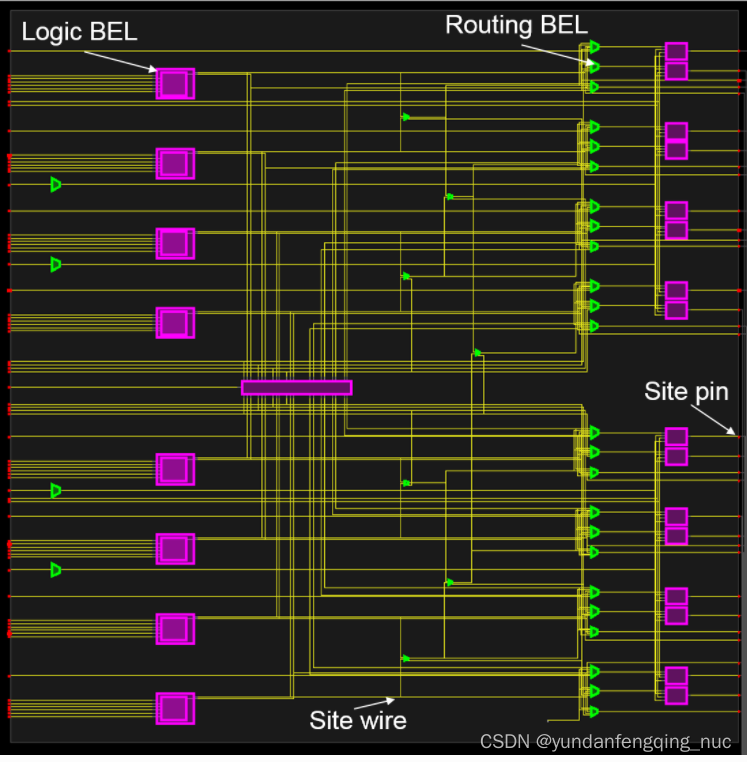

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。像我们常说的LUT、FF、CARRY都属于Logic BEL,Routing BEL我们平时不常说,很多工程师可能也没太听过,像FFMUX和DOUTMUX都属于Routing BEL,它们分别长下面这样:

在Vivado综合或实现的Design中,可以看到会在每一个模块下都会有Nets和Leaf Cells。

image-20211224212553327

Leaf Cells就是FPGA中一个个真实存在的硬件模块,Vivado中place_design做的工作就是把这些Leaf Cells放到合适的BEL上。

image-20211224212627988

Site

一系列相关的元素与它们的连线组成了Site,Site中主要包含下面三种:

BEL

Site的输入输出管脚

Site内部的连线

Site一般都是跟Slice、DSP48、BRAM等是对应的,我们以Slice为例,在7系列的FPGA中,一个CLB有两个Slice,下图的白色框是一个CLB,从左边的Properties中可以看出,包含了两个site,其实就是包含了两个Slice。每个Slice都有独立的site,所以这个CLB中就有两个sites。

Xilinx FPGA中很多元素的位置都是以_X_Y结尾来表示该元素在坐标中的位置,下图中的这个Slice的位置是X142Y185。

Tile

Tile是比Site更高一级的概念,一个Tile里面包含多个Site,Tile没有pin的概念,比如下面这个Tile,其实就是一个CLB。

FSR

FSR就是Fabric Sub Region or Clock Region,是由一片Tile组成的,在UltraScale的FPGA中,所有的FSR的高度都有60个CLB,但宽度不尽相同。

时钟routing和distribution的粒度与FSR相同,在UltraScale的FPGA中,有24个水平的routing track,24个垂直的routing track,24个水平的distribution track和24个垂直的distribution track,相邻的FSR就靠这些track互连。

SLR

SLR就是Super Logic Region,这个概念仅针对SSIT的FPGA,也就是包含多个die的芯片,这样每个die就被称为一个SLR。

Device

这个概念就无需过多介绍,就是指整个FPGA;如果是单个die的片子,那么多个FSR就组成了Device,如果是多个die的片子,那么多个SLR组成了Device。

边栏推荐

- StringUtils的具体操作

- Relaxation class: the boss will martial arts, who also can not hold up against!The charm of six sigma training

- Pieces of TensorFlow 2.9 (1)

- Different command line styles

- Uni applet Tencent map polygon background transparency

- Synchronization lock synchronized traces the source

- 【Unity入门计划】2D游戏实现敌人来回移动控制脚本

- 协同工具满足70%-90%的工作需求,成为企业香饽饽

- DAY25: Logic Vulnerability

- Rust learning: 6.4_ enumeration of composite types

猜你喜欢

推荐几个高质量的软件测试实战项目

DAY25: Logic Vulnerability

本地生活商家如何通过短视频赛道,提升销量曝光量?

DAY25:逻辑漏洞复现

2022-08-01 Advanced Network Engineering (23) Advanced VLAN Technology - VLAN Aggregation, MUX VLAN

How AliExpress sellers seize product search weight

90. (cesium house) cesium height monitoring events

【Unity入门计划】制作RubyAdventure03-使用碰撞体&触发器实现世界交互

iwemeta元宇宙:一个娃娃卖9999元,泡泡玛特认为一点也不贵

ShardingSphere入门

随机推荐

Class Notes (7) (1) - #647. Find the root and the child (root)

VMware ESX Server常用命令行

phpstudy开机自启

Johnson全源最短路

J9数字论:Web3.0+互联网电商会引起怎样的火花?

day16--抓包工具Charles的使用

【Unity入门计划】Collision2D类&Collider2D类

不同的命令行风格

Spotify使用C4模型表达其架构设计

1-31部 1-31套 和硬件工程师90天学习资料及笔记汇总

js读取excel时间格式转换

数据库注入提权总结(一)

nrm 使用详解

UGUI - Events, iTween Plugin

ARM Architecture 2: Processor Core and Assembly Instruction Set

高等数学(第七版)同济大学 习题4-3 个人解答

js函数聚合的三种实现方式

刷题工具h

CV+Deep Learning - network architecture Pytorch recurrence series - classification (3: MobileNet, ShuffleNet)

Unity—UGUI控件