当前位置:网站首页>VHDL finite state machine (FSM) code example

VHDL finite state machine (FSM) code example

2022-04-23 06:46:00 【Round moon】

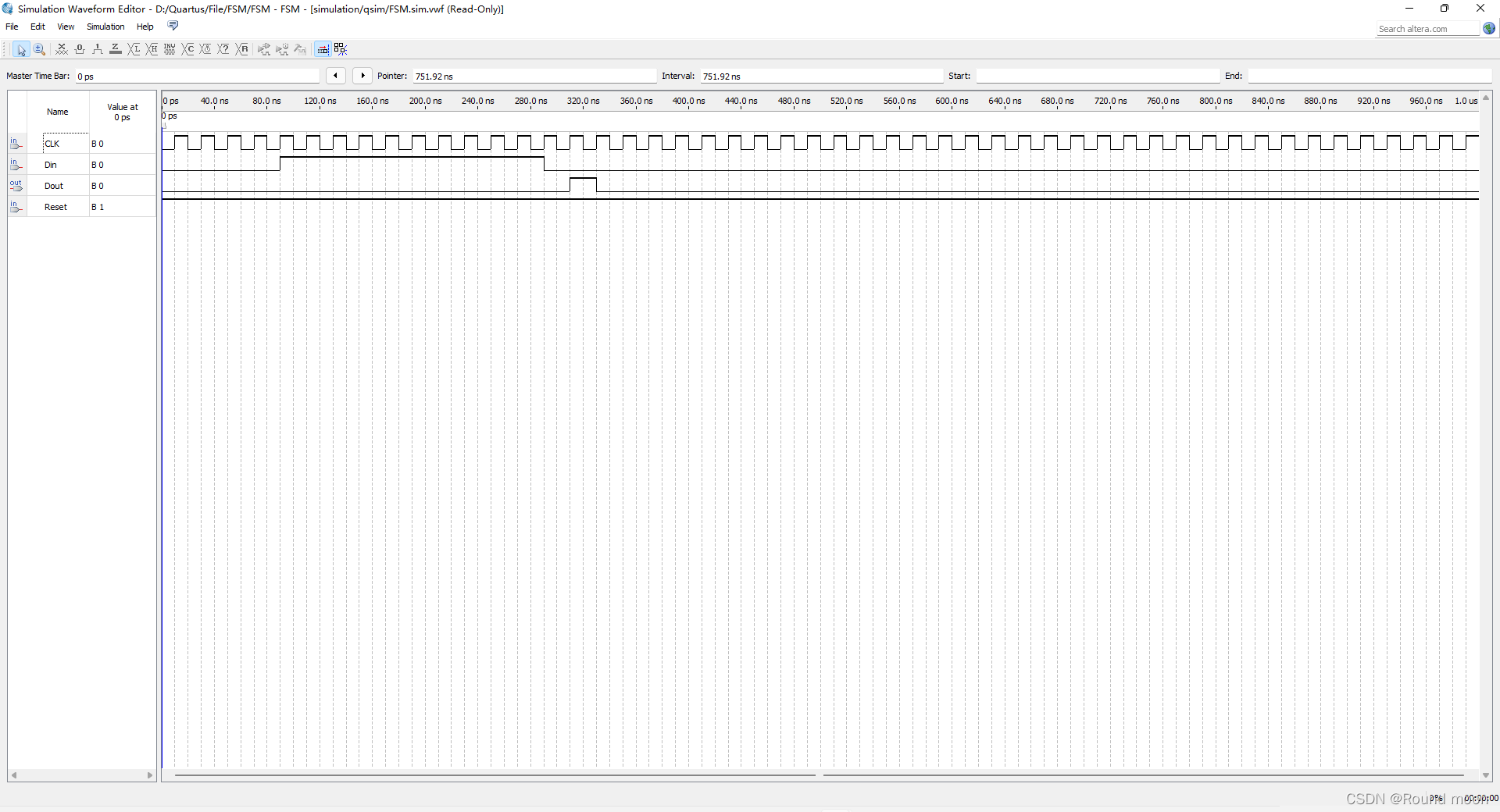

Example 1 "10" detector

library ieee;

use ieee.std_logic_1164.all;

entity FSM is

port(Din,CLK,Reset:in std_logic;Dout:out std_logic);

end FSM;

architecture behave of FSM is

type state is(S0,S1,S2);

signal currentstate: state:=S0;

signal nextstate:state:=S0;

begin

state_trans:process(Din,currentstate)

begin

case currentstate is

when S0=>if Din='1' then nextstate<=S1;else nextstate<=S0;end if;

when S1=>if Din='0' then nextstate<=S2;else nextstate<=S1;end if;

when S2=>if Din='0' then nextstate<=S0;else nextstate<=S1;end if;

end case;

end process;

state_latch:process(CLK,reset)

begin

if reset='0' then

currentstate<=S0;

else

if CLK'event and CLk='1' then

currentstate<=nextstate;

end if;

end if;

end process;

Dout<='1' when currentstate=S2 else '0';

end behave;

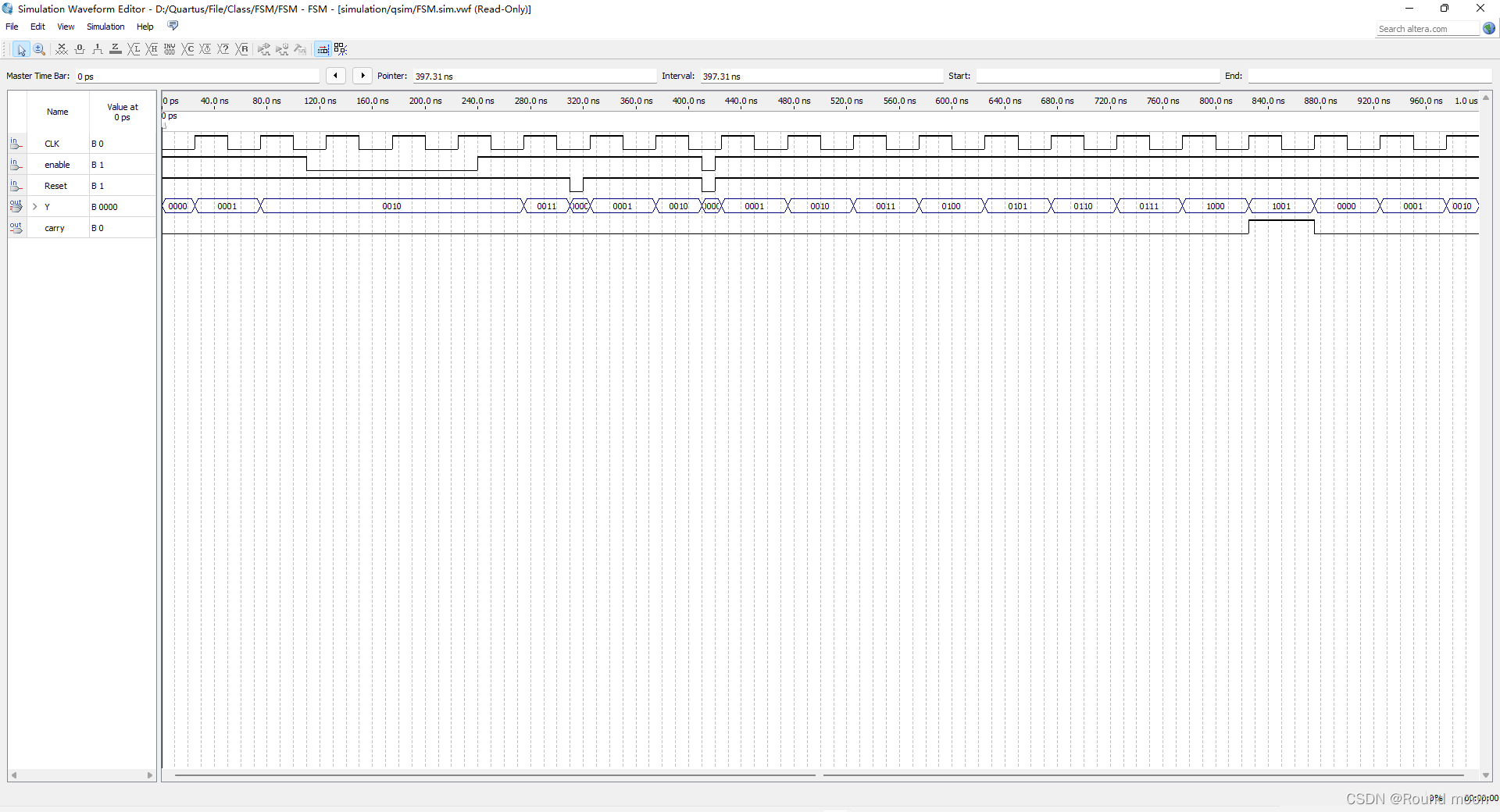

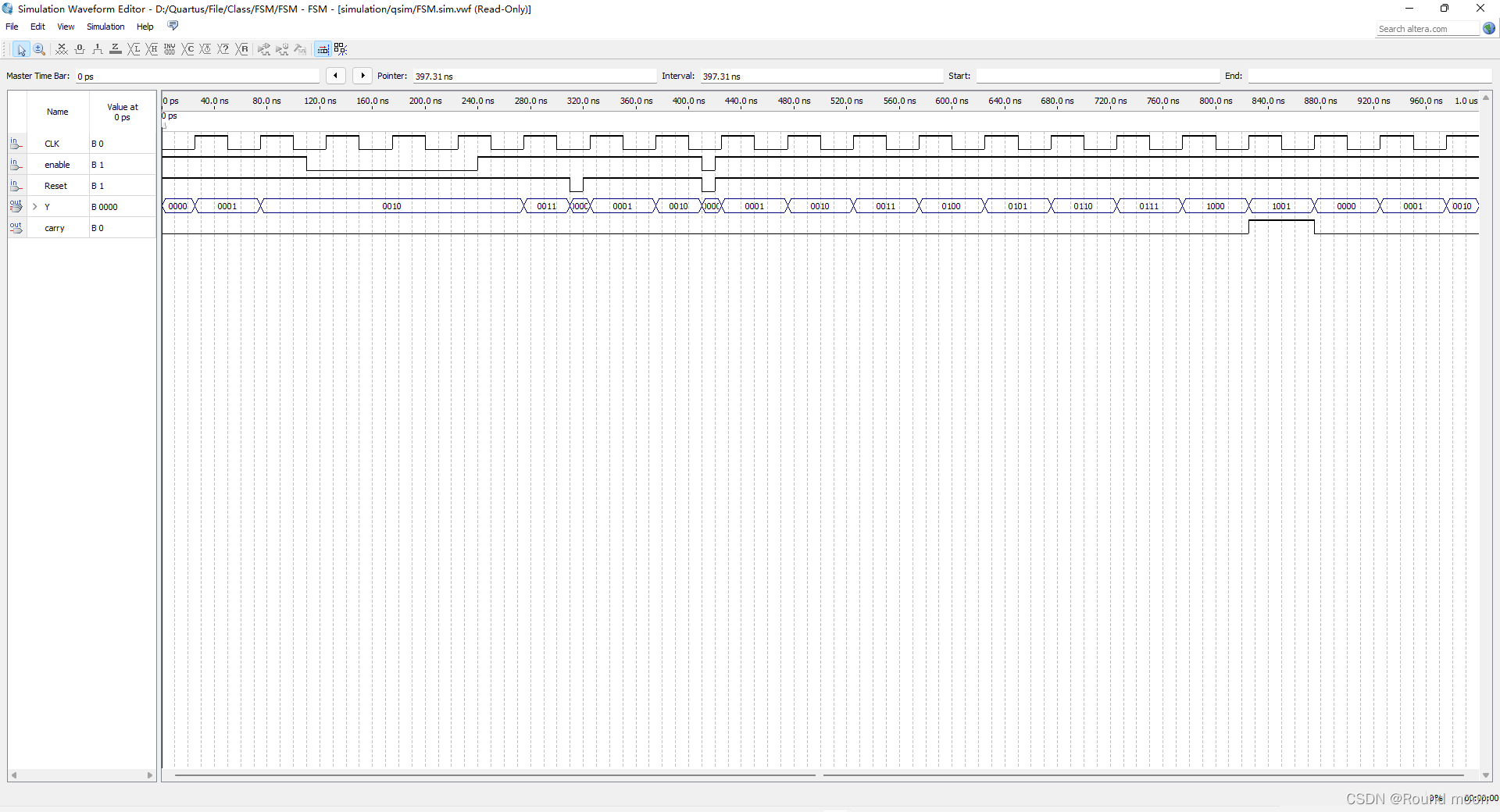

Example 2 Decimal counter

library ieee;

use ieee.std_logic_1164.all;

entity FSM is

port(CLK,Reset,enable:in std_logic;Y:out std_logic_vector(3 downto 0);carry:out std_logic);

end FSM;

architecture behave of FSM is

type state is(S0,S1,S2,S3,S4,S5,S6,S7,S8,S9);

signal currentstate:state:=S0;

signal nextstate:state:=S0;

begin

process(currentstate)

begin

case currentstate is

when S0=>if enable='1' then nextstate<=S1;else nextstate<=S0;end if;

when S1=>if enable='1' then nextstate<=S2;else nextstate<=S1;end if;

when S2=>if enable='1' then nextstate<=S3;else nextstate<=S2;end if;

when S3=>if enable='1' then nextstate<=S4;else nextstate<=S3;end if;

when S4=>if enable='1' then nextstate<=S5;else nextstate<=S4;end if;

when S5=>if enable='1' then nextstate<=S6;else nextstate<=S5;end if;

when S6=>if enable='1' then nextstate<=S7;else nextstate<=S6;end if;

when S7=>if enable='1' then nextstate<=S8;else nextstate<=S7;end if;

when S8=>if enable='1' then nextstate<=S9;else nextstate<=S8;end if;

when S9=>if enable='1' then nextstate<=S0;else nextstate<=S9;end if;

end case;

end process;

process(clk,reset)

begin

if reset='0' then

currentstate<=S0;

elsif CLK'event and CLK='1' then

if enable='1' then

Currentstate<=nextstate;

end if;

end if;

end process;

with currentstate select

Y<="0000" when S0,

"0001" when S1,

"0010" when S2,

"0011" when S3,

"0100" when S4,

"0101" when S5,

"0110" when S6,

"0111" when S7,

"1000" when S8,

"1001" when S9;

carry<='1' when currentstate=S9 else '0';

end behave;

By-Round Moon

版权声明

本文为[Round moon]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204230549498953.html

边栏推荐

- C语言中volatile的使用

- 圆整 round 的一点点小细节

- Matching between class template with default template argument and template parameter

- Opencv uses genericindex for KNN search

- HDU-Memory Control

- [UDS unified diagnosis service] i. diagnosis overview (3) - ISO 15765 architecture

- 2022LDU寒假训练-程序补丁

- 如何读文献

- TP download folder, compress folder and download

- [stepping on the pit] MELD in win11 wsl2 cannot be used normally. Problem repair

猜你喜欢

CUDA project encountered a series of compilation problems after changing the environment (computer)

Installation of GCC, G + +, GDB

![[UDS unified diagnostic service] i. overview of diagnosis (4) - basic concepts and terms](/img/fb/3d3cf54dc5b67ce42d60e0fe63baa6.png)

[UDS unified diagnostic service] i. overview of diagnosis (4) - basic concepts and terms

卷积神经网络实现CIFAR100数据集分类

VHDL 有限状态机(FSM) 代码示例

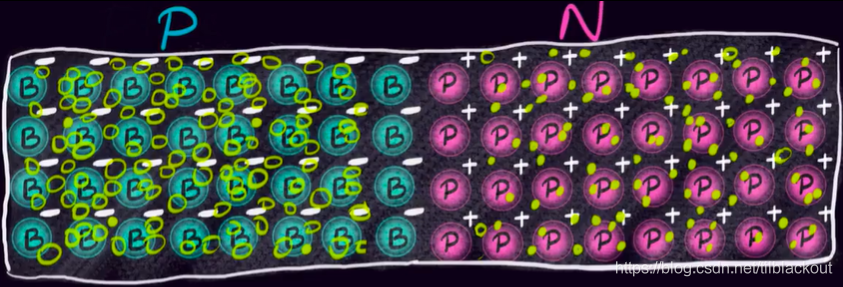

PN结、二极管原理详解与应用

【UDS统一诊断服务】(补充)五、ECU bootloader开发要点详解 (2)

基于SSD的物体检测案例实现

MOS管特性和导通过程

【UDS统一诊断服务】四、诊断典型服务(1)— 诊断和通信管理功能单元

随机推荐

对象的动态建立和释放,赋值和复制

FOC电机库 定点PID代码分析

在MFC中使用printf

【UDS统一诊断服务】一、诊断概述(2)— 主要诊断协议(K线和CAN)

修改注册表的值

【UDS统一诊断服务】二、网络层协议(1)— 网络层概述与功能

CUDA environment installation

QT icon application

提交本地仓库并同步码云仓库

[UDS unified diagnosis service] i. diagnosis overview (2) - main diagnosis protocols (K-line and can)

Understanding of SSH public key and private key

Static member

【UDS统一诊断服务】五、诊断应用示例:Flash Bootloader

声明为全局变量

VHDL 有限状态机(FSM) 代码示例

[UDS unified diagnostic service] II. Network layer protocol (2) - data transmission rules (single frame and multi frame)

POJ-The Unique MST

往String原型上封装一个时间戳转日期的方法

SSH 公钥 私钥的理解

基于VGG卷积神经网络的图像识别代码实现