当前位置:网站首页>文献阅读(185)Co-design

文献阅读(185)Co-design

2022-08-11 11:08:00 【tiaozhanzhe1900】

文章目录

- 题目:Coupling Extraction and Optimization for Heterogeneous 2.5D Chiplet-Package Co-Design

- 时间:2020

- 会议:ICCAD

- 研究机构:阿肯色大学

缩写

- RDL: package redistribution layers 再分布层

- WLP: Wafer-Level-Packaging

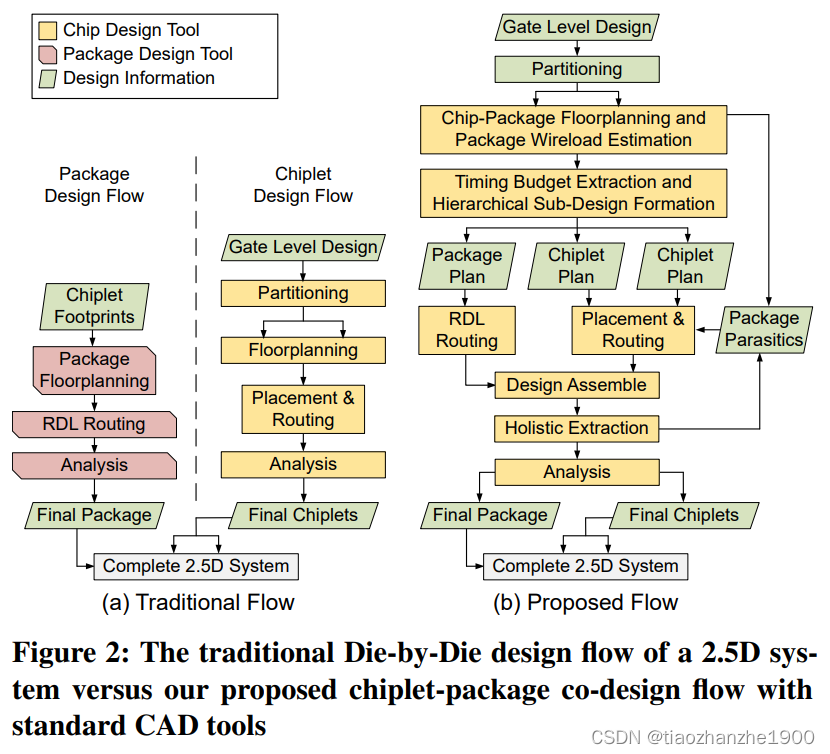

传统的设计流程是将芯片设计与封装设计分开进行,没有考虑他们的相互作用,因为间隙足够大,PCB pitch(间距)为250um,但后面发展的wafer级封装技术间隙为30-50um,然后现在InFO就到了10-1.5um;因此,为了保证系统可靠性和信号完整性,需要在时序和功耗上考虑芯片和封装上的相互作用

本篇论文的主要贡献:

- A unified tool flow that, for the first time, designs and optimizes chiplets and the package of high-density 2.5D systems together taking into account the mutual interactions between them;

- A new holistic parasitic extraction and STA analysis flow for homogeneous 2.5D systems with chiplets and the package considered together;

- A new in-context parasitic extraction and STA analysis flow for heterogeneous 2.5D systems with chiplets-package interactions captured;

- A comparative study between two 2.5D designs to validate our Drop-in design approach and demonstrate chiplet-package interaction impacts on two 2.5D systems Performance, Power, and Area (PPA)

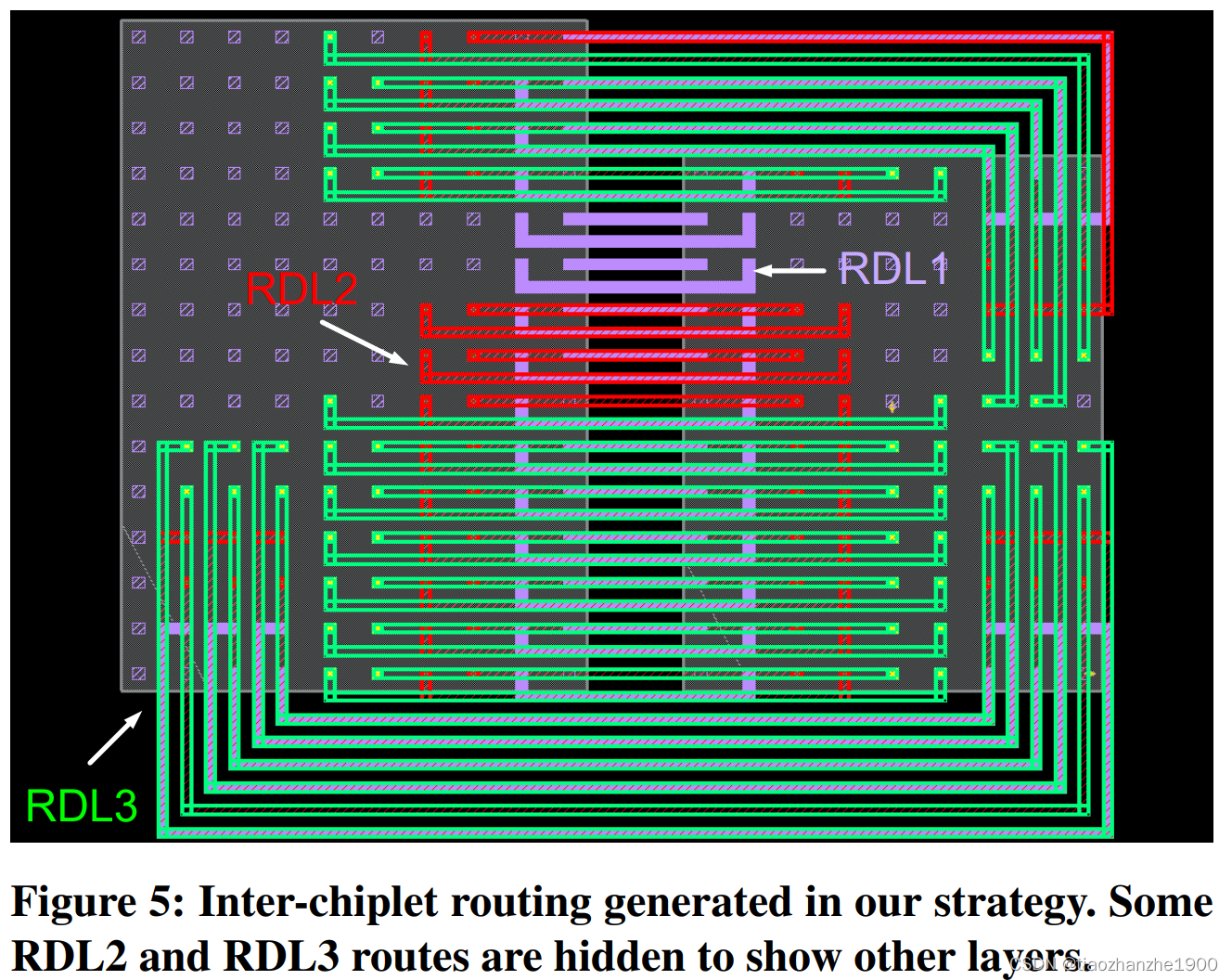

Package Floorplanning and RDL Routing

chiplet间的RDL线完全有可能成为时序的瓶颈,当然,相比与芯片内部,RDL密度要小得多,所以不太可能出现不能布线即routability的问题,关键还是时序能不能满足要求,需要package wireload estimations

- 题目:Thermal Modeling of a Chiplet-Based Packaging With a 2.5-D Through-Silicon Via Interposer

- 时间:2022

- 期刊:TCAD

- 研究机构:TPMT( IEEE Transactions on Components, Packaging and Manufacturing Technology)

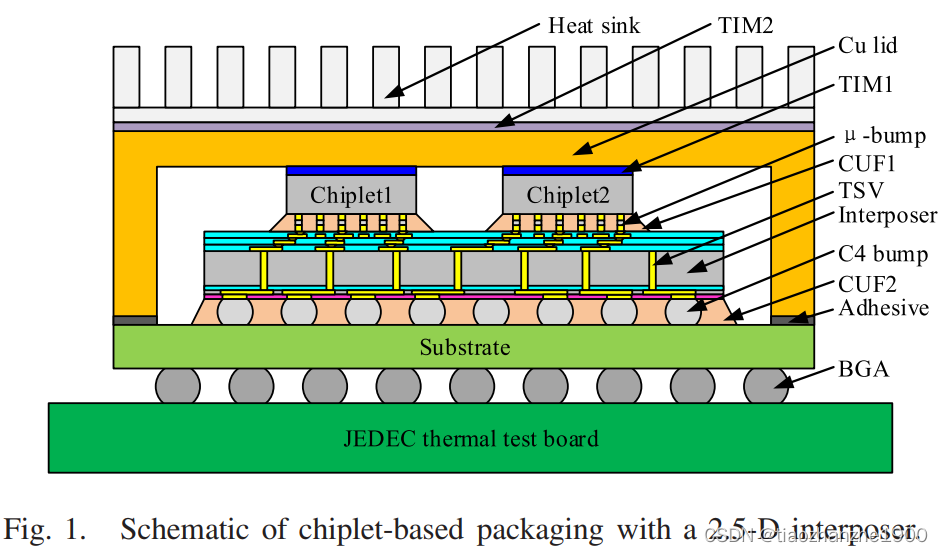

2.5D封装

The 2.5-D packaging uses an interposer with TSVs and redistribution layers (RDLs).

Multiple chips are stacked on the interposer side-by-side via microbumps (μ-bumps) to connect to each other or the substrate.

由上图所示

Two chiplets are mounted on the interposer side-by-side through μ-bumps. The interposer is bonded on an organic substrate via the controlled collapse chip connection (C4) bumps.

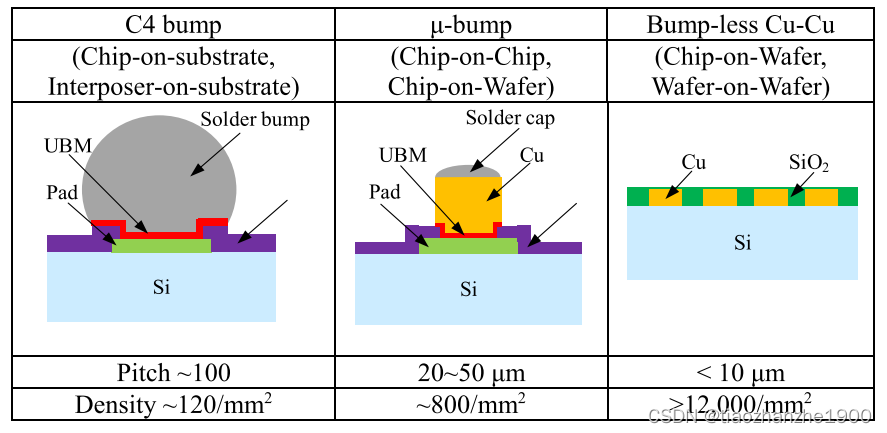

In general, the packaging interconnections can be classified into horizontal and vertical ones. The horizontal interconnection mainly includes fine line/space layers, 2.5-D interposer, and silicon bridge, while the vertical interconnection mainly includes C4 bump, μ-bump, and bumpless.

上述垂直互连的接触形式如下图所示

边栏推荐

猜你喜欢

数据库导出的csv文件纯数字被转为科学计数法

运动健康服务场景事件订阅,让应用推送“更懂用户”

【翻译】Drafting and Revision: Laplacian Pyramid Network for Fast High-Quality Artistic Style Transfer

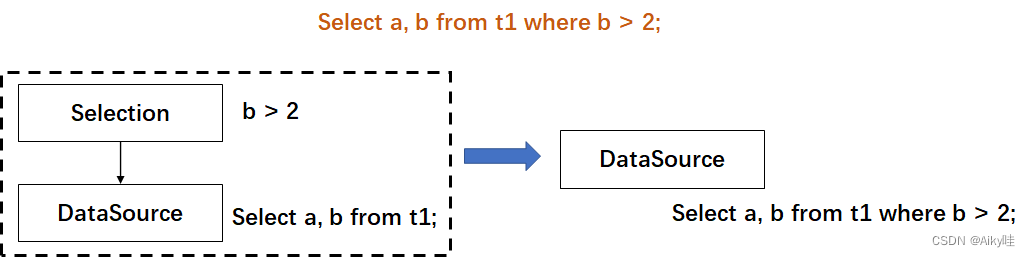

数据库内核面试中我不会的问题(4)

当科学家决定搞点“花里胡哨”的东西

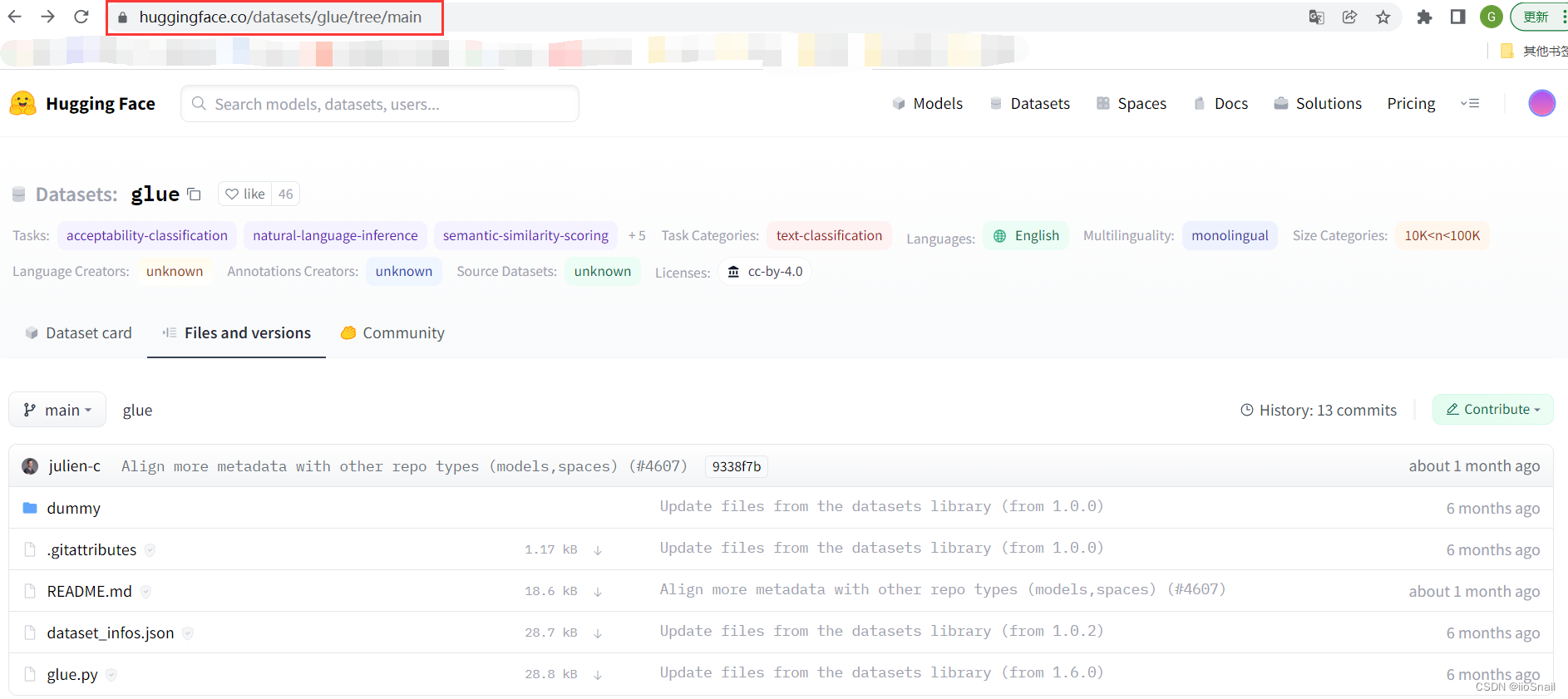

如何批量下载hugging face模型和数据集文件

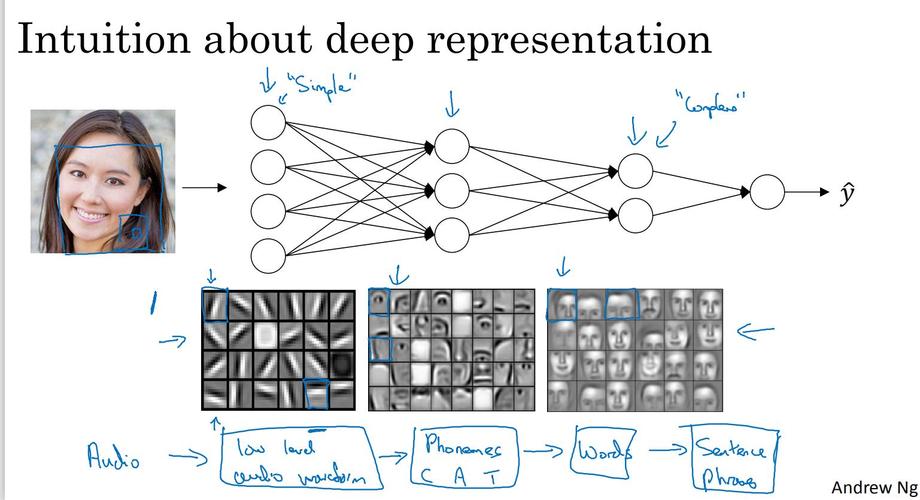

How long does it take to train a neural network, neural network training takes too long

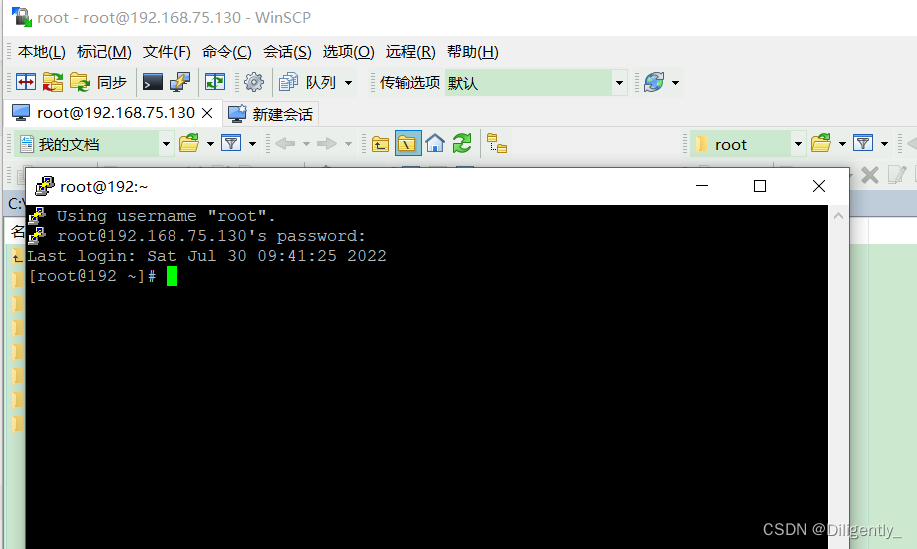

虚拟机使用 WinSCP & Putty

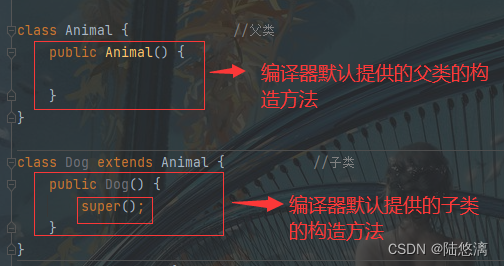

4. 继承

C语言手写魂斗罗(一)

随机推荐

7 天找个 Go 工作,Gopher 要学的条件语句,循环语句 ,第3篇

阿里云ssl证书申请,宝塔ssl证书部署

6.1 总线的概念和结构形态

LeetCode·每日一题·1417.重新格式化字符串·模拟

go语言学习:并发编程(定时器/select/并发安全锁)

fetch请求设置请求头错误导致无法跨域

PerfView project (first) : how to find hot spots function

03列中新增子行

困扰所有SAP顾问多年的问题终于解决了

centos linux 下安装mysql 8.0

六、一起学习Lua 循环

开发者时薪高达1200美元?一文带你走近Move语言的编程魅力!

数据库导出的csv文件纯数字被转为科学计数法

论文笔记:《Time Series Generative Adversrial Networks》(TimeGAN,时间序列GAN)

AcWing 273. 分级(线性DP+结论)

How to explain to my girlfriend what is cache penetration, cache breakdown, cache avalanche?

ID3v2 Library以便能够设置

我用这个操作,代码可读性提升一个档次

Spark Core

PerfView专题 (第一篇):如何寻找热点函数