当前位置:网站首页>Comprehensive analysis of FPGA basics

Comprehensive analysis of FPGA basics

2022-08-10 00:32:00 【InfoQ】

1、FPGA的简介

- FPGA(Field- Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLDIt is a product further developed on the basis of programmable devices.它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点.

- FPGA普遍用于实现数字电路模块,用户可对FPGA内部的逻辑模块和I/O模块重新配置,以实现用户的需求.它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改.FPGA如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统.

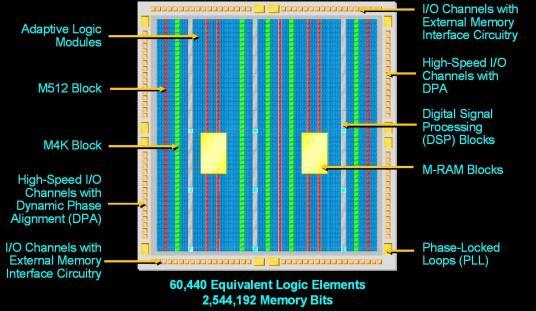

- FPGA 的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块RAM,布线资源,内嵌专用硬核,底层内嵌功能单元.FPGA的设计流程包括算法设计、代码仿真以及设计、板级调试,设计者以及实际需求建立算法架构,利用EDA建立设计方案或HD编写设计代码,通过代码仿真保证设计方案符合实际要求,最后进行板级调试,利用配置电路将相关文件下载至FPGA芯片中,验证实际运行效果.

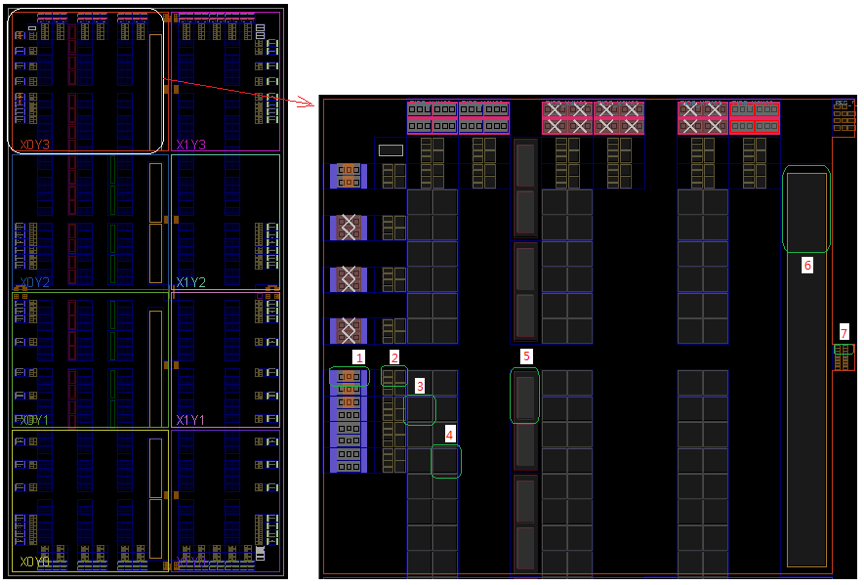

2、FPGA整体结构

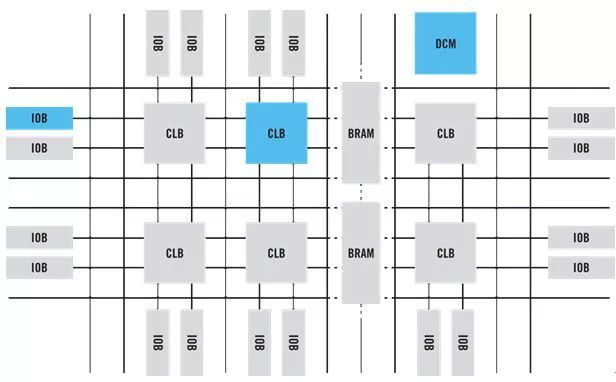

FPGAThe architecture mainly consists of configurable logic blocksCLB(Configurable Logic Block)、输入输出块IOB(Input Output Block)、内部连线(Interconnect)and other inline units in four parts.

- CLB是FPGA的基本逻辑单元.实际数量和特性会依器件的不同而改变,但是每个CLB都包含一个由4或6个输入、若干选择电路(多路复用器等)和触发器组成的可配置开关矩阵.

- FPGAMany types are supportedI/O标准,因而可以为系统设计提供理想的接口桥接.FPGA 内的I/O按bank分组,每个bank能独立支持不同的I/O标准.目前最先进的FPGA提供了十多个I/O bank,能够提供灵活的I/O支持.

- CLB 提供了逻辑性能,灵活的互连布线则负责在CLB和I/O之间传递信号.布线有几种类型,从设计用于专门实现 CLB 互连(短线资源)、到器件内的高速水平和垂直长线(长线资源)、再到时钟与其它全局信号的全局低skew布线(全局性专用布线资源).

- Embedded hard core unit includedRAM、DSP、DCM(数字时钟管理模块)及其它特定接口硬核等,FPGAThe internal structure of the device is shown in the following diagram.

3、FPGA开发流程

FPGA的设计流程就是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程.FPGA的开发流程一般如下图所示,包括功能定义/器件选型、设计输入、功能仿真、逻辑综合、布局布线与实现、The main steps such as programming and debugging.

- 功能定义/器件选型:在FPGA设计项目开始之前,必须有系统功能的定义和模块的划分,另外就是要根据任务要求,如系统的功能和复杂度,对工作速度和器件本身的资源、成本、以及连线的可布性等方面进行权衡,选择合适的设计方案和合适的器件类型.

- 设计输入:Design input refers to the use of hardware description language to express the designed system or circuit in code.最常用的硬件描述语言是Verilog HDL.

- 功能仿真:Functional simulation refers to the logic function verification of the circuit designed by the user before logic synthesis.仿真前,需要搭建好测试平台并准备好测试激励,仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化.如果发现错误,则返回设计修改逻辑设计.常用仿真工具有Model Tech公司的ModelSim、Sysnopsys公司的VCS等软件.

- 逻辑综合:所谓综合就是将较高级抽象层次的描述转化成较低层次的描述.综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现.就目前的层次来看,综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路.

- 布局布线与实现:Place and route can be understood as the use of implementation tools to map logic into the resources of the target device structure,决定逻辑的最佳布局,选择逻辑与输入输出功能链接的布线通道进行连线,并产生相应文件(如配置文件与相关报告);实现是将综合生成的逻辑网表配置到具体的FPGA芯片上.由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具.

- 编程调试:设计的最后一步就是编程调试.芯片编程是指产生使用的数据文件(位数据流文件,Bitstream Generaon),将编程数据加载到FPGA芯片中;之后便可进行上板测试.最后将FPGA文件(如.bit文件)从电脑下载到单板上的FPGA芯片中.

- 目前FPGAThe two major manufacturers are xilinx和altera.

- Xilinx:The company website is :http://www.xilinx.com/.FPGA市场的龙头老大,市场份额接近50%,其主要产品包括:Sparten系列、Virtex系列、Artix系列、Kintex系列、Virtex系列等

开发工具:The development tools for its sixth-generation and earlier products are ISE ,Starting with the seventh generation of products,All transferred tovivado平台.

- Altera:The company website is :http://www.altera.com/,FPGAThe second master of the market,市场份额40%以上,2015年6月被Intel以167亿美元收购.主要产品包含:Max系列、Cyclone系列、Arria系列、Stratix系列等.

主要开发工具:Quartus

4、FPGA内部结构

XC6SLX4-2TQG144芯片

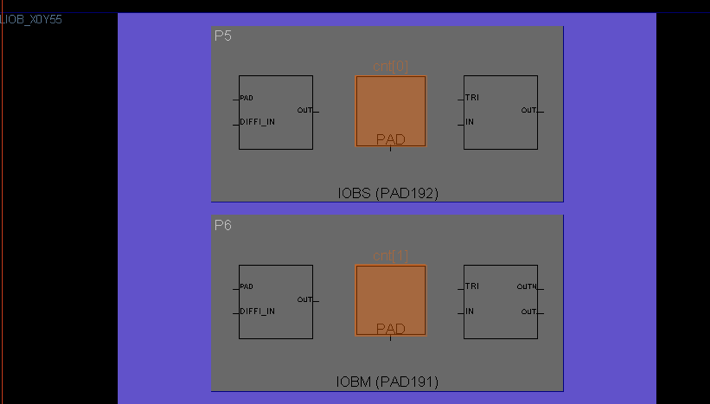

输入输出块

ILOGIC、OLOGIC、IODELAY部分

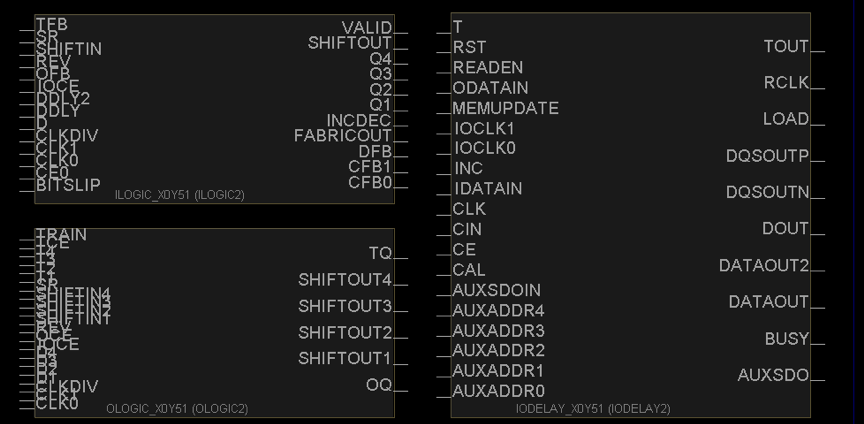

Slice

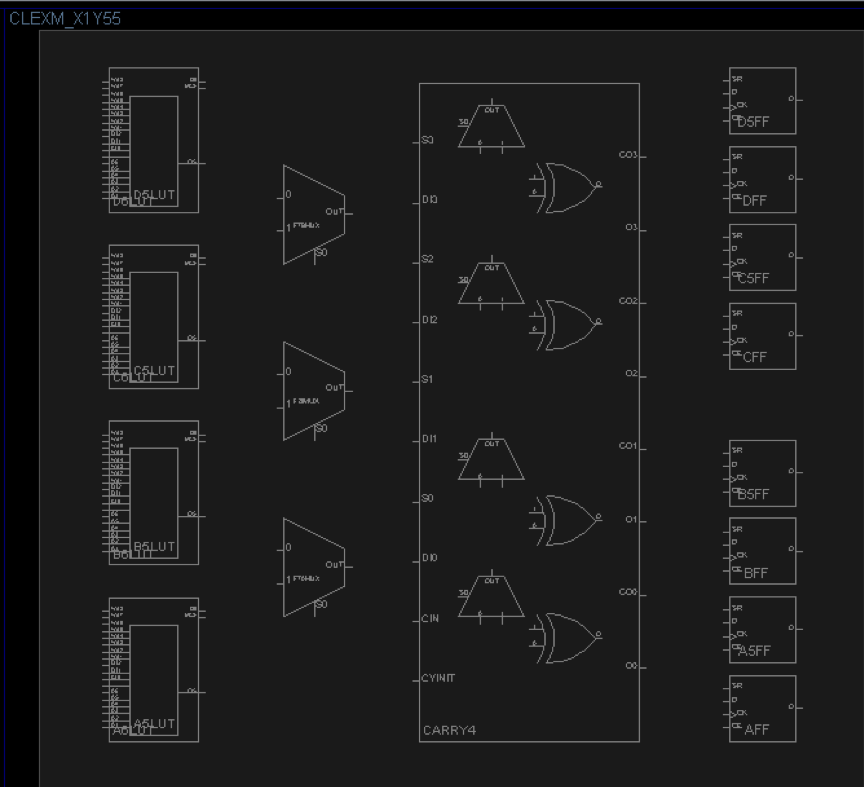

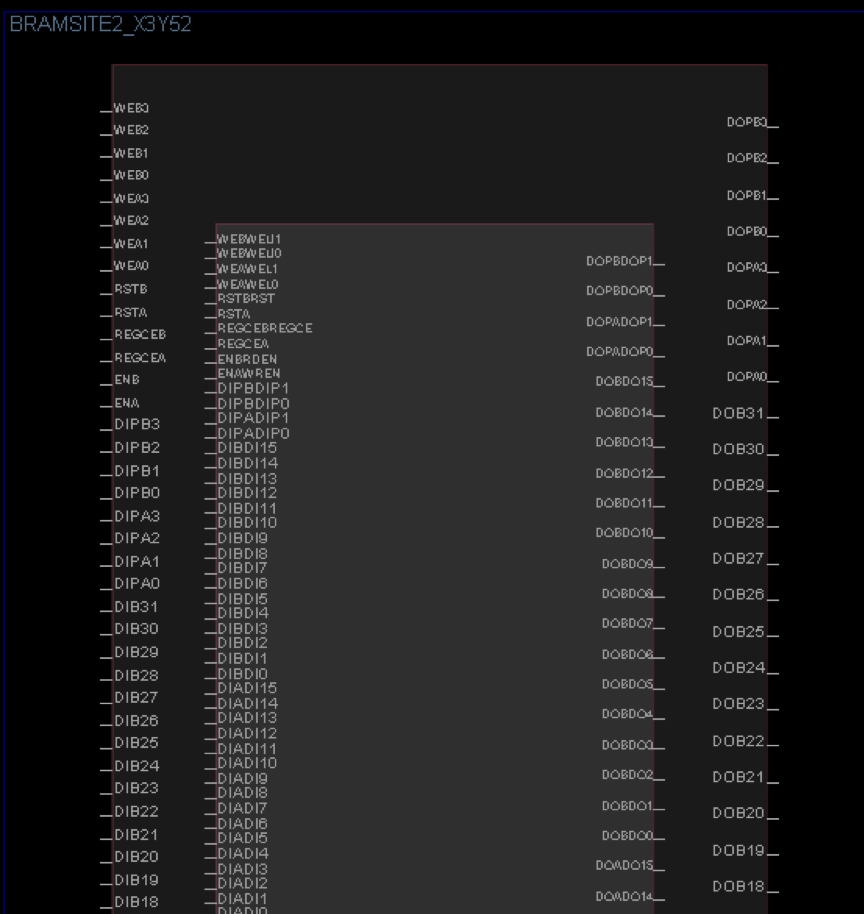

block ram资源

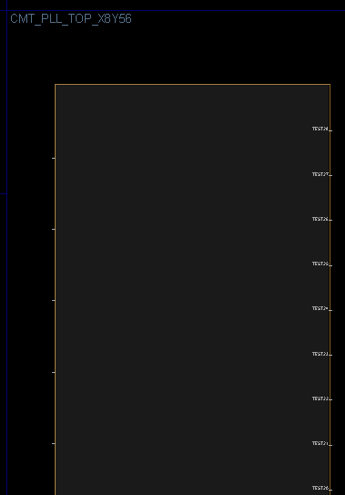

时钟管理单元

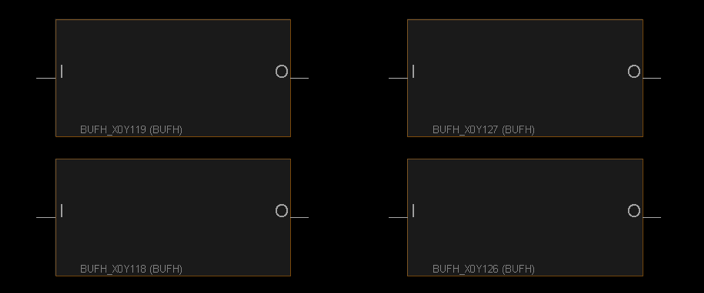

时钟驱动

FPGArely on its power、全方面、Multi-dimensional programmability,在航空航天、电子通信、银行金融、医疗设备、信息存储、数据处理、ASICMany industries or fields such as prototyping play an extremely important role.

5、FPGA专业术语

- ASIC,通常所说的ASICMainly refers to the gate array、Embedded array、标准单元 ASIC、结构化 ASIC 等.

- ASSP,相对于 ASIC This one is customized for a specific customer LSI,ASSP It is generic for a specific field or application LSI.

- CPLD,复杂可编程逻辑器件

- DLL,延迟锁定环

- IP,设计资产

- LUT,查找表

- LVDS,低电压差分信号

- PLD,可编程逻辑器件

- PLL,复杂可编程逻辑器件

- SerDes,串行器-解串器

范例

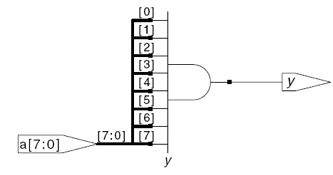

八输入与门

逻辑表达式 y = a[7] & a[6] & a[5] & a[4] & a[3] & a[2] & a[1] & a[0];

Its circuit diagram is:

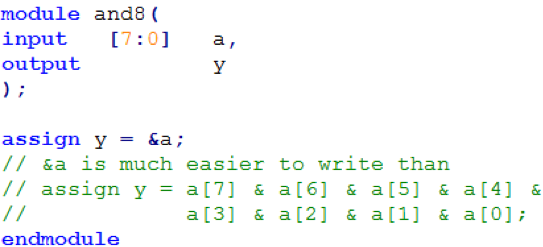

Verilog代码:

语法说明:

a[7]

:可将一个多位宽信号中的一位或多位以此种方式进行单独处理

&

:按位与、归并与操作,如该操作符只有一个操作数时,则将该操作数的所有位进行相与操作,可以实现与注释部分相同的功能,但写法更简洁.

边栏推荐

猜你喜欢

随机推荐

国内十大活跃报表 BI 产品深度对比及点评

毕昇编译器优化:Lazy Code Motion

Gartner全球集成系统市场数据追踪,超融合市场增速第一

国内BI厂商一览

UNI-APP_ monitor page scroll h5 monitor page scroll

DXF笔记:文字对齐的研究

继承关系下构造方法的访问特点

UNI-APP_监听页面滚动h5监听页面滚动

Install win7 virtual machine in Vmware and related simple knowledge

金仓数据库 KingbaseGIS 使用手册(6.6. 几何对象校验函数、6.7. 空间参考系函数)

shell数组

shell array

力扣:322. 零钱兑换

浅析量股票化交易的发展现状

干涉BGP的选路---社团属性

Leetcode 530. 二叉搜索树的最小绝对差

setter与getter访问器属性——数据驱动显示

Chapter 15 HMM模型

Leetcode 701. 二叉搜索树中的插入操作

金仓数据库 KingbaseGIS 使用手册(6.4. 几何对象存取函数)