当前位置:网站首页>【数字赛道命题三】基于复旦微FPGA平台实现H.264视频解码

【数字赛道命题三】基于复旦微FPGA平台实现H.264视频解码

2022-08-11 11:42:00 【数字积木】

一、 赛题

基于复旦微FPGA平台实现视频解码

要求:

1、 使用verilog实现H.264视频解码功能;

2、 图像分辨率不低于720P(1280x720);

3、 在复旦微电子的FPGA平台实现功能;

二、 赛题指定方案

1、参赛队伍要求

团队3-4人

建议

(1)了解复旦微电子青龙PSOC的开发流程;

(2)熟悉verilog/VHDL等硬件实现语言,或对数字有了解的参加;

(3)了解AXI总线;

(4)熟悉c/c++,能够完成基于操作系统的应用开发。

2、初赛阶段

(1) 根据给定的硬件平台,实现视频编解码功能;

(2) 提交设计文档(组委会提供统一模板),并提供相应的工程文件(包括RTL和firmwire);

(3) 提供相关simulation报告;

(4) 评审委员会根据提交的材料进行打分,决定决赛队伍

(5) 赛程:3个半月

3、赛前培训

(1)地点:线上培训

(2)内容:FM 硬件平台介绍;Procise工具介绍;赛道赛题解释

(3)时间:1~2天

4、决赛阶段

(1)各参赛队伍根据培训内容,在复微FPGA平台上实现工程;

(2)输出FPGA上的演示demo和相关文档

(3)评审委员会根据演示demo效果和性能指标进行打分

(4)赛程:2-5天

5、答辩

参赛选手参加此环节。

“复微杯”官方微信公众号

快人一步获取更多赛事信息

更多“复微杯”赛事培训、指导视频

尽在“复旦微电子集团官方B站平台”

请各位同学扫码关注

边栏推荐

- @Transactional注解加不加 rollbackFor = Exception.class 的区别?

- 云原生 · 镜像详解

- 2022 OceanBase 年度发布会:发布四大策略,迈入4.0时代

- 文献阅读(185)Co-design

- openEuler小程序会议指南

- 鸿海董事长刘扬伟:市场对智能手机和其他消费电子产品的需求正在放缓

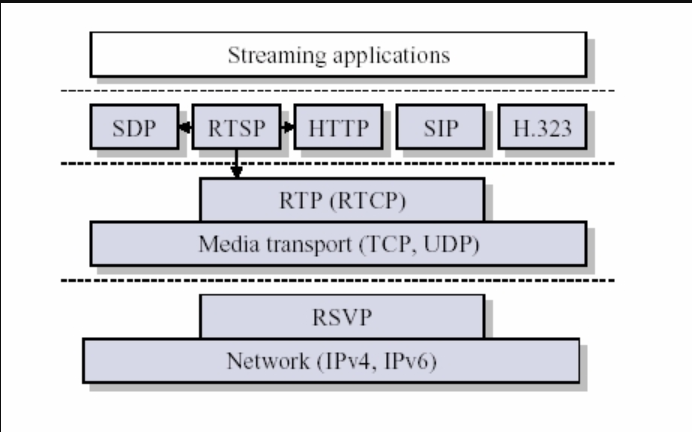

- From Douyin to Volcano Engine——Seeing the Evolution and Opportunities of Streaming Media Technology

- 在华门店数超星巴克,瑞幸咖啡完成“逆袭”?

- 7月月更开奖啦!快来看看你中奖了吗?

- 嵌入式开发:提示和技巧——退出时休眠

猜你喜欢

随机推荐

【项目篇- 项目团队部分怎么写、如何作图?(两千字图文总结建议)】创新创业竞赛项目计划书、新苗国创(大创)申报书、挑战杯创业计划竞赛

参与openEuler社区不到1年,我成为了Maintainer……

From Douyin to Volcano Engine——Seeing the Evolution and Opportunities of Streaming Media Technology

学习二叉树

兴盛优选:时序数据如何高效处理?

【毕业设计】远程智能浇花灌溉系统 - stm32 单片机 嵌入式 物联网

MySQL之JDBC编程增删改查

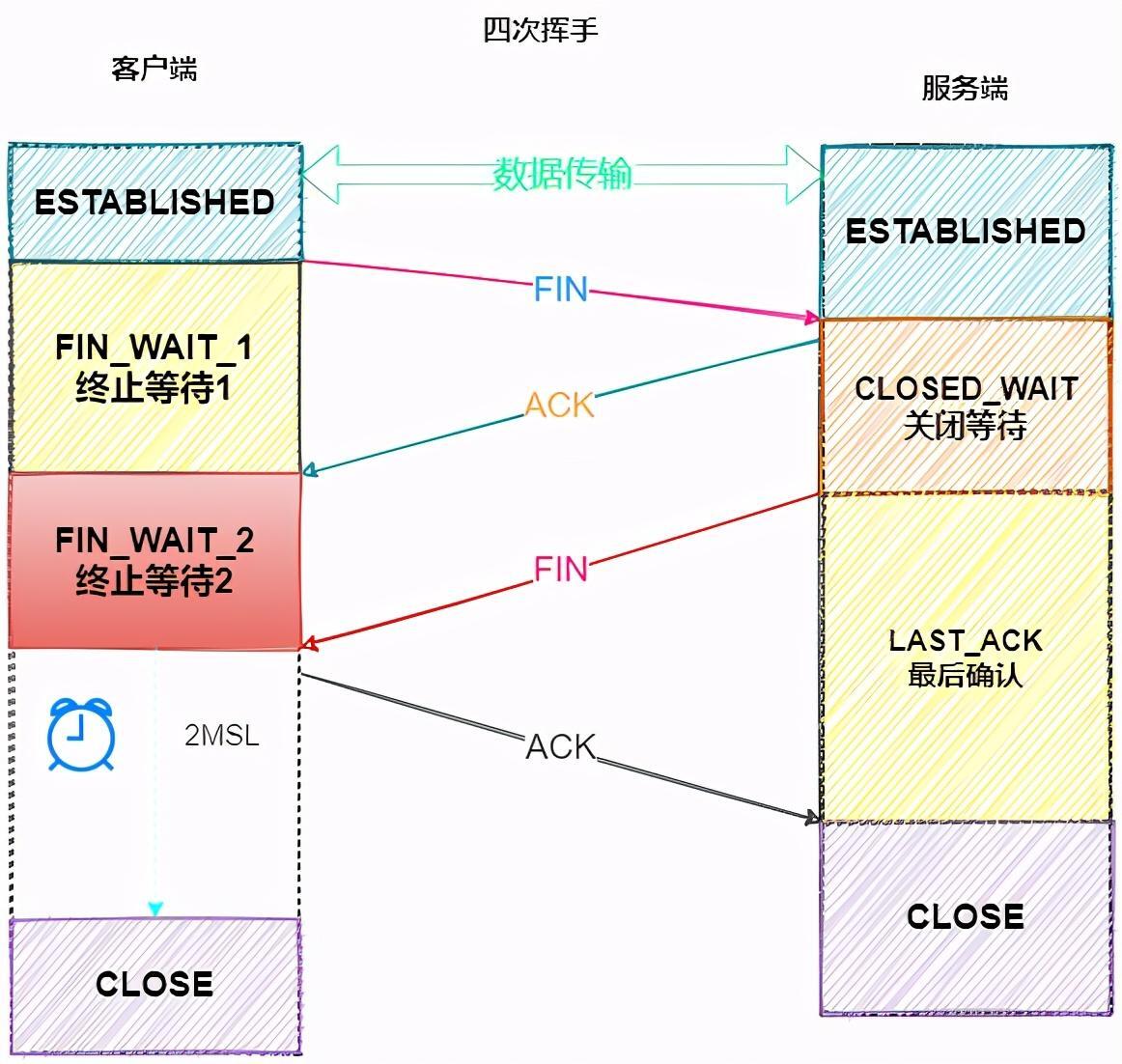

The old saying: The interview must ask "Three handshakes, four waves", so you can't forget it

反射获取DLL中的字段、属性、方法、泛型方法(C#)

fiddler双向认证

Hugging Face快速入门(重点讲解模型(Transformers)和数据集部分(Datasets))

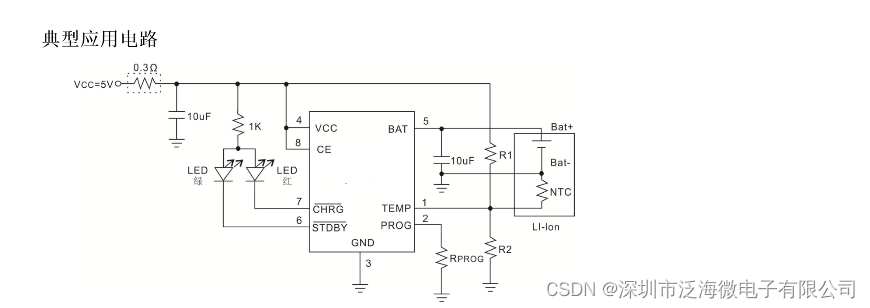

SM5200原厂SOT23-6 500mA 线性锂电子替代芯片

文献阅读(185)Co-design

HyperLynx(五)反射仿真

Go编译原理系列10(逃逸分析)

七、一起学习Lua 函数

怎么了

PG--核心技术--HOT

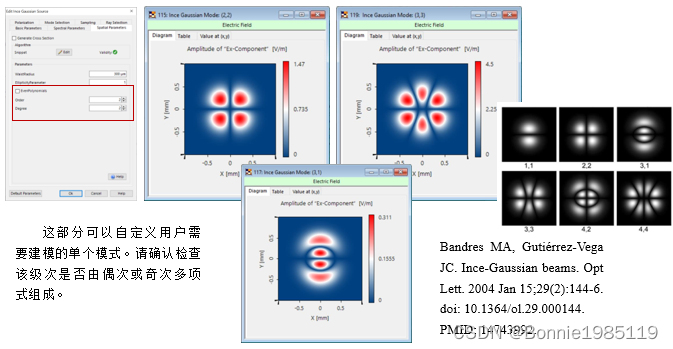

Ince-Gaussian mode

Configuring vim(12) from scratch - theme configuration