当前位置:网站首页>基于 VIVADO 的 AM 调制解调(1)方案设计

基于 VIVADO 的 AM 调制解调(1)方案设计

2022-08-11 08:30:00 【chylinne】

一、AM 原理

常规调幅(conventional AM)信号(简称 AM 信号)的时域表达式为:

![s_{AM}(t)=A_{c}[1+m(t)]cos2\pi f_{c}t](http://img.inotgo.com/imagesLocal/202208/11/202208110830072787_3.gif)

其中, 是载波幅度,

是载波幅度, 是调制信号(基带消息信号)。

是调制信号(基带消息信号)。 是已调信号,它的包络直接对应着信号

是已调信号,它的包络直接对应着信号  的变化规律。

的变化规律。

定义调幅指数(modulation index),或调制深度,为:

![\beta _{AM}=\frac{max[s_{AM}(t)]-A_{c}}{A_{c}}=max[m(t)]](http://img.inotgo.com/imagesLocal/202208/11/202208110830072787_10.gif)

它反应了信号在载波幅度上的“调制程度”。

对应的解调方法一般是使用包络检波器,即直接提取  的实包络来恢复消息信号。包络检波器实质上是一个整流器与一个低通滤波器的结合,这主要是利用了 RC 电路中电容放电慢的特点来提取提取

的实包络来恢复消息信号。包络检波器实质上是一个整流器与一个低通滤波器的结合,这主要是利用了 RC 电路中电容放电慢的特点来提取提取  的包络。因此,我们具体可以通过全波整流并低通滤波两步来实现。

的包络。因此,我们具体可以通过全波整流并低通滤波两步来实现。

二、目标设计

完成信号 AM 调制和解调功能,目标如下:

(1)载波信号频率范围:1M-10MHz,分辨率 0.01 MHz。

(2)调制信号为单频正弦波信号,频率范围:1kHz-10kHz,分辨率 0.01kHz。

(3)调制深度 0-1.0,步进 0.1,精度优于 5%。

(4)使用 MATLAB 对比调制信号和解调信号指标。

(5)载波信号频率、调制信号频率和调制深度可设置。

(6)完成 Testbench 仿真验证。

三、方案设计

1、原理框图

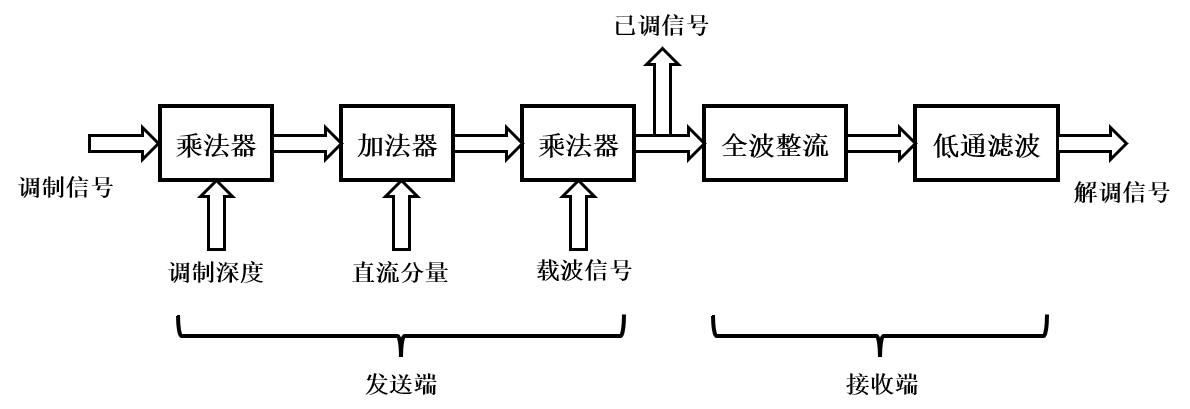

AM 调制解调较简单,其原理框图设计如下所示:

2、实现工具

原理框图中的调制信号、载波信号可以通过 Xilinx VIVADO 中调用 DDS IP 核进行配置得到;乘法器、加法器则直接调用 Xilinx VIVADO 的 IP 核进行使用;低通滤波器需要在调用 IP 核的基础上,利用 MATLAB 的滤波器设计工具生成 .coe 文件进行参数配置。

3、参数设计

(1)系统参数

时钟频率  设置为 100 MHz。

设置为 100 MHz。

(2)发送端参数

对于调制信号和载波信号而言,我们使用的是 DDS IP 核,根据 Xilinx 的 dds_compiler 官方手册给出的公式

我们可以利用系统时钟频率  、输出信号频率

、输出信号频率  、相位累加器位宽

、相位累加器位宽  来计算出所需的频率控制字

来计算出所需的频率控制字  的数值。

的数值。

对于调制信号,我们设置输出信号频率  为 8 kHz,相位累加器位宽

为 8 kHz,相位累加器位宽  为 24。

为 24。

对于载波信号,我们设置输出信号频率  为 8 MHz,相位累加器位宽

为 8 MHz,相位累加器位宽  为 16。

为 16。

类似的,根据手册,我们同样可以根据公式

来计算相位控制字  的数值,本次设计中暂不用考虑设计相位控制字。

的数值,本次设计中暂不用考虑设计相位控制字。

然后,我们将调制深度  设置为 0.9,直流分量

设置为 0.9,直流分量  幅度大小设置为 127。这里需要注意的是,调制深度不能直接在代码中写小数,我们可以将

幅度大小设置为 127。这里需要注意的是,调制深度不能直接在代码中写小数,我们可以将  乘上 256 后取整,再与调制信号相乘,最后将结果右移 8 位即可。

乘上 256 后取整,再与调制信号相乘,最后将结果右移 8 位即可。

(3)接收端参数

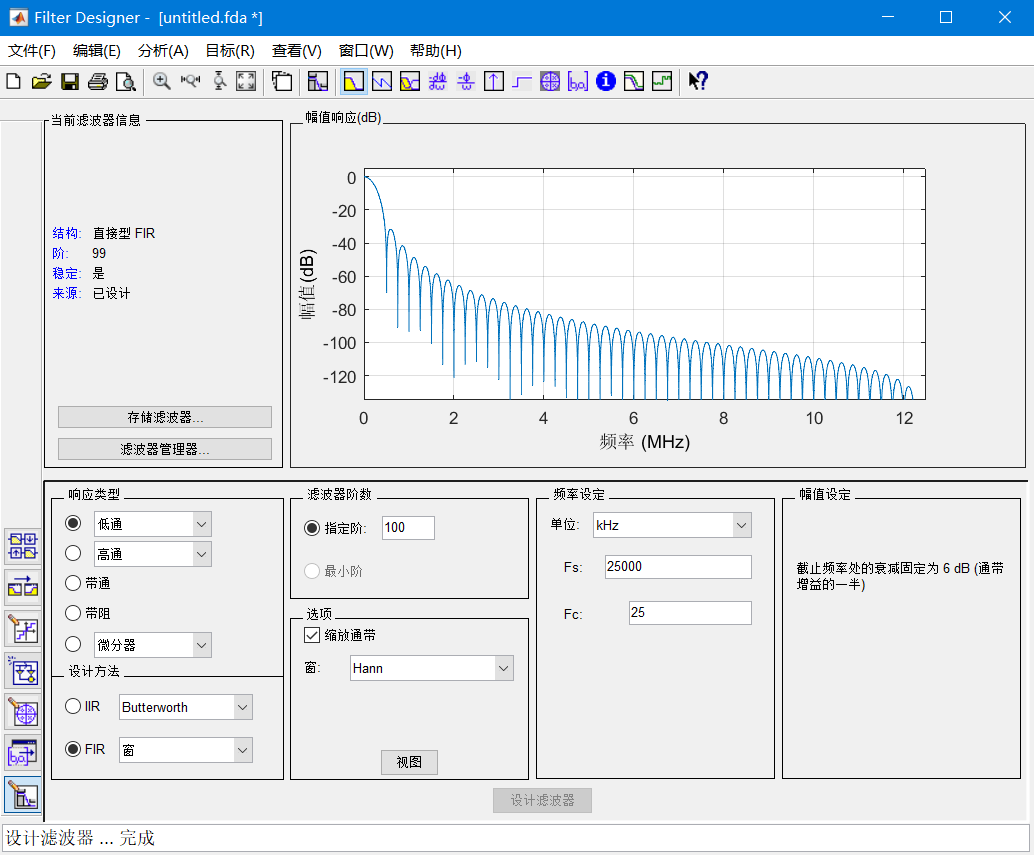

在 MATLAB 命令行窗口输入 filterDesigner 进入滤波器设计 GUI 界面。滤波器选择 fir 低通滤波器,滤波器阶数设置为 100,采样频率为 25 MHz,截止频率为 25kHz。

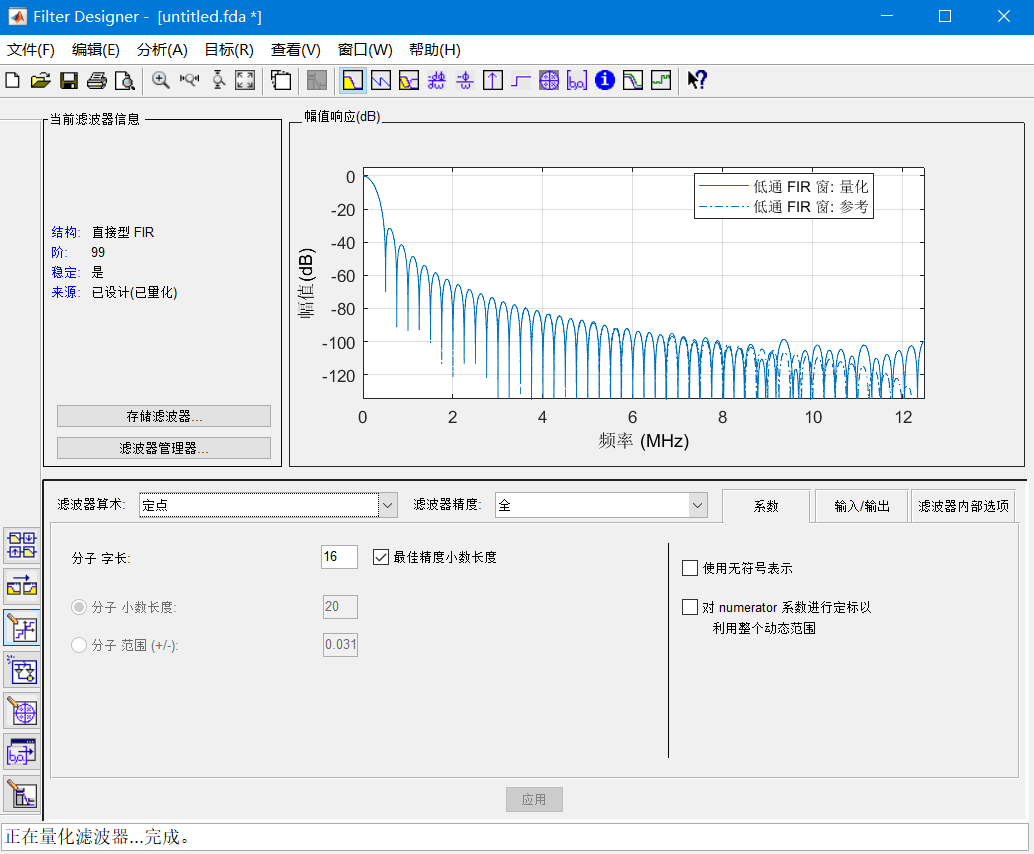

下图量化完成后,点击菜单栏目标(Targets),输出为 .coe 文件,在调用 fir IP 核时引用。

边栏推荐

- gRPC系列(四) 框架如何赋能分布式系统

- 零基础SQL教程: 基础查询 05

- 【系统梳理】微服务的注册和发现中心

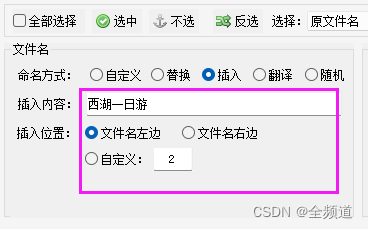

- The easiest trick to support quick renaming of various files

- Has legal counsel become a tasteless product of law firms?

- eureka和consul的区别

- Analysys and the Alliance of Small and Medium Banks jointly released the Hainan Digital Economy Index, so stay tuned!

- 【云原生】云原生在网络安全领域的应用

- 机器学习(二)线性回归

- 【415. 字符串相加】

猜你喜欢

基于C#通过PLCSIM ADV仿真软件实现与西门子1500PLC的S7通信方法演示

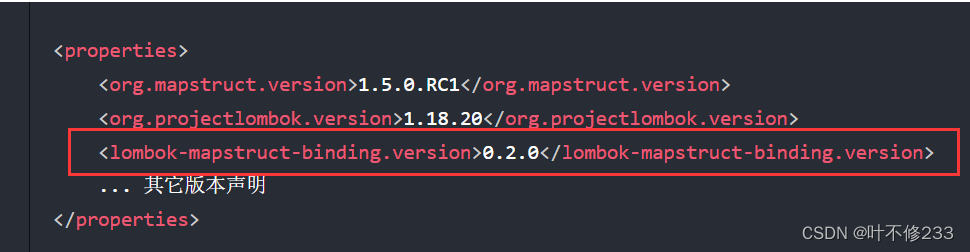

记录一些遇见的bug——Lombok和Mapstruct的冲突导致,A component required a bean of type ‘com.XXX.controller.converter.

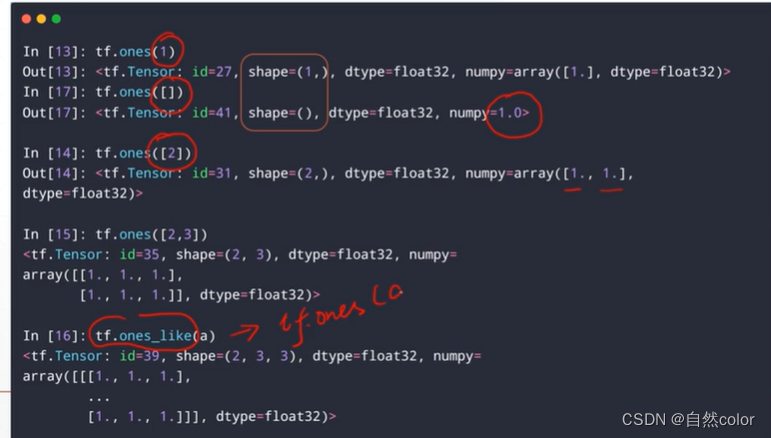

tensorflow 基础操作1(tensor 基本属性 , 维度变换,数学运算)

The easiest trick to support quick renaming of various files

Notable NFT development trends in 2022

9、Neural Sparse Voxel Fields

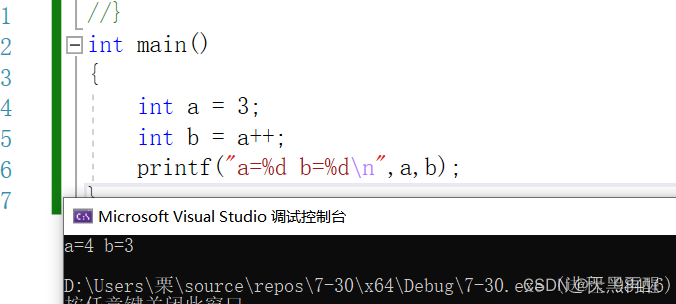

C语言操作符详解

One network cable to transfer files between two computers

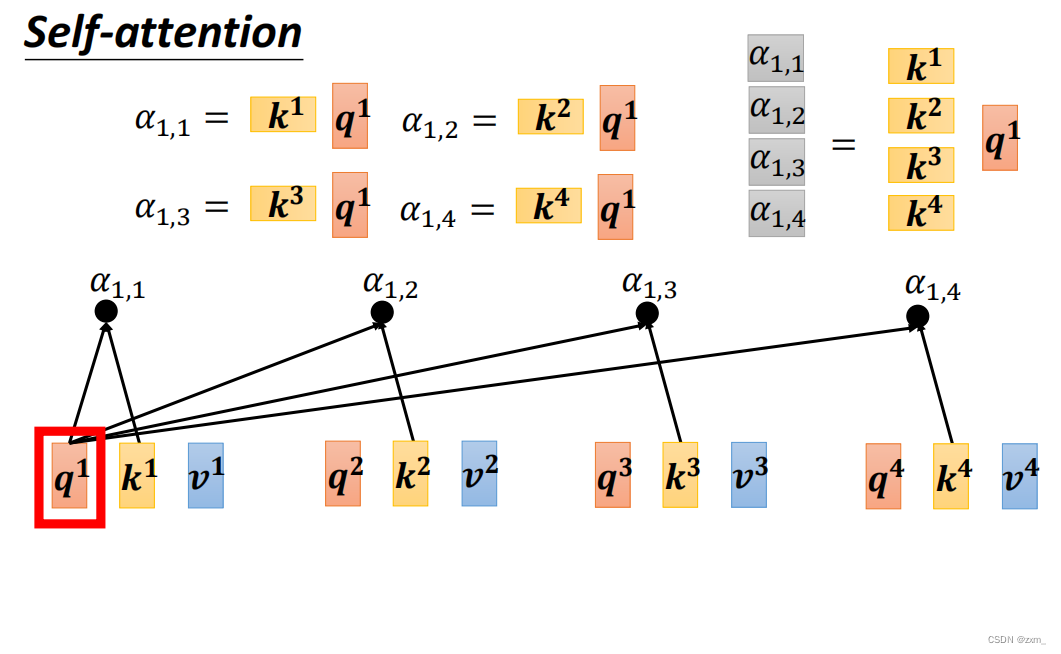

小目标检测3_注意力机制_Self-Attention

囍楽cloud task source code

随机推荐

RestTemplate工具类

Kotlin算法入门求自由落体

AcWing 272. 最长公共上升子序列

欧拉函数(用欧拉筛法求欧拉函数)

Alibaba Sentinel - Slot chain解析

Unity3D——自定义类的Inspector面板的修改

机器学习(一)数据的预处理

查询跟踪快递单号物流,智能分析物流中转有延误的单号

数据库无法启动,报无法分配内存,怎么处理

js将table生成excel文件并去除表格中的多余tr(js去除表格中空的tr标签)

通过Xshell连接Vagrant创建的虚拟机

XXL-JOB 分布式任务调度中心搭建

关于架构的认知

pycharm中绘图,显示不了figure窗口的问题

2022年值得关注的NFT发展趋势

你有对象类,我有结构体,Go lang1.18入门精炼教程,由白丁入鸿儒,go lang结构体(struct)的使用EP06

Features of LoRa Chips

基础SQL——DDL

@RequiredArgsConstructor注解

gRPC系列(一) 什么是RPC?