当前位置:网站首页>MSP430学习总结——时钟UCS

MSP430学习总结——时钟UCS

2022-08-11 05:25:00 【LIGAZN菜鸟】

目录

前言

MSP430具有超低功耗的特点,由于前段时间在准备电子设计大赛时学习了这款单片机,当时花了很多时间才把时钟篇看懂一点,特意在这里记录一下学习总结。我用的是MSP430F5529单片机,这款单片机可以直接用USB线连接电脑,在CCS上直接下载和调试程序,用起来还是很方便的。和STM32一样,MSP430的时钟是整个系统正常工作必不可少的一条件,我们学习他的重要性不言而喻。MSP430是16位的单片机,一个很大的优势就在于超低功耗,因此灵活且正确地配置是时钟是非常重要的,话不多说,接下来就以MSP430F5529为例来介绍一下MSP430的时钟系统UCS。参考的资料有数据手册和User's Guide以及一些大佬的博客。

(23条消息) MSP430F5529时钟25MHZ设置方式,觉得很有帮助(转载)_不说二话的自家人的博客-CSDN博客_msp430f5529时钟配置

(23条消息) MSP430F5529系统升压与时钟配置,初学者必看!_不说二话的自家人的博客-CSDN博客_msp430f5529时钟配置

一、MSP430时钟系统

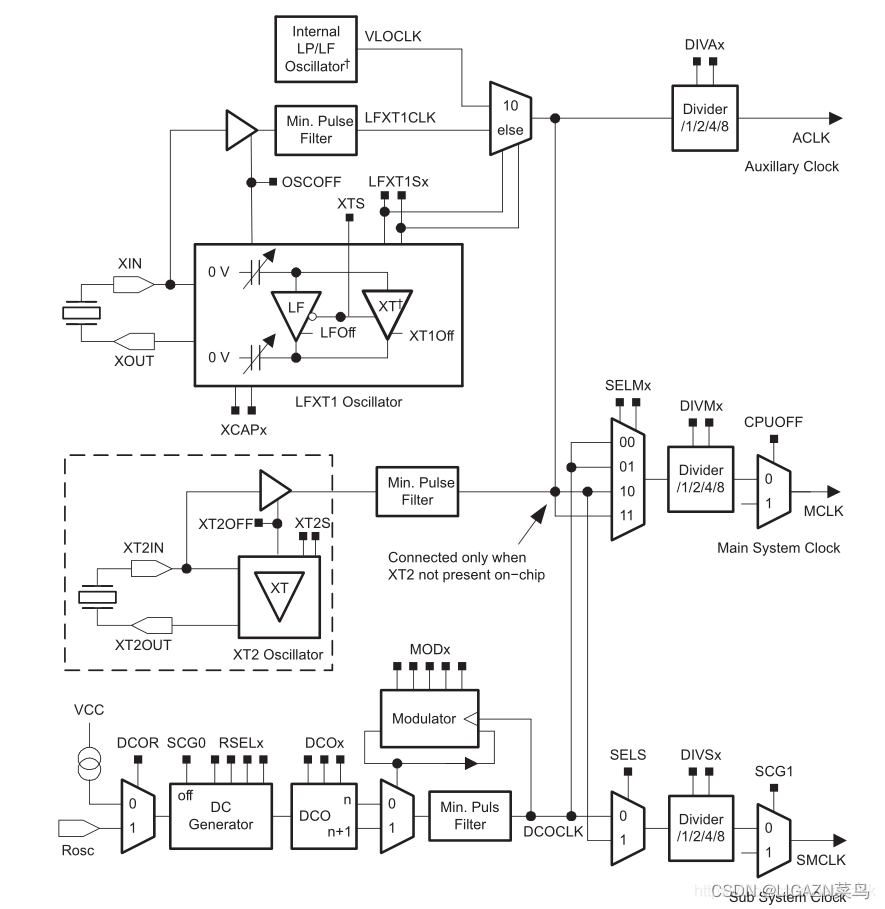

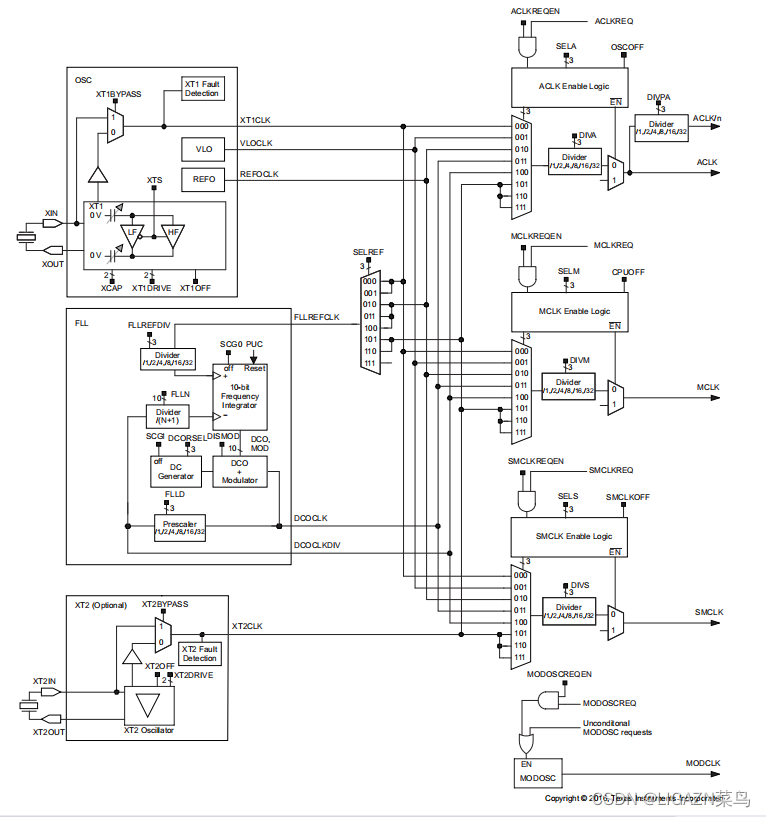

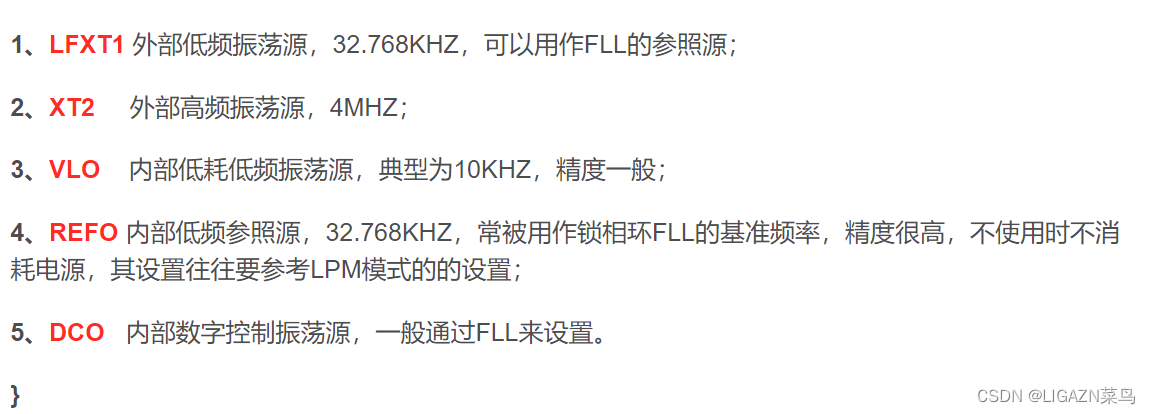

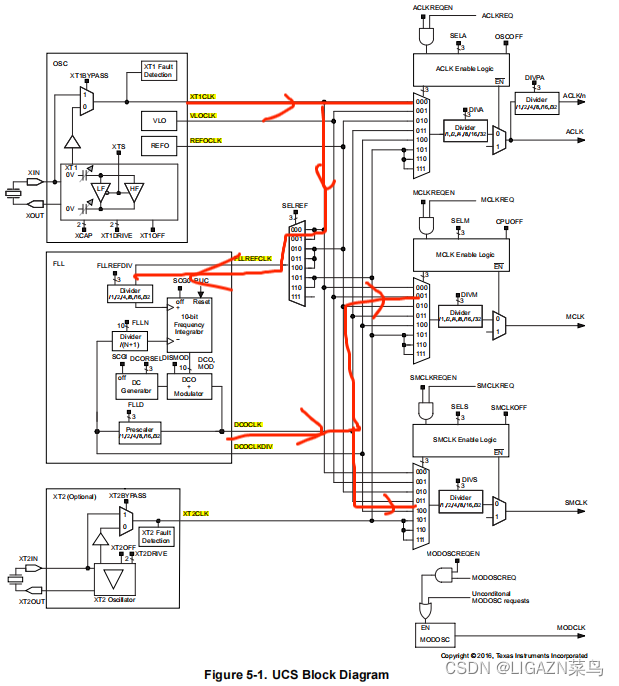

MSP430有五个时钟源,他们分别是XT1CLK,VLOCLK,REFOCLK,DCOCLK,XT2CLK。VLOCLK是内部低频低功耗时钟源(Internat LP/LF Oscillator)生成,XT1CLK由外部低频时钟源1(LFXT1 Osoillator)配合XIN与XOUT上外接的晶振电路或时钟信号生成,REFOCLK由内部修剪的低频振荡器产生,DCOCLK由内部数字控制振荡器(DCO)产生, XT12CLK由外部高速时钟源2(XT2 Osoillator)配合XT2IN与XT2OUT上外接的晶振电路或时钟信号生成。其中XTICLK和XT2CLK由外部晶振电路产生,时钟频率较为稳定和精确。其余的为内部的振荡器产生。下图为MSP430的时钟框图

这五个时钟源并不是直接提供给外设,而是先驱动三个时钟信号,ACLK(Auxiliary clock)辅助时钟,MCLK(Master clock)主时钟,SMCLK(Subsystem master clock)子系统主时钟。ACLK可以设置为XT1CLK, REFOCLK, VLOCLK, DCOCLK, DCOCLKDIV, XT2CLK,这其中之一经过1, 2, 4, 8, 16, or 32分频得到。ACLK可以在各个外设配置时被选择使用。和ACLK类似,MCLK为CPU和单片机系统提供时钟信号。SMCLK也可以被各个外设使用。

了解了MSP430的时钟系统之后就可以去配置MSP430的时钟。前面提到了ACLK,MCLK,SMCLK的时钟信号来源可以是XT1CLK, REFOCLK, VLOCLK, DCOCLK, DCOCLKDIV, XT2CLK的其中一个,并且需要经过分频器才能成为三大时钟信号,我们配置时钟无非就是配置时钟来源和分频系数。

二、MSP430的时钟配置

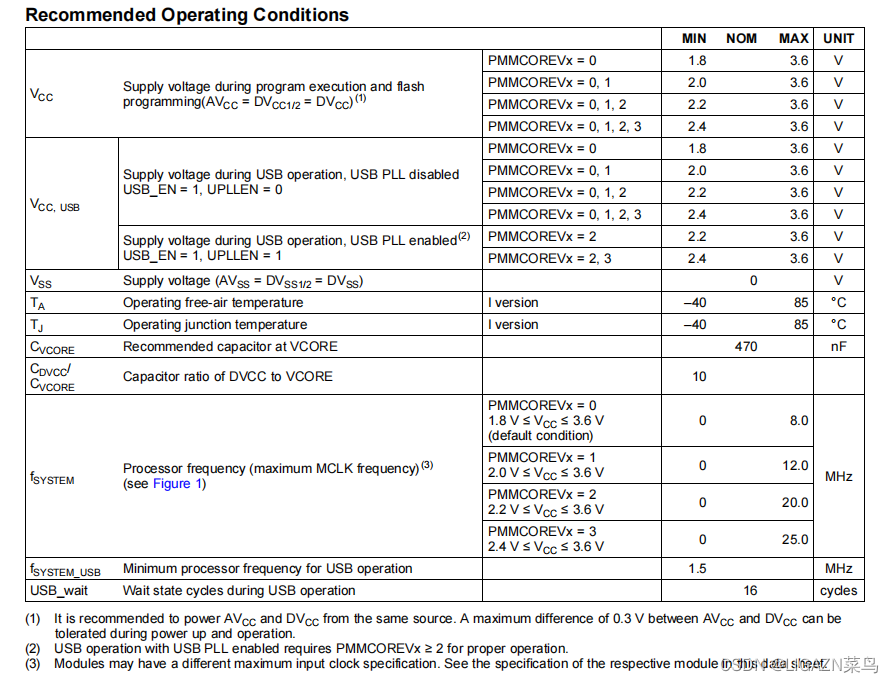

1.在配置时钟频率前要配置响应的电压

代码如下

void upVcc(void)//核心电压上升3级

{

PMMCTL0_H = 0xA5; //开启PMM电源管理,即开锁

SVSMLCTL |= SVSMLRRL_1 + SVMLE; //配置SVML电压

PMMCTL0 = PMMPW +PMMCOREV_3; //配置内核电压,选择3级

while((PMMIFG & SVSMLDLYIFG)==0); //等待配置完成

PMMIFG &=~ (SVMLVLRIFG + SVMLIFG + SVSMLDLYIFG);

if((PMMIFG & SVMLIFG)==1)

while((PMMIFG & SVMLVLRIFG)==0);

SVSMLCTL &=~ SVMLE; //关闭SVML

PMMCTL0_H = 0x00; //锁存配置,即关锁

}2.配置时钟频率

配置SMCLK和MCLK为4M,ACLK为32.768khz

void UCS_Init(void)//配置主时钟MCLK和SMCLK为4M

{

// P1DIR |= BIT0; // ACLK set out to pins

// P1SEL |= BIT0;

P2DIR |= BIT2; // SMCLK set out to pins

P2SEL |= BIT2;

// P7DIR |= BIT7; // MCLK set out to pins

// P7SEL |= BIT7;

P5SEL |= BIT2+BIT3; // Port select XT2

UCSCTL6 &= ~XT2OFF; // Enable XT2

UCSCTL3 |= SELREF_2; // FLLref = REFO

// Since LFXT1 is not used,

// sourcing FLL with LFXT1 can cause

// XT1OFFG flag to set

UCSCTL4 |= SELA_2; // ACLK=REFO,SMCLK=DCO,MCLK=DCO

// Loop until XT1,XT2 & DCO stabilizes - in this case loop until XT2 settles

do

{

UCSCTL7 &= ~(XT2OFFG + XT1LFOFFG + DCOFFG);

// Clear XT2,XT1,DCO fault flags

SFRIFG1 &= ~OFIFG; // Clear fault flags

}while (SFRIFG1&OFIFG); // Test oscillator fault flag

UCSCTL6 &= ~XT2DRIVE0; // Decrease XT2 Drive according to

// expected frequency

UCSCTL4 |= SELS_5 + SELM_5; // SMCLK=MCLK=XT2

}配置25M时钟频率

void timerup(void)//配置时钟25MHZ

{

UCSCTL3 = SELREF_2;

UCSCTL4 |= SELA_2;

__bis_SR_register(SCG0);

UCSCTL0 = 0x0000;

UCSCTL1 = DCORSEL_7;//50Mhz范围

UCSCTL2 = FLLD_0 + 762; //(762+1)*32768==25MHZ

__bic_SR_register(SCG0);

__delay_cycles(782000);延时

while(SFRIFG1 & OFIFG)//等待设置完成

{

UCSCTL7 &=~ (XT2OFFG + XT1LFOFFG + DCOFFG);

SFRIFG1 &=~ OFIFG;

}

//UCSCTL4 = UCSCTL4&(~(SELS_7|SELM_7))|SELS_3|SELM_3;

}配置25M的时钟频率的最后的逻辑走向应该是这样的,如下图

总结

MSP430的时钟配置很复杂,目前的理解就是这些,后续有更深的理解会添加上去,也请各位大佬不吝赐教。

边栏推荐

- 安全帽识别

- 【调试记录1】提高MC3172浮点运算能力,IQmath库的获取与导入使用教程

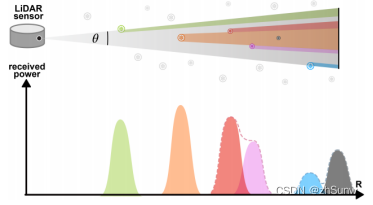

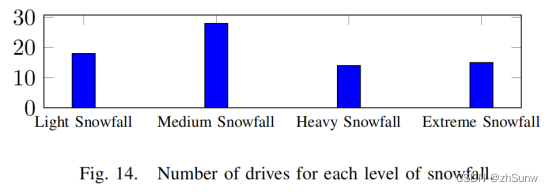

- LiDAR Snowfall Simulation for Robust 3D Object Detection

- Reconstruction and Synthesis of Lidar Point Clouds of Spray

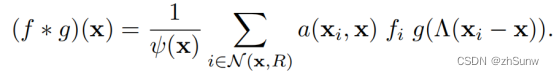

- LAGRANGIAN FLUID SIMULATION WITH CONTINUOUS CONVOLUTIONS

- Maykle Studio - HarmonyOS Application Development Fourth Training

- CVPR2020:Seeing Through Fog Without Seeing Fog

- 目标检测——Faster R-CNN 之 Fast R-CNN

- The working principle and industry application of AI intelligent image recognition

- 实时姿态估计--基于空洞卷积的人体姿态估计网络

猜你喜欢

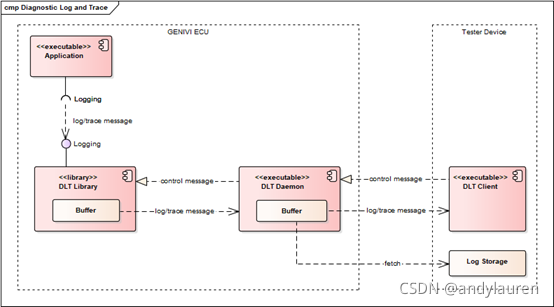

Diagnostic Log and Trace——dlt的编译和安装

LiDAR Snowfall Simulation for Robust 3D Object Detection

The selection points you need to know about the helmet identification system

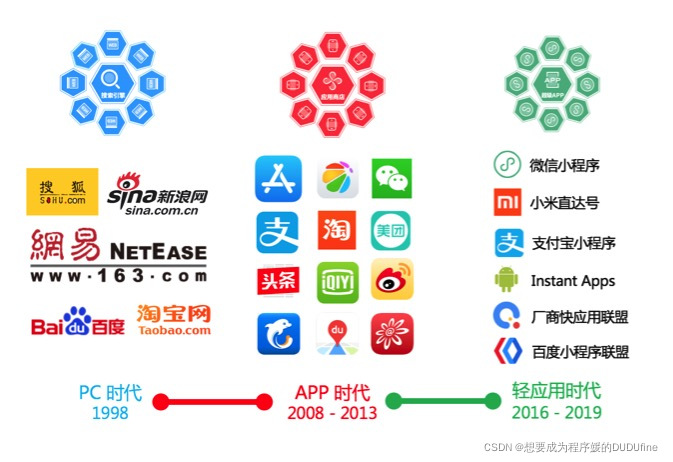

小程序技术原理分析

OpenPCDet installs the latest version: spconv in one step

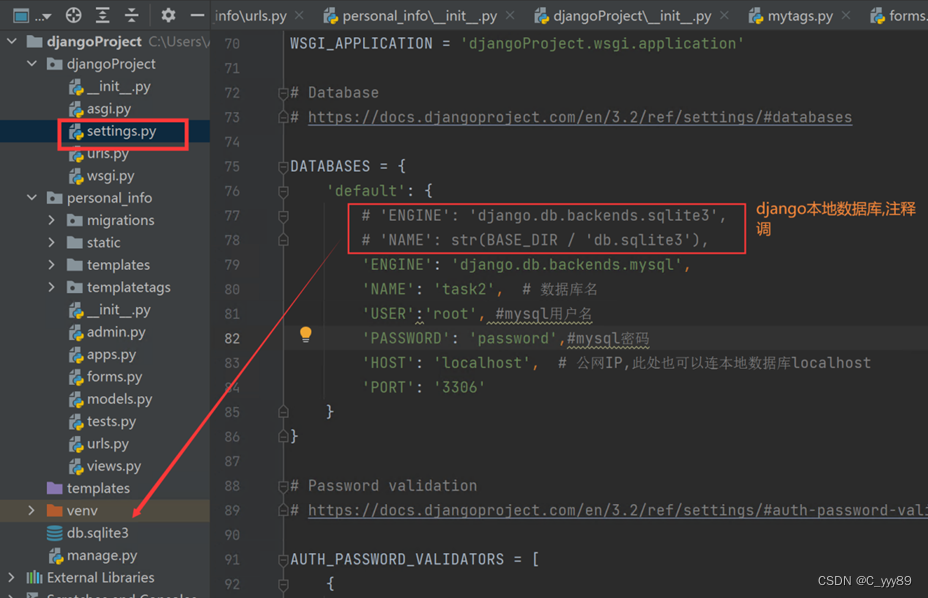

Maykel Studio - Django Web Application Framework + MySQL Database Fourth Training

恶劣天气 3D 目标检测数据集收集

LAGRANGIAN FLUID SIMULATION WITH CONTINUOUS CONVOLUTIONS

音乐竞品分析:酷狗、QQ音乐、网易云、酷我、汽水音乐

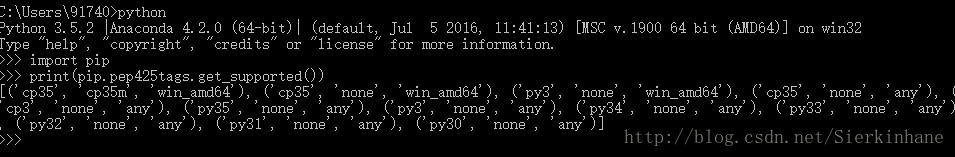

pip安装报错:is not a supported wheel on this platform

随机推荐

关于mmdetection框架实用小工具说明

ASP.NET MVC 4中实现action的事务功能

Maykle Studio - HarmonyOS Application Development Fourth Training

pip安装报错:is not a supported wheel on this platform

Asp doNet Mvc4绑定js脚本用法

安全帽识别系统-为安全生产保驾护航

电商机会:私域

Hardhat Recognition System - Solving Regulatory Conundrums

通用的 kernel和 userspace Makefile

Waymo数据集使用介绍(waymo-open-dataset)

跨应用间调用: URL Scheme

Introduction of safety helmet wearing recognition system

Wisdom construction site safety helmet identification system

目标检测学习目录(持续更新)

Node-3.构建Web应用(二)

梅科尔工作室-HarmonyOS应用开发的第二次培训

恶劣天气 3D 目标检测数据集收集

CVPR2020:Seeing Through Fog Without Seeing Fog

解决jupyter中import torch出错问题

Maykel Studio - Django Web Application Framework + MySQL Database Fourth Training