当前位置:网站首页>The vivado project corresponding to the board is generated by TCL script

The vivado project corresponding to the board is generated by TCL script

2022-04-23 18:07:00 【Zhuge hammer who loves learning】

Source of problem

Try according to PYNQ v2.4 Source code refactoring Base Overlay, Think from tcl Scripts are generated directly Vivado engineering

Resources and development kits

- Vivado 2018.3

- On time atomic Star Development Board Zynq7010 (xc7z010clg400-1 chip )

Operation record

- Download it in advance PYNQ v2.4 Source code ( Official search v2.4 Of Release)

- View and modify Tcl Script base.tcl ( route

<PYNQ repository>/boards/Pynq-Z1/base) - The first part of the script 105 That's ok , take

-partThe parameters are modified to the chip model of the board , I am herexc7z010clg400-1

if {

$list_projs eq "" } {

create_project ${overlay_name} ${overlay_name} -part xc7z010clg400-1

}

Save and exit

- open Vivado 2018.3, Found at the bottom Tcl Console

- Type the command... In the input box

cd <PYNQ repository>/boards/Pynq-Z1/base

source ./base.tcl

- Wait for a while , complete , open Block Design Check it out.

Follow up on Base Overlay Of Block Design Tailoring , modify xdc Constraint file , Generate bit flow , Development on the board

版权声明

本文为[Zhuge hammer who loves learning]所创,转载请带上原文链接,感谢

https://yzsam.com/2022/04/202204231801055352.html

边栏推荐

- Map basemap Library

- Read excel, int digital time to time

- ES6 face test questions (reference documents)

- 深度学习经典网络解析目标检测篇(一):R-CNN

- powerdesigner各种字体设置;preview字体设置;sql字体设置

- Realization of consumer gray scale

- re正則錶達式

- NVIDIA Jetson: GStreamer and openmax (GST OMX) plug-ins

- Docker 安装 Redis

- Thirteen documents in software engineering

猜你喜欢

Go的Gin框架学习

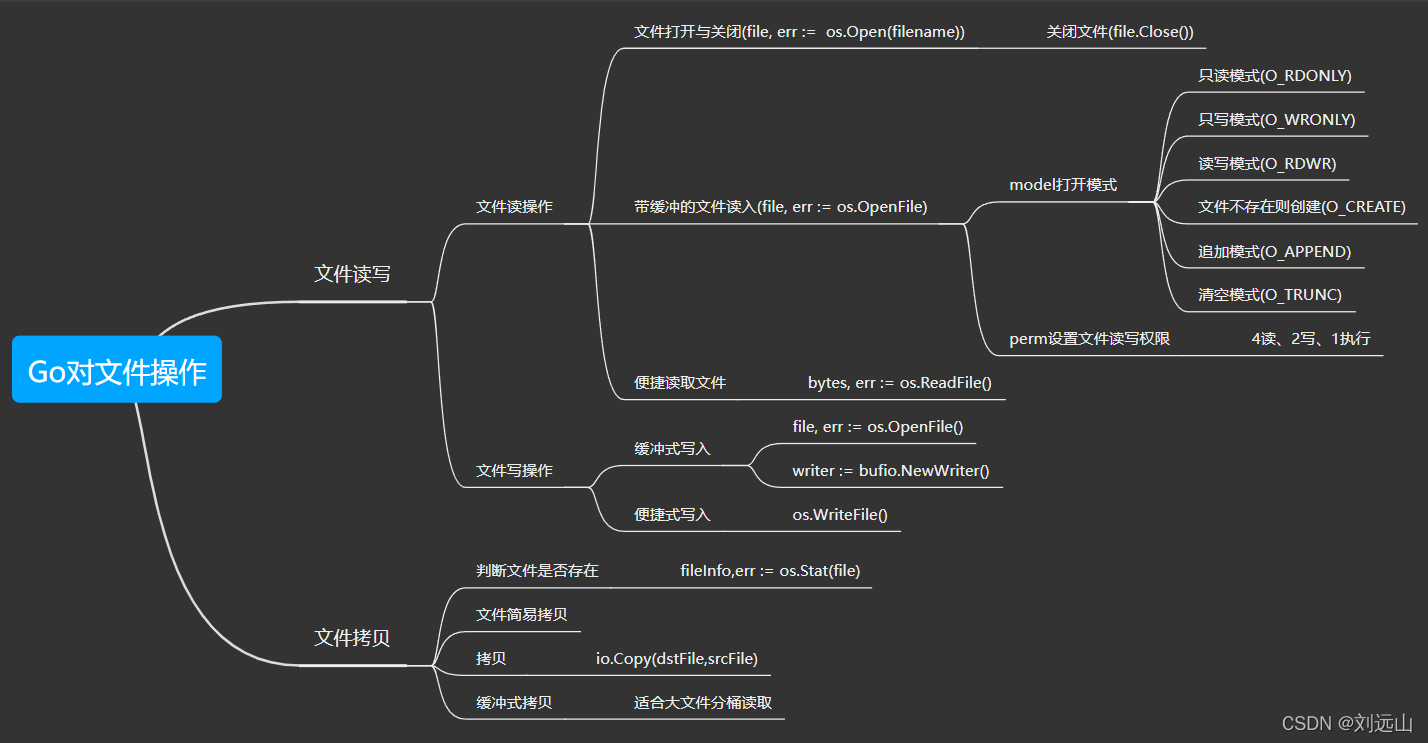

Go file operation

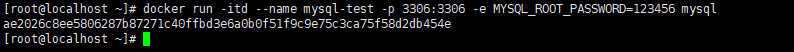

Docker installation MySQL

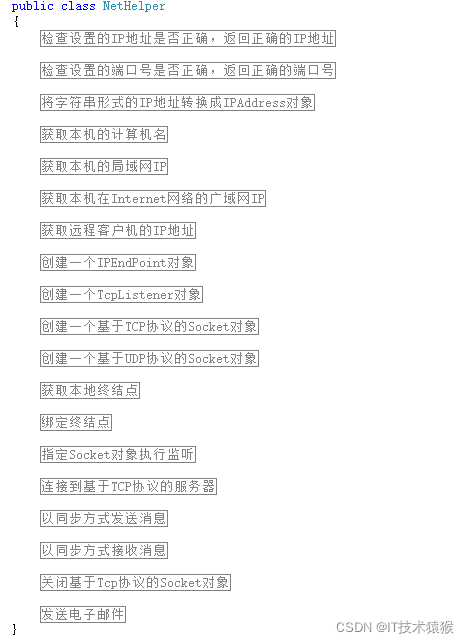

C network related operations

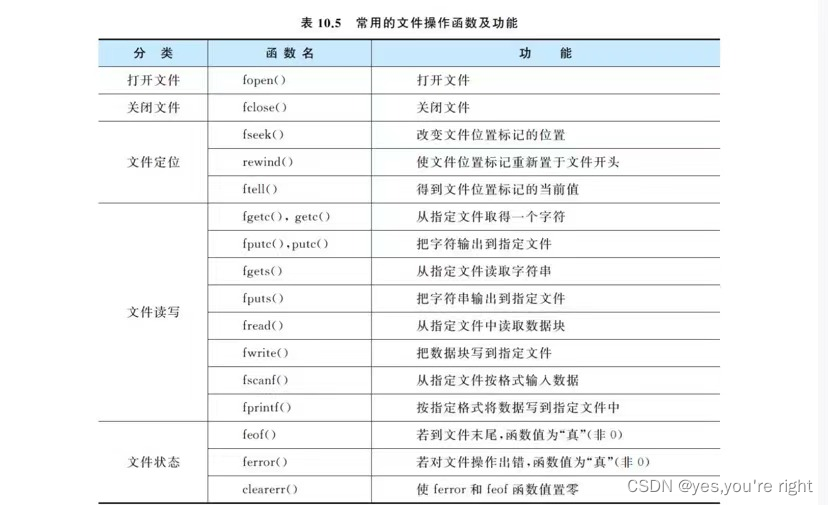

Using files to save data (C language)

![[UDS unified diagnostic service] v. diagnostic application example: Flash bootloader](/img/45/f9e24ae1c619f78aeeb7bcf12d6e5f.png)

[UDS unified diagnostic service] v. diagnostic application example: Flash bootloader

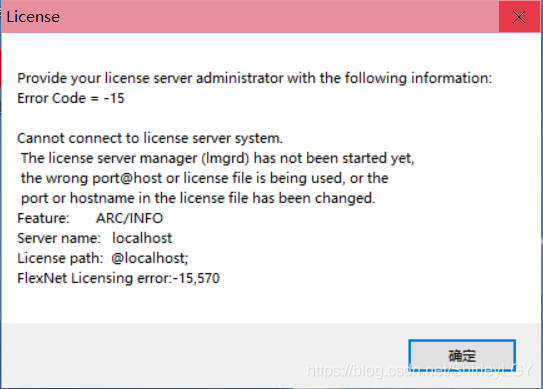

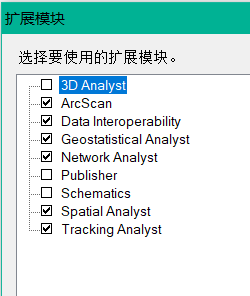

ArcGIS license error -15 solution

![[UDS unified diagnostic service] (Supplement) v. detailed explanation of ECU bootloader development points (2)](/img/91/3272d5ad04cd1d8476c739546f4356.png)

[UDS unified diagnostic service] (Supplement) v. detailed explanation of ECU bootloader development points (2)

Visualization of residential house prices

Batch export ArcGIS attribute table

随机推荐

Qt读写XML文件(含源码+注释)

JS high frequency interview questions

_ FindText error

Pointers in rust: box, RC, cell, refcell

Multi thread safe reference arc of rust

C language to achieve 2048 small game direction merging logic

Auto.js 自定义对话框

C [file operation] read TXT text by line

QTableWidget使用讲解

Robocode Tutorial 4 - robocode's game physics

Selenium + phantom JS crack sliding verification 2

Jenkspy package installation

cv_ Solution of mismatch between bridge and opencv

I / O multiplexing and its related details

Deep learning classic network analysis and target detection (I): r-cnn

Format problems encountered in word typesetting

Serialization scheme of serde - trust

Operators in C language

C network related operations

C language array processing batch data