当前位置:网站首页>STM32-中断优先级管理NVIC

STM32-中断优先级管理NVIC

2022-08-11 05:25:00 【Archimedes' boat】

目录

参考资料:

1、正点原子探索者STM32f407开发板-《STM32f407开发指南-库函数版本》-4.5小节;

2、STM32F4xx 官方参考资料《STM32F4xx中文参考手册》-第十章。

NVIC中断优先级分组

CM4内核支持256个中断,包括16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

STM32F4并只使用CM4部分中断:STM32F40xx、41xx有92个,42xx、43xx有96个。

探索者板使用的是40xx、41xx,有10内核中断和82个外部中断(全是可屏蔽中断),我们用的就是82个可屏蔽中断。

详见:《STM32F4xx中文参考手册》P234--表45和表46

然鹅,这么多中断,如果同时满足两个中断的条件,那么就需要制定先后顺序,比如A、B中断同时满足,就应该根据顺序先响应其中的某个,再响应另外一个。

在此就有了抢占优先级和响应优先级:

1、抢占优先级和响应优先级由共同的寄存器中的4位配置,从0000到1111,是SCB寄存器的4~7位,他们可以随意分组;

eg:抢占优先级占前1位,那么响应优先级就占后3位,如果设置为1101,那么抢占优先级就是1,响应优先级就是101,十进制就是5,这叫“分组配置”,而这四位的分组由SCB->AIRCR控制,是SCB寄存器的8~10位:

2、先比较抢占优先级,如果相同,后比较响应优先级(抢占>响应);

3、抢占优先级高的,可以打断抢占优先级低的(正在进行的也可以);

4、响应优先级高的,不可以打断响应优先级低的(达咩);

5、只有同时产生中断条件,且抢占优先级一样,响应优先级高的,才会先执行;

6、抢占和响应都一样的时候,看哪个中断先发生就先执行。

简而言之,抢占越大,越可以随便打断,响应在抢占之后,不能随便打断。

一定程度上,可以把抢占看成母优先级,响应看成子优先级。

特别的,一般只设置一次中断优先级分组,要不然容易错乱:

比如有A和B,分组设置为2(即为2位抢占优先级,2位响应优先级),A的SCB中IP bit为1011,B的SCB中IP bit为1001,A抢占为10,B抢占也为10,此时A、B抢占优先级一样,如果随便更改分组,比如分组3,A抢占就是101,B抢占就是100,那么B优先级就大于A了。

规定的,数值越小,优先级越高,比如优先级100>101。

中断优先级分组函数(在FWLIB的misc.c中):

NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup);void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)

{

/* Check the parameters */

assert_param(IS_NVIC_PRIORITY_GROUP(NVIC_PriorityGroup));

/* Set the PRIGROUP[10:8] bits according to NVIC_PriorityGroup value */

SCB->AIRCR = AIRCR_VECTKEY_MASK | NVIC_PriorityGroup;

}加上宏定义:

#define NVIC_PriorityGroup_0 ((uint32_t)0x700) /*!< 0 bits for pre-emption priority

4 bits for subpriority */

#define NVIC_PriorityGroup_1 ((uint32_t)0x600) /*!< 1 bits for pre-emption priority

3 bits for subpriority */

#define NVIC_PriorityGroup_2 ((uint32_t)0x500) /*!< 2 bits for pre-emption priority

2 bits for subpriority */

#define NVIC_PriorityGroup_3 ((uint32_t)0x400) /*!< 3 bits for pre-emption priority

1 bits for subpriority */

#define NVIC_PriorityGroup_4 ((uint32_t)0x300) /*!< 4 bits for pre-emption priority

0 bits for subpriority */

#define IS_NVIC_PRIORITY_GROUP(GROUP) (((GROUP) == NVIC_PriorityGroup_0) || \

((GROUP) == NVIC_PriorityGroup_1) || \

((GROUP) == NVIC_PriorityGroup_2) || \

((GROUP) == NVIC_PriorityGroup_3) || \

((GROUP) == NVIC_PriorityGroup_4))

/* Private typedef -----------------------------------------------------------*/

/* Private define ------------------------------------------------------------*/

#define AIRCR_VECTKEY_MASK ((uint32_t)0x05FA0000)NVIC中断优先级设置

分组设置好了后,开始设置单个中断的抢占优先级和响应优先级。

此处库函数版本是通过定义NVIC_Type这个结构体(在core_cm4.h中)来进行地址映射:

#define __IO volatile /*!< Defines 'read / write' permissions */

/* \brief Structure type to access the Nested Vectored Interrupt Controller (NVIC).

*/

typedef struct

{

__IO uint32_t ISER[8]; /*!< Offset: 0x000 (R/W) Interrupt Set Enable Register */

uint32_t RESERVED0[24];

__IO uint32_t ICER[8]; /*!< Offset: 0x080 (R/W) Interrupt Clear Enable Register */

uint32_t RSERVED1[24];

__IO uint32_t ISPR[8]; /*!< Offset: 0x100 (R/W) Interrupt Set Pending Register */

uint32_t RESERVED2[24];

__IO uint32_t ICPR[8]; /*!< Offset: 0x180 (R/W) Interrupt Clear Pending Register */

uint32_t RESERVED3[24];

__IO uint32_t IABR[8]; /*!< Offset: 0x200 (R/W) Interrupt Active bit Register */

uint32_t RESERVED4[56];

__IO uint8_t IP[240]; /*!< Offset: 0x300 (R/W) Interrupt Priority Register (8Bit wide) */

uint32_t RESERVED5[644];

__O uint32_t STIR; /*!< Offset: 0xE00 ( /W) Software Trigger Interrupt Register */

} NVIC_Type;

RESERVE就是保留的,没用到的中断,其他ISER、ICER什么的就是对可以用的中断进行调教。

下面分析除了RESERVE的其他结构体变量成员含义:

注意下面的IP[240]:

前面说到了:

CM4内核支持256个中断,包括16个内核中断和240个外部中断,并且具有256级的可编程中断设置。

此240即彼240也。

又:

探索者板使用的是40xx、41xx,有10内核中断和82个外部中断(全是可屏蔽中断),我们用的就是82个可屏蔽中断。

我们只能使用IP[0]~IP[81]了。

然后用NVIC_Init函数进行设置(也在misc.c里面):

void NVIC_Init(NVIC_InitTypeDef* NVIC_InitStruct)

{

uint8_t tmppriority = 0x00, tmppre = 0x00, tmpsub = 0x0F;

/* Check the parameters */

assert_param(IS_FUNCTIONAL_STATE(NVIC_InitStruct->NVIC_IRQChannelCmd));

assert_param(IS_NVIC_PREEMPTION_PRIORITY(NVIC_InitStruct->NVIC_IRQChannelPreemptionPriority));

assert_param(IS_NVIC_SUB_PRIORITY(NVIC_InitStruct->NVIC_IRQChannelSubPriority));

if (NVIC_InitStruct->NVIC_IRQChannelCmd != DISABLE)

{

/* Compute the Corresponding IRQ Priority --------------------------------*/

tmppriority = (0x700 - ((SCB->AIRCR) & (uint32_t)0x700))>> 0x08;

tmppre = (0x4 - tmppriority);

tmpsub = tmpsub >> tmppriority;

tmppriority = NVIC_InitStruct->NVIC_IRQChannelPreemptionPriority << tmppre;

tmppriority |= (uint8_t)(NVIC_InitStruct->NVIC_IRQChannelSubPriority & tmpsub);

tmppriority = tmppriority << 0x04;

NVIC->IP[NVIC_InitStruct->NVIC_IRQChannel] = tmppriority;

/* Enable the Selected IRQ Channels --------------------------------------*/

NVIC->ISER[NVIC_InitStruct->NVIC_IRQChannel >> 0x05] =

(uint32_t)0x01 << (NVIC_InitStruct->NVIC_IRQChannel & (uint8_t)0x1F);

}

else

{

/* Disable the Selected IRQ Channels -------------------------------------*/

NVIC->ICER[NVIC_InitStruct->NVIC_IRQChannel >> 0x05] =

(uint32_t)0x01 << (NVIC_InitStruct->NVIC_IRQChannel & (uint8_t)0x1F);

}

}

入口的结构体定义:

typedef struct

{

uint8_t NVIC_IRQChannel; /*!< Specifies the IRQ channel to be enabled or disabled.

This parameter can be an enumerator of @ref IRQn_Type

enumeration (For the complete STM32 Devices IRQ Channels

list, please refer to stm32f4xx.h file) */

uint8_t NVIC_IRQChannelPreemptionPriority; /*!< Specifies the pre-emption priority for the IRQ channel

specified in NVIC_IRQChannel. This parameter can be a value

between 0 and 15 as described in the table @ref MISC_NVIC_Priority_Table

A lower priority value indicates a higher priority */

uint8_t NVIC_IRQChannelSubPriority; /*!< Specifies the subpriority level for the IRQ channel specified

in NVIC_IRQChannel. This parameter can be a value

between 0 and 15 as described in the table @ref MISC_NVIC_Priority_Table

A lower priority value indicates a higher priority */

FunctionalState NVIC_IRQChannelCmd; /*!< Specifies whether the IRQ channel defined in NVIC_IRQChannel

will be enabled or disabled.

This parameter can be set either to ENABLE or DISABLE */

} NVIC_InitTypeDef;

NVIC_IRQChannel:设置具体哪一个中断;

NVIC_IRQChannelPreemptionPriority:设置抢占优先级;

NVIC_IRQChannelSubPriority:设置响应优先级;

FunctionalState NVIC_IRQChannelCmd:使能这个中断,宏定义如下:

typedef enum {DISABLE = 0, ENABLE = !DISABLE} FunctionalState;现在从头开始看,ISER[8],中断使能寄存器组:

作用:使能中断。

大小:32位寄存器,每位控制一个中断的使能,一个82个外部中断,所以要使用ISER[0]~ISER[2]。

ISER[0]的bit0~bit31分别对应中断0~31;

ISER[1]的bit0~27对应中断32~63;

ISER[2]的bit0~17对应中断64~81。

然后是ICER[8]:

作用:失能中断。

大小和ISER一样,用法相反。

接着是ISPR[8]:

作用:挂起中断

最后是ICPR[8]:

作用:解挂中断

这些寄存器通过这几个函数设置:

static __INLINE void NVIC_SetPendingIRQ(IRQn_TypeIRQn);

static __INLINE uint32_t NVIC_GetPendingIRQ(IRQn_TypeIRQn);

static __INLINE void NVIC_ClearPendingIRQ(IRQn_TypeIRQn)

都在core_cm4.h中。

__STATIC_INLINE void NVIC_ClearPendingIRQ(IRQn_Type IRQn)

{

NVIC->ICPR[((uint32_t)(IRQn) >> 5)] = (1 << ((uint32_t)(IRQn) & 0x1F)); /* Clear pending interrupt */

}

__STATIC_INLINE uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn)

{

return((uint32_t) ((NVIC->ISPR[(uint32_t)(IRQn) >> 5] & (1 << ((uint32_t)(IRQn) & 0x1F)))?1:0)); /* Return 1 if pending else 0 */

}

__STATIC_INLINE void NVIC_ClearPendingIRQ(IRQn_Type IRQn)

{

NVIC->ICPR[((uint32_t)(IRQn) >> 5)] = (1 << ((uint32_t)(IRQn) & 0x1F)); /* Clear pending interrupt */

}

关于IRQN_Type(可不看):

typedef enum IRQn

{

/****** Cortex-M4 Processor Exceptions Numbers ****************************************************************/

NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */

MemoryManagement_IRQn = -12, /*!< 4 Cortex-M4 Memory Management Interrupt */

BusFault_IRQn = -11, /*!< 5 Cortex-M4 Bus Fault Interrupt */

UsageFault_IRQn = -10, /*!< 6 Cortex-M4 Usage Fault Interrupt */

SVCall_IRQn = -5, /*!< 11 Cortex-M4 SV Call Interrupt */

DebugMonitor_IRQn = -4, /*!< 12 Cortex-M4 Debug Monitor Interrupt */

PendSV_IRQn = -2, /*!< 14 Cortex-M4 Pend SV Interrupt */

SysTick_IRQn = -1, /*!< 15 Cortex-M4 System Tick Interrupt */

/****** STM32 specific Interrupt Numbers **********************************************************************/

WWDG_IRQn = 0, /*!< Window WatchDog Interrupt */

PVD_IRQn = 1, /*!< PVD through EXTI Line detection Interrupt */

TAMP_STAMP_IRQn = 2, /*!< Tamper and TimeStamp interrupts through the EXTI line */

RTC_WKUP_IRQn = 3, /*!< RTC Wakeup interrupt through the EXTI line */

FLASH_IRQn = 4, /*!< FLASH global Interrupt */

RCC_IRQn = 5, /*!< RCC global Interrupt */

EXTI0_IRQn = 6, /*!< EXTI Line0 Interrupt */

EXTI1_IRQn = 7, /*!< EXTI Line1 Interrupt */

EXTI2_IRQn = 8, /*!< EXTI Line2 Interrupt */

EXTI3_IRQn = 9, /*!< EXTI Line3 Interrupt */

EXTI4_IRQn = 10, /*!< EXTI Line4 Interrupt */

DMA1_Stream0_IRQn = 11, /*!< DMA1 Stream 0 global Interrupt */

DMA1_Stream1_IRQn = 12, /*!< DMA1 Stream 1 global Interrupt */

DMA1_Stream2_IRQn = 13, /*!< DMA1 Stream 2 global Interrupt */

DMA1_Stream3_IRQn = 14, /*!< DMA1 Stream 3 global Interrupt */

DMA1_Stream4_IRQn = 15, /*!< DMA1 Stream 4 global Interrupt */

DMA1_Stream5_IRQn = 16, /*!< DMA1 Stream 5 global Interrupt */

DMA1_Stream6_IRQn = 17, /*!< DMA1 Stream 6 global Interrupt */

ADC_IRQn = 18, /*!< ADC1, ADC2 and ADC3 global Interrupts */

#if defined (STM32F40_41xxx)

CAN1_TX_IRQn = 19, /*!< CAN1 TX Interrupt */

CAN1_RX0_IRQn = 20, /*!< CAN1 RX0 Interrupt */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */

TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */

TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */

OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */

TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global interrupt */

TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global interrupt */

TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */

FSMC_IRQn = 48, /*!< FSMC global Interrupt */

SDIO_IRQn = 49, /*!< SDIO global Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

UART4_IRQn = 52, /*!< UART4 global Interrupt */

UART5_IRQn = 53, /*!< UART5 global Interrupt */

TIM6_DAC_IRQn = 54, /*!< TIM6 global and DAC1&2 underrun error interrupts */

TIM7_IRQn = 55, /*!< TIM7 global interrupt */

DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */

DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */

DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */

DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */

DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */

ETH_IRQn = 61, /*!< Ethernet global Interrupt */

ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */

CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */

CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */

CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */

CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */

OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */

DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */

DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */

DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */

USART6_IRQn = 71, /*!< USART6 global interrupt */

I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */

I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */

OTG_HS_EP1_OUT_IRQn = 74, /*!< USB OTG HS End Point 1 Out global interrupt */

OTG_HS_EP1_IN_IRQn = 75, /*!< USB OTG HS End Point 1 In global interrupt */

OTG_HS_WKUP_IRQn = 76, /*!< USB OTG HS Wakeup through EXTI interrupt */

OTG_HS_IRQn = 77, /*!< USB OTG HS global interrupt */

DCMI_IRQn = 78, /*!< DCMI global interrupt */

CRYP_IRQn = 79, /*!< CRYP crypto global interrupt */

HASH_RNG_IRQn = 80, /*!< Hash and Rng global interrupt */

FPU_IRQn = 81 /*!< FPU global interrupt */

#endif /* STM32F40_41xxx */

#if defined (STM32F427_437xx)

CAN1_TX_IRQn = 19, /*!< CAN1 TX Interrupt */

CAN1_RX0_IRQn = 20, /*!< CAN1 RX0 Interrupt */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */

TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */

TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */

OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */

TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global interrupt */

TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global interrupt */

TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */

FMC_IRQn = 48, /*!< FMC global Interrupt */

SDIO_IRQn = 49, /*!< SDIO global Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

UART4_IRQn = 52, /*!< UART4 global Interrupt */

UART5_IRQn = 53, /*!< UART5 global Interrupt */

TIM6_DAC_IRQn = 54, /*!< TIM6 global and DAC1&2 underrun error interrupts */

TIM7_IRQn = 55, /*!< TIM7 global interrupt */

DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */

DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */

DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */

DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */

DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */

ETH_IRQn = 61, /*!< Ethernet global Interrupt */

ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */

CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */

CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */

CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */

CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */

OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */

DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */

DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */

DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */

USART6_IRQn = 71, /*!< USART6 global interrupt */

I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */

I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */

OTG_HS_EP1_OUT_IRQn = 74, /*!< USB OTG HS End Point 1 Out global interrupt */

OTG_HS_EP1_IN_IRQn = 75, /*!< USB OTG HS End Point 1 In global interrupt */

OTG_HS_WKUP_IRQn = 76, /*!< USB OTG HS Wakeup through EXTI interrupt */

OTG_HS_IRQn = 77, /*!< USB OTG HS global interrupt */

DCMI_IRQn = 78, /*!< DCMI global interrupt */

CRYP_IRQn = 79, /*!< CRYP crypto global interrupt */

HASH_RNG_IRQn = 80, /*!< Hash and Rng global interrupt */

FPU_IRQn = 81, /*!< FPU global interrupt */

UART7_IRQn = 82, /*!< UART7 global interrupt */

UART8_IRQn = 83, /*!< UART8 global interrupt */

SPI4_IRQn = 84, /*!< SPI4 global Interrupt */

SPI5_IRQn = 85, /*!< SPI5 global Interrupt */

SPI6_IRQn = 86, /*!< SPI6 global Interrupt */

SAI1_IRQn = 87, /*!< SAI1 global Interrupt */

DMA2D_IRQn = 90 /*!< DMA2D global Interrupt */

#endif /* STM32F427_437xx */

#if defined (STM32F429_439xx)

CAN1_TX_IRQn = 19, /*!< CAN1 TX Interrupt */

CAN1_RX0_IRQn = 20, /*!< CAN1 RX0 Interrupt */

CAN1_RX1_IRQn = 21, /*!< CAN1 RX1 Interrupt */

CAN1_SCE_IRQn = 22, /*!< CAN1 SCE Interrupt */

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */

TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */

TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

USART3_IRQn = 39, /*!< USART3 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */

OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */

TIM8_BRK_TIM12_IRQn = 43, /*!< TIM8 Break Interrupt and TIM12 global interrupt */

TIM8_UP_TIM13_IRQn = 44, /*!< TIM8 Update Interrupt and TIM13 global interrupt */

TIM8_TRG_COM_TIM14_IRQn = 45, /*!< TIM8 Trigger and Commutation Interrupt and TIM14 global interrupt */

TIM8_CC_IRQn = 46, /*!< TIM8 Capture Compare Interrupt */

DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */

FMC_IRQn = 48, /*!< FMC global Interrupt */

SDIO_IRQn = 49, /*!< SDIO global Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

UART4_IRQn = 52, /*!< UART4 global Interrupt */

UART5_IRQn = 53, /*!< UART5 global Interrupt */

TIM6_DAC_IRQn = 54, /*!< TIM6 global and DAC1&2 underrun error interrupts */

TIM7_IRQn = 55, /*!< TIM7 global interrupt */

DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */

DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */

DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */

DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */

DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */

ETH_IRQn = 61, /*!< Ethernet global Interrupt */

ETH_WKUP_IRQn = 62, /*!< Ethernet Wakeup through EXTI line Interrupt */

CAN2_TX_IRQn = 63, /*!< CAN2 TX Interrupt */

CAN2_RX0_IRQn = 64, /*!< CAN2 RX0 Interrupt */

CAN2_RX1_IRQn = 65, /*!< CAN2 RX1 Interrupt */

CAN2_SCE_IRQn = 66, /*!< CAN2 SCE Interrupt */

OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */

DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */

DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */

DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */

USART6_IRQn = 71, /*!< USART6 global interrupt */

I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */

I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */

OTG_HS_EP1_OUT_IRQn = 74, /*!< USB OTG HS End Point 1 Out global interrupt */

OTG_HS_EP1_IN_IRQn = 75, /*!< USB OTG HS End Point 1 In global interrupt */

OTG_HS_WKUP_IRQn = 76, /*!< USB OTG HS Wakeup through EXTI interrupt */

OTG_HS_IRQn = 77, /*!< USB OTG HS global interrupt */

DCMI_IRQn = 78, /*!< DCMI global interrupt */

CRYP_IRQn = 79, /*!< CRYP crypto global interrupt */

HASH_RNG_IRQn = 80, /*!< Hash and Rng global interrupt */

FPU_IRQn = 81, /*!< FPU global interrupt */

UART7_IRQn = 82, /*!< UART7 global interrupt */

UART8_IRQn = 83, /*!< UART8 global interrupt */

SPI4_IRQn = 84, /*!< SPI4 global Interrupt */

SPI5_IRQn = 85, /*!< SPI5 global Interrupt */

SPI6_IRQn = 86, /*!< SPI6 global Interrupt */

SAI1_IRQn = 87, /*!< SAI1 global Interrupt */

LTDC_IRQn = 88, /*!< LTDC global Interrupt */

LTDC_ER_IRQn = 89, /*!< LTDC Error global Interrupt */

DMA2D_IRQn = 90 /*!< DMA2D global Interrupt */

#endif /* STM32F429_439xx */

#if defined (STM32F401xx) || defined (STM32F411xE)

EXTI9_5_IRQn = 23, /*!< External Line[9:5] Interrupts */

TIM1_BRK_TIM9_IRQn = 24, /*!< TIM1 Break interrupt and TIM9 global interrupt */

TIM1_UP_TIM10_IRQn = 25, /*!< TIM1 Update Interrupt and TIM10 global interrupt */

TIM1_TRG_COM_TIM11_IRQn = 26, /*!< TIM1 Trigger and Commutation Interrupt and TIM11 global interrupt */

TIM1_CC_IRQn = 27, /*!< TIM1 Capture Compare Interrupt */

TIM2_IRQn = 28, /*!< TIM2 global Interrupt */

TIM3_IRQn = 29, /*!< TIM3 global Interrupt */

TIM4_IRQn = 30, /*!< TIM4 global Interrupt */

I2C1_EV_IRQn = 31, /*!< I2C1 Event Interrupt */

I2C1_ER_IRQn = 32, /*!< I2C1 Error Interrupt */

I2C2_EV_IRQn = 33, /*!< I2C2 Event Interrupt */

I2C2_ER_IRQn = 34, /*!< I2C2 Error Interrupt */

SPI1_IRQn = 35, /*!< SPI1 global Interrupt */

SPI2_IRQn = 36, /*!< SPI2 global Interrupt */

USART1_IRQn = 37, /*!< USART1 global Interrupt */

USART2_IRQn = 38, /*!< USART2 global Interrupt */

EXTI15_10_IRQn = 40, /*!< External Line[15:10] Interrupts */

RTC_Alarm_IRQn = 41, /*!< RTC Alarm (A and B) through EXTI Line Interrupt */

OTG_FS_WKUP_IRQn = 42, /*!< USB OTG FS Wakeup through EXTI line interrupt */

DMA1_Stream7_IRQn = 47, /*!< DMA1 Stream7 Interrupt */

SDIO_IRQn = 49, /*!< SDIO global Interrupt */

TIM5_IRQn = 50, /*!< TIM5 global Interrupt */

SPI3_IRQn = 51, /*!< SPI3 global Interrupt */

DMA2_Stream0_IRQn = 56, /*!< DMA2 Stream 0 global Interrupt */

DMA2_Stream1_IRQn = 57, /*!< DMA2 Stream 1 global Interrupt */

DMA2_Stream2_IRQn = 58, /*!< DMA2 Stream 2 global Interrupt */

DMA2_Stream3_IRQn = 59, /*!< DMA2 Stream 3 global Interrupt */

DMA2_Stream4_IRQn = 60, /*!< DMA2 Stream 4 global Interrupt */

OTG_FS_IRQn = 67, /*!< USB OTG FS global Interrupt */

DMA2_Stream5_IRQn = 68, /*!< DMA2 Stream 5 global interrupt */

DMA2_Stream6_IRQn = 69, /*!< DMA2 Stream 6 global interrupt */

DMA2_Stream7_IRQn = 70, /*!< DMA2 Stream 7 global interrupt */

USART6_IRQn = 71, /*!< USART6 global interrupt */

I2C3_EV_IRQn = 72, /*!< I2C3 event interrupt */

I2C3_ER_IRQn = 73, /*!< I2C3 error interrupt */

FPU_IRQn = 81, /*!< FPU global interrupt */

#if defined (STM32F401xx)

SPI4_IRQn = 84 /*!< SPI4 global Interrupt */

#endif /* STM32F411xE */

#if defined (STM32F411xE)

SPI4_IRQn = 84, /*!< SPI4 global Interrupt */

SPI5_IRQn = 85 /*!< SPI5 global Interrupt */

#endif /* STM32F411xE */

#endif /* STM32F401xx || STM32F411xE */

} IRQn_Type;

最后还有一个IABR[8]:

作用:只读,通过它可以知道当前在执行的中断是哪一个,如果对应位为1,说明该中断正在执行。

调用函数:

static __INLINE uint32_t NVIC_GetActive(IRQn_TypeIRQn);

__STATIC_INLINE uint32_t NVIC_GetActive(IRQn_Type IRQn)

{

return((uint32_t)((NVIC->IABR[(uint32_t)(IRQn) >> 5] & (1 << ((uint32_t)(IRQn) & 0x1F)))?1:0)); /* Return 1 if active else 0 */

}

NVIC初始化示例:

NVIC_InitTypeDef NVIC_InitStructure;

NVIC_InitStructure.NVIC_IRQChannel = USART1_IRQn;//串口1中断

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=1 ;// 抢占优先级为1

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 2;// 子优先级位2

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;//IRQ通道使能

NVIC_Init(&NVIC_InitStructure); //根据上面指定的参数初始化NVIC寄存器中断优先级设置步骤(总结):

1、系统运行后先设置中断优先级分组,调用:

NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup);

(系统执行中,只设置一次分组即可)

2、针对每个中断,设置对应的抢占优先级和响应优先级,调用:

NVIC_Init(&NVIC_InitStructure);

3、如果需要挂起/解挂,查看中断当前激活状态,分别调用相关函数即可。

Fin.

边栏推荐

猜你喜欢

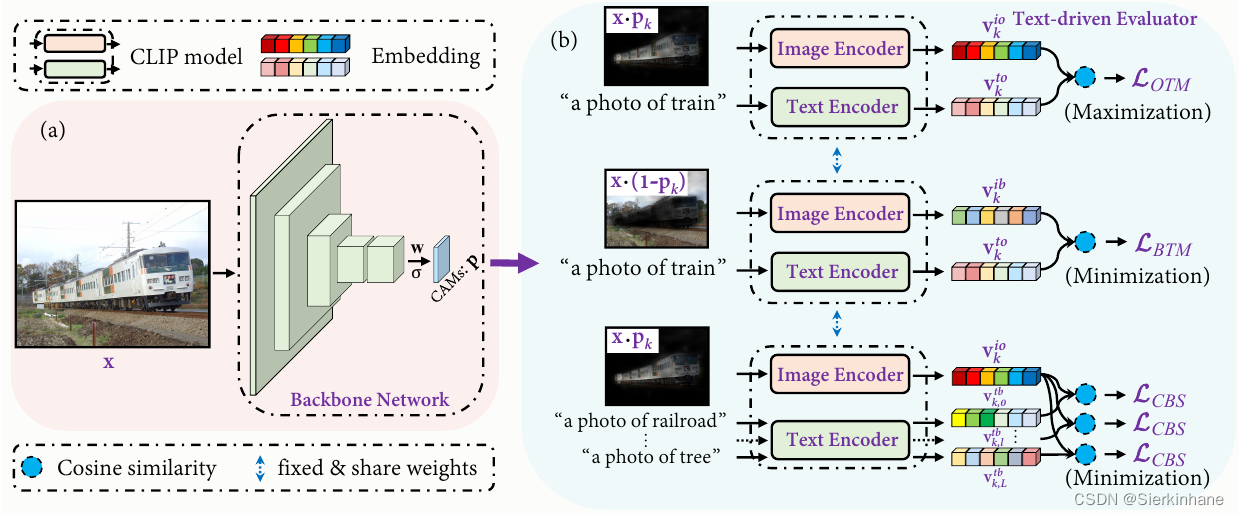

目标检测——Faster R-CNN 之 Fast R-CNN

Pay “Attention” to Adverse Weather

梅科尔工作室-华为云ModelArts第二次培训

Reconstruction and Synthesis of Lidar Point Clouds of Spray

CVPR2022——Not All Points Are Equal : IA-SSD

Maykle Studio - HarmonyOS Application Development First Training

基于AI智能图像识别:4个不同的行业应用

【调试记录1】提高MC3172浮点运算能力,IQmath库的获取与导入使用教程

弱监督语义分割CLIMS(CVPR2022)

Hard hat recognition algorithm

随机推荐

aPaaS和iPaaS的区别

Node-3.构建Web应用(一)

产品如何拟定优化方案?

Robust 3D Object Detection in Cold Weather Conditions

weex入门踩坑

微文案也能提升用户体验

梅科尔工作室-Pr第一次培训笔记(安装及项目创建)

CMT2380F32模块开发5-CLK例程

Node-3.构建Web应用(二)

Mei cole studios - fifth training DjangoWeb application framework + MySQL database

ActiveReports报表分类之页面报表

The selection points you need to know about the helmet identification system

OpenPCDet安装最新版:spconv一步到位

安全帽识别

CMT2380F32模块开发2-IDE软件配置

小程序技术原理分析

红外线一认识

Realize data exchange between kernel and userspace through character device virtual file system (passed based on kernel 5.8 test)

Mei cole studios - deep learning second BP neural network

Introduction of safety helmet wearing recognition system