当前位置:网站首页>FPGA工程师面试试题集锦101~110

FPGA工程师面试试题集锦101~110

2022-08-10 18:14:00 【fpga和matlab】

101. 用Altera_Cpld作了一个186(主CPU)控制sdram的控制接口, 发现问题:要使得sdram读写正确, 必须把186(主CPU)的clk送给sdram, 而不能把clk经cpld的延时送给sdram. 两者相差仅仅4ns. 而时序通过逻辑分析仪测试没有问题. 此程序在xilinx器件上没有问题. 这是怎么回事?

答:建议将所有控制和时钟信号都从PLD输出, 因为SDRAM对时钟偏移(clock skew)很敏感, 而Altera的器件PLL允许对时钟频率和相位都进行完全控制. 因此, 对于所有使用SDRAM的设计, Altera的器件PLL必须生成SDRAM时钟信号.

要利用SDRAM作为数据或程序存储地址来完成设计, 是采用MegaWizard还是Plug-In Manager来将一个PLL在采用Quartus II软件的设计中的顶层示例?可以选择创建一个新的megafuntion变量, 然后在Plug-In manager中创建ALTCLKLOCK(I/P菜单)变量. 可以将PLL设置成多个, 或是将输入划分开来, 以适应设计需求. 一旦软件生成PLL, 将其在设计中示例, 并使用PLL的“Clock”输出以驱动CPU时钟输入和输出IP引脚.

102.在max7000系列中, 只允许有两个输出使能信号, 可在设计中却存在三个, 每次编译时出现“device need too many [3/2] output enable signal”. 如果不更换器件(使用的是max7064lc68). 如何解决这个问题?

答:Each of these unique output enables may control a large number of tri-stated signals. For example, you may have 16 bidirectional I/O pins. Each of these pins require an outpu

边栏推荐

猜你喜欢

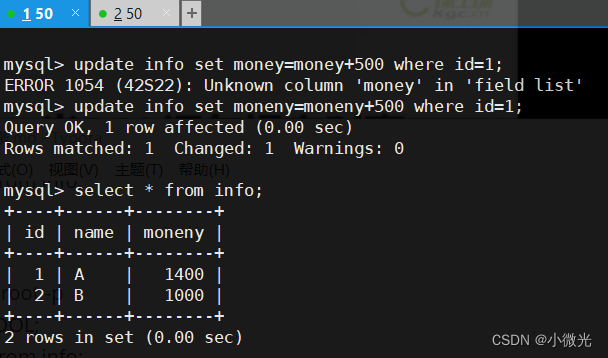

Mysql index, transaction and storage engine

Wuling Hongguang MINI EV, the only drawback is safety

入门:人脸专集2 | 人脸关键点检测汇总(文末有相关文章链接)

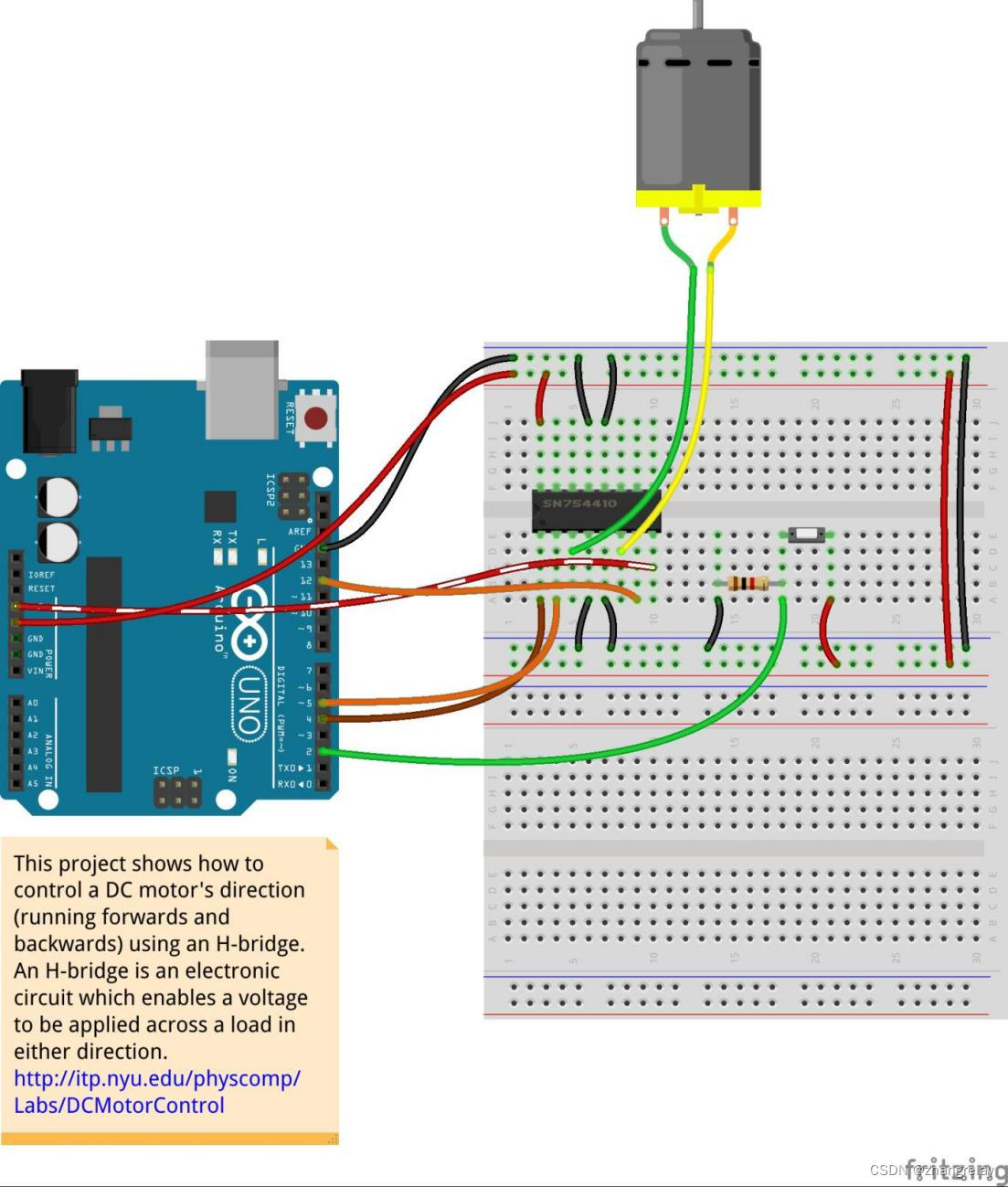

机器人控制器编程实践指导书旧版-实践三 直流电机(执行器)

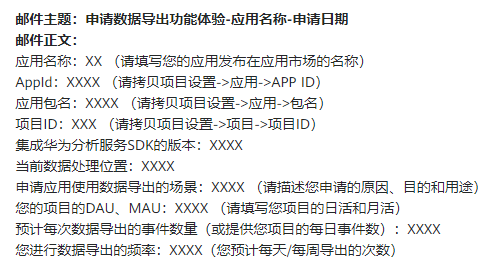

【HMS core】【FAQ】Analytics Kit、Push Kit典型问题合集3

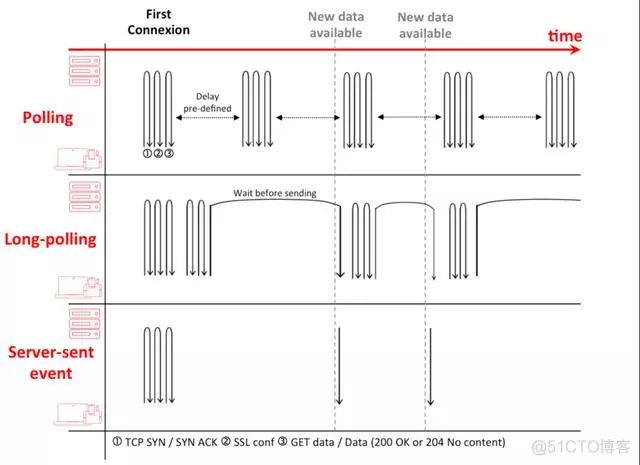

「Web应用架构」轮询,SSE 和WebSocket,如何选择合适的?

【深度学习21天学习挑战赛】4、初尝循环神经网络(RNN)——股票预测

Toronto Research Chemicals农药检测丨Naled-d6

兼具外观、性能、屏幕!华硕灵耀X 14火热抢购中

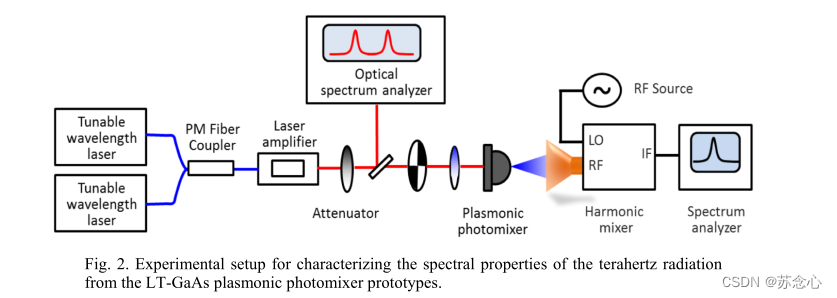

【2015】【论文笔记】等离子光混合器THz辐射的光谱——

随机推荐

Toronto Research Chemicals 对乙酰氧基苯乙酮说明书

Allegro软件Shape菜单下的每个命令的含义

120Hz OLED拒绝“烧屏”!华硕无双全能轻薄本

[Image dehazing] Image dehazing based on color attenuation prior with matlab code

Scala中使用 Jackson API 进行JSON序列化和反序列化

stm32中的CAN通讯列表模式配置解析与源码

【测试】黑盒测试用例设计方法

WebRTC源码分析 nack详解

接口测试进阶接口脚本使用—apipost(预/后执行脚本)

海思HI3516DV300开发资料

pyspark columns merge into one row

企业如何通过北森HR SaaS 自动化管理员工账号生命周期

机器人控制器编程实践指导书旧版-实践七 无线通信(网络)

机器人控制器编程实践指导书旧版-实践四 步进电机(执行器)

IoU、GIoU、DIoU、CIoU四种损失函数总结

CSV(Comma-Separate-Values)逗号分隔值文件

6-11 先序输出叶结点(15分)

面试题 04.12. 求和路径-dfs+辅助数组法

三星Galaxy Watch5产品图片流出 非Pro表款亦有蓝宝石加持

去除富文本标签样式