当前位置:网站首页>快时钟同步慢时钟域下的异步控制信号slow clk to fast clk

快时钟同步慢时钟域下的异步控制信号slow clk to fast clk

2022-04-23 17:06:00 【icgogogo】

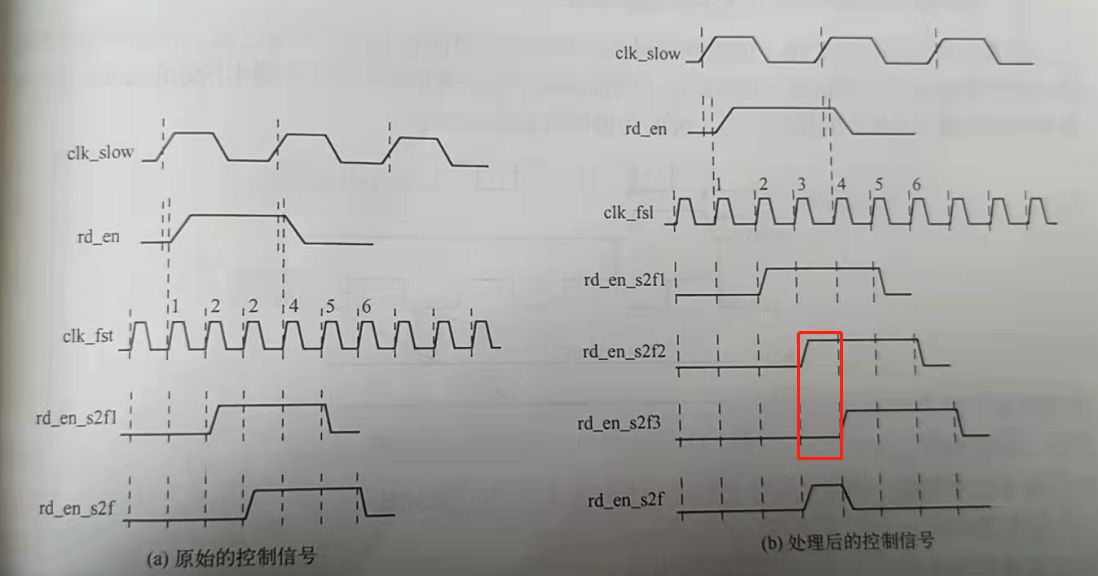

这种情况下,异步控制信号可能在己慢时钟下只维持了一个有效时钟,而在快时钟下,已经被采样了几次,一次读请求可能被误以为多次读请求。

快时钟同步慢时钟信号示意图

RTL代码

module synchronizer(

clk_fst;

rst_b;

rd_en;//原始控制信号

rd_en_s2f;//处理后的信号

);

input clk_fst;

input rst_b;

output rd_en_s2f;

wire rd_en_s2f;

reg rd_en_s2f1;

reg rd_en_s2f2;

reg rd_en_s2f3;

always@(posedge clk_fst or negedge rst_b)

if(!rst_b)begin

rd_en_s2f1 <= 1'b0;

rd_en_s2f2 <= 1'b0;

rd_en_s2f3 <= 1'b0;

end else begin//同步器

rd_en_s2f1 <= rd_en;

rd_en_s2f2 <= rd_en_s2f1;

rd_en_s2f3 <= rd_en_s2f2;

end

end

always@(rd_en_s2f3 or rd_en_s2f3)begin

case({rd_en_s2f3,rd_en_s2f2})

2'b01:

rd_en_s2f <= 1'b1;

default:

rd_en_s2f <= 1'b0;

endcase

end

endmodule版权声明

本文为[icgogogo]所创,转载请带上原文链接,感谢

https://blog.csdn.net/javagogogo2850/article/details/124360724

边栏推荐

- Shell-awk命令的使用

- Collect blog posts

- Milvus 2.0 质量保障系统详解

- 拷贝构造函数 浅拷贝与深拷贝

- Detailed explanation of information abstract, digital signature, digital certificate, symmetric encryption and asymmetric encryption

- TypeError: set_ figure_ params() got an unexpected keyword argument ‘figsize‘

- Idea of batch manufacturing test data, with source code

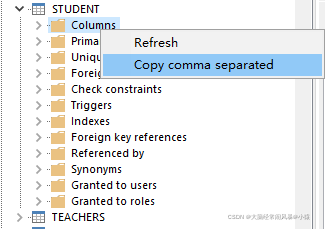

- Get the column name list of the table quickly in Oracle

- Zhimeng dedecms security setup Guide

- Signalr can actively send data from the server to the client

猜你喜欢

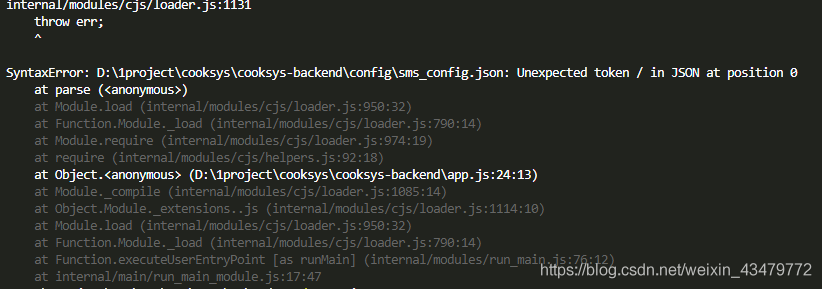

Nodejs reads the local JSON file through require. Unexpected token / in JSON at position appears

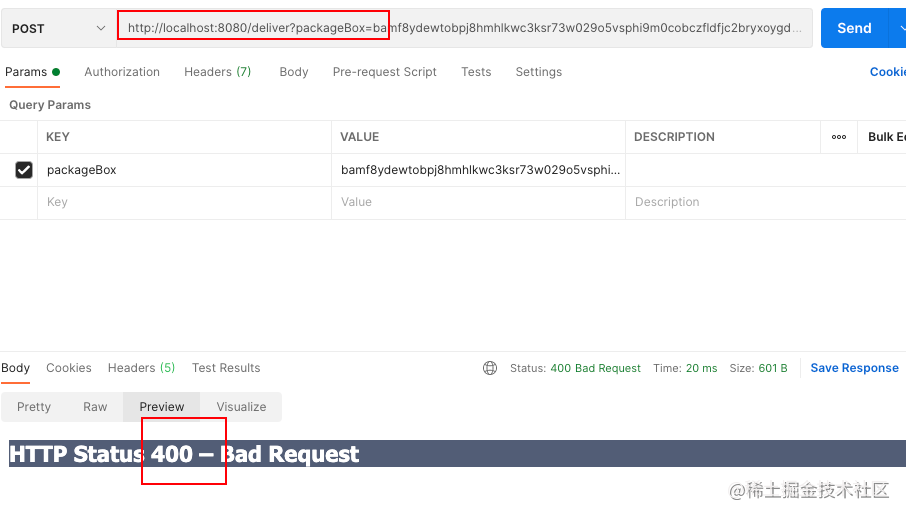

Feign report 400 processing

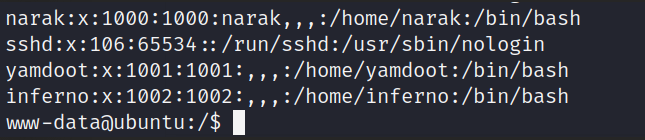

Detailed explanation of the penetration of network security in the shooting range

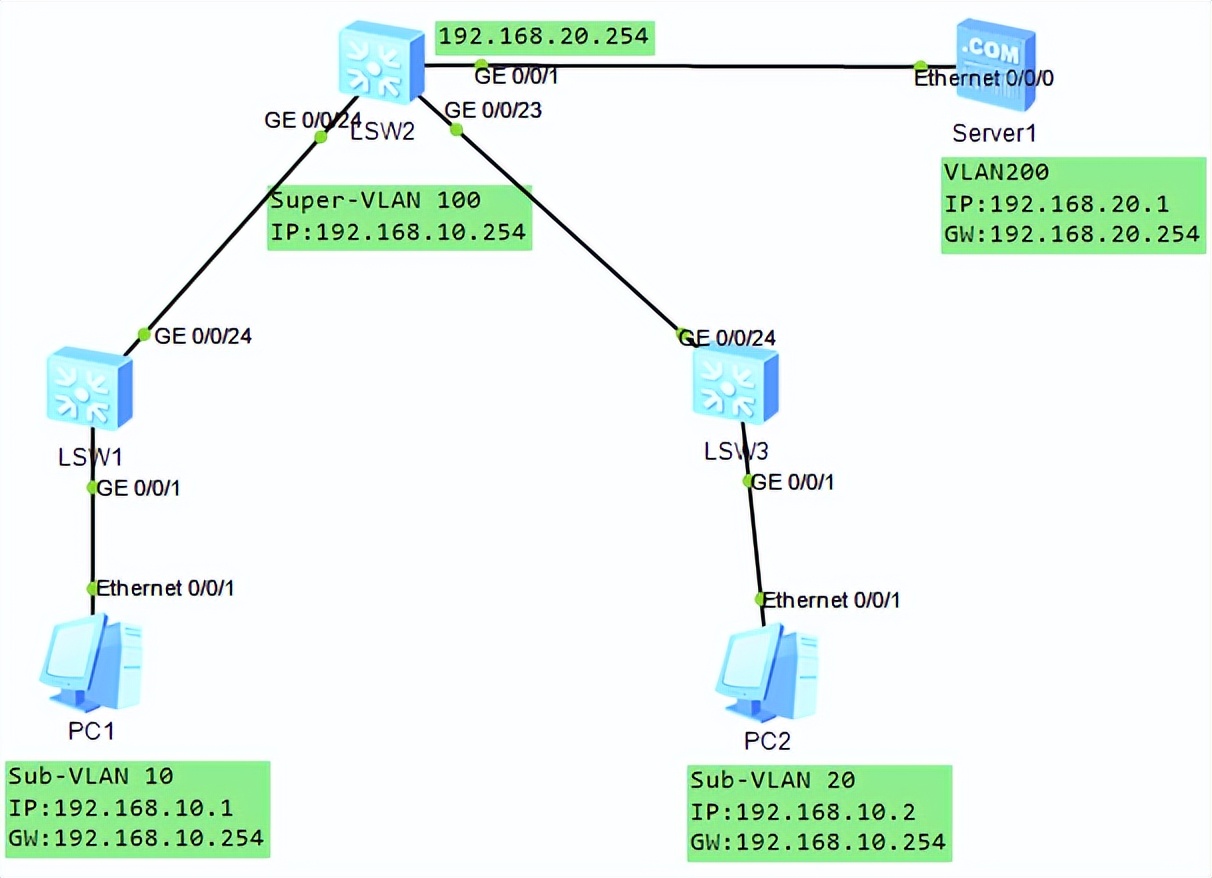

VLAN高级技术,VLAN聚合,超级Super VLAN ,Sub VLAN

Nifi fast installation and file synchronization

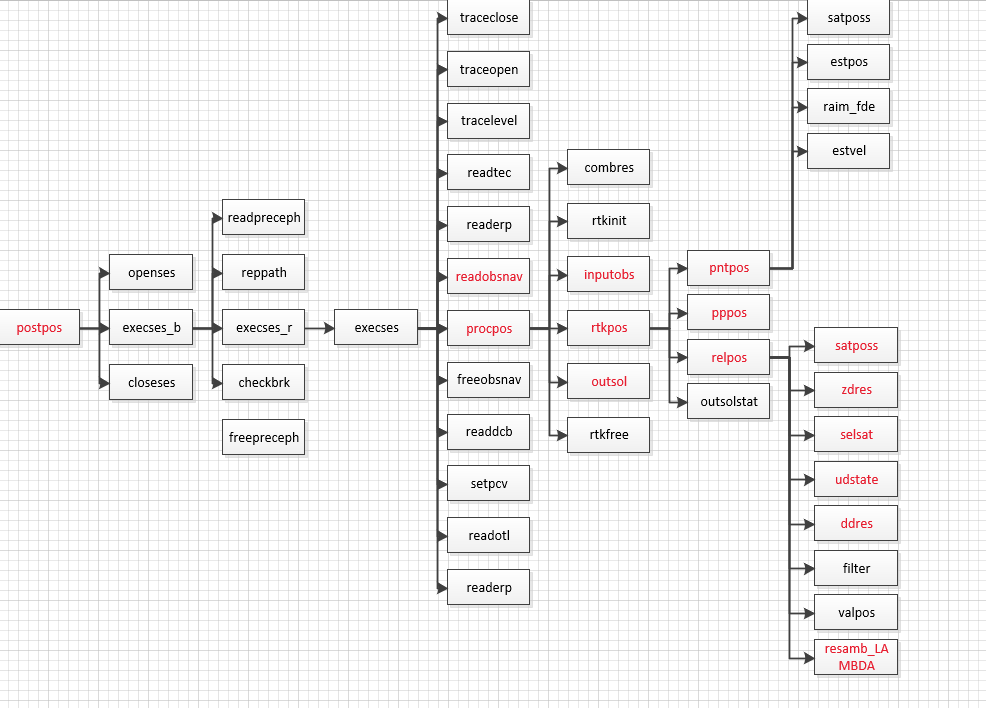

Rtklib 2.4.3 source code Notes

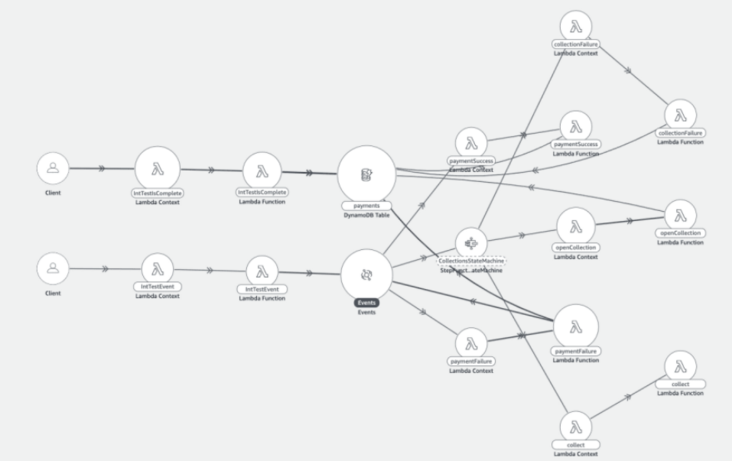

On lambda powertools typescript

Use between nodejs modules

oracle 中快速获取表的列名列表

![[pimf] openharmony paper Club - what is the experience of wandering in ACM survey](/img/b6/3df53baafb9aad3024d10cf9b56230.png)

[pimf] openharmony paper Club - what is the experience of wandering in ACM survey

随机推荐

Variable length parameter__ VA_ ARGS__ Macro definitions for and logging

Nodejs reads the local JSON file through require. Unexpected token / in JSON at position appears

C# Task. Delay and thread The difference between sleep

Shell脚本——Shell编程规范及变量

websocket

Nifi fast installation and file synchronization

Further study of data visualization

Mock test

Production environment——

Paging the list collection

1-3 components and modules

Zhongang Mining: Fluorite Flotation Process

Paging SQL

Linux MySQL data timing dump

Grpc gateway based on Ocelot

Feign report 400 processing

Solution architect's small bag - 5 types of architecture diagrams

Bottom processing of stack memory in browser

Do you really understand the principle of code scanning login?

Calculation formula related to tolerance analysis